- •Особенности схемотехники и основные параметры транзисторно-транзисторной логики.

- •Особенности схемотехники ттлш.

- •Особенности схемотехники эмиттерно-связанной логики.

- •Особенности схемотехники и основные параметры инжекционной интегральной логики.

- •Ключевые схемы на мдп (моп)-транзисторах.

- •Принципы проектирования комбинационных устройств.

- •Сумматоры и вычитающие устройства.

- •Цифровые компараторы.

- •Преобразователи кодов.

- •Кодирующие и декодирующие устройства.

- •Мультиплексоры и демультиплексоры.

- •Триггеры: общие сведения.

- •Регистры.

Особенности схемотехники и основные параметры транзисторно-транзисторной логики.

Основное отличие логических элементов ТТЛ в том, что в ТТЛ логических элементах входные диоды заменены одним многоэмиттерным транзистором (МЭТ). В первом приближении p–n переходы база–эмиттер многоэмиттерного транзистора VT1 можно считать входными диодами как у схем ДТЛ, а переход база–коллектор многоэмиттерного транзистора, – помехозащитным диодом в базе фазоразделительного каскада. Так эта схема ТТЛ и работает при уровне логической единицы на входах A, B и C. Когда же на один из входов поступает логический ноль, многоэмиттерный транзистор VT1 становится транзистором, включенным по схеме ОБ.

При таком переходе входа многоэмиттерного транзистора из логической единицы в логический ноль транзистор фазоразделительного каскада VT2 из открытого (насыщенного) состояния переходит в закрытое, при этом накопленный в базе VT2 заряд быстро рассасывается через открытый многоэмиттерный транзистор VT1, что существенно уменьшает время переключения всего ТТЛ элемента по сравнению с ДТЛ.

О собенностью

многоэмиттерного транзистора в открытом

состоянии является отсутствие прямого

взаимодействия эмиттеров между собой,

т.к. их разделяют участки базы. Можно

считать что многоэмиттерный транзистор

во включенном состоянии, – это несколько

транзисторов, имеющих общий коллектор.

собенностью

многоэмиттерного транзистора в открытом

состоянии является отсутствие прямого

взаимодействия эмиттеров между собой,

т.к. их разделяют участки базы. Можно

считать что многоэмиттерный транзистор

во включенном состоянии, – это несколько

транзисторов, имеющих общий коллектор.

Трехтранзисторный выходной инвертор ТТЛ, отличается от рассмотренного ранее при анализе ДТЛ логического элемента, введением диода VD1 в эмиттерную цепь верхнего транзистора VT4 двухтактного выходного каскада. Этот диод обеспечивает более надежное запирание транзистора VT4 при логическом нуле на входе логического элемента.

Развитие схемотехники ТТЛ вентиля (логического элемента) привело в основном к следующему:

1) введению антизвонных диодов (VD1…VD3 ) на входах схемы (ведены во все сериях ТТЛ);

2) замене эмиттерного сопротивления R3 фазоразделительного каскада на генератор тока, схема которого собрана на VT6, R4, R5 (называется иногда динамической нагрузкой), который обеспечивает быстрое рассасывание накопленных зарядов в области базы нижнего транзистора VT5 выходного двухтактного каскада при закрывании этого транзистораVT5;

3) замене выходного эмиттерного повторителя верхнего транзистора VT4 выходного двухтактного каскада на составной эмиттерный повторитель на двух транзисторах VT3 и VT4, для уменьшения выходного сопротивления в состоянии логической единицы на выходе, для выравнивания этого сопротивления с сопротивлением при логическом нуле на выходе;

4) замене всех или части транзисторов логических элементов транзисторами Шоттки для уменьшения времени их переключения.

Комбинации 2, 3 и 4 изменений, а также значения внутренних резисторов определяют различия между сериями ТТЛ, при этом изменяются быстродействие и потребляемая микросхемами мощность.

Особенности схемотехники ттлш.

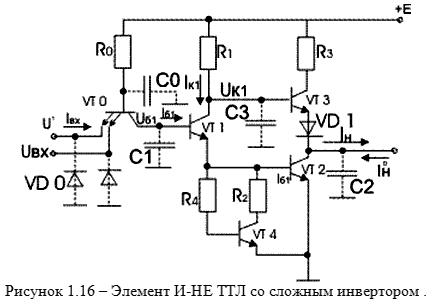

Использование диодов и транзисторов Шотки в схемах ТТЛ, повышает их быстродействие в качестве VT3 (рис.1.16) используется обычный транзистор, так как он не входит в режим насыщения. Все остальные – транзисторы Шотки. Повышение быстродействия в элементах ТШЛ обусловлено двумя причинами: не учитывается время рассасывания избыточного заряда в транзисторах Шотки, т.е. tc ≈ 0; уменьшается времена спада и нарастания tc , tн.

Недостатком элементов ТШЛ является их уменьшение по сравнению с элементами ТТЛ помехоустойчивость Un+ вследствие повышения уровня U0 и понижения порога Vn:

U0 = Uост ш = U* - U*ш

Vn = 2U* - Uост ш = U* + U*ш

Un+ = Vn – U0 = 2U*ш.

Падение напряжения на открытом диоде Шотки в современных микросхемах обычно составляет U*ш = 0,3-0,5 В.

Помехоустойчивость элементов ТШЛ составляет Un+ ≈ 0,8 В при Тn+ = + 200C и Un+ = 0,3-0,5 В при Т = + 1250С.

Применение диодов и транзисторов Шотки позволяет также существенно повысить быстродействие элементов ДТЛ со сложным инвертором. Элементы ДТШЛ используют в цифровых микросхемах с повышенным потреблением мощности. Они обеспечивают типовые значения t3 ≈10 нс при потребляемой мощности Р = 1-2 мВт.

Схемы ТШЛ и ДТШЛ являются наиболее перспективной элементной базой для цифровых микросхем среднего и высокого быстродействия, хотя их стоимость больше чем обычных ТТЛ.