- •Методичні вказівки до розрахункової роботи та курсового проекту з предмету: «мікропроцесорні системи комплексної безпеки об’єктів» вступ

- •Аналітичний огляд

- •Можливість передавати інформацію та її кількість

- •Можливість керувати іншими компонентами системи безпеки

- •Коректність даних

- •Стани star і sтор

- •Формат байта

- •Підтвердження

- •Синхронізація

- •Призначення бітів першого байта

- •Порядок проводів ліній шини

- •Вибір напряму проектування

- •Основні особливості пліс Хіlіnх:

- •2.2 Пліс типу fpga

- •Основні модулі пакета Foundation Series.

- •Конфігурації пакету

- •Будова і принцип дії

- •Програмування і керування

- •Граничні експлуатаційні характеристики

- •3.16 Буфер р82в96

- •Для проектуючої пліс маємо

Основні модулі пакета Foundation Series.

Ргоjeсt: Мanager графічний засіб керування файлами проекту і основними модулями пакету.

Synthesis Constraits Editor - редактор обмежень, що накладаються на проект написаний на VHDL /Verilog перед синтезом.

Aynthesis Timing Analyzer - аналізатор часових параметрів синтезованих проектів.

Synopsys FPGA Express Synthesis- програма синтезу проектів, написаних на VHDL\Verilog

HDL Design Toois - набір утиліт для спрощення вводу проекту на мовах високого рівня VHDL\Verilog, що містить в собі текстовий редактор, майстер готових шаблонів основних конструкцій мови, перевірку синтаксису, редактор діаграм станів.

ABEL Synthesis - модуль синтезу проектів, написаних на АbеІ.

Schematic Editor- графічний редактор, що дозволяє вводити проекти у схемному вигляді на основі бібліотек логічних елементів (прості вентилі, регістри, лічильники, елементи пам'яті і т.д.)

Simulator (Functional and Timing)- графічний редактор, що дозволяє провести моделювання до трасування і після.

Design Manager-інтерфейсний модуль, що здійснює керування всіма засобами автоматичного трасування та дає доступ користувачу до них.

Flow Engine-відображає та виконує всі етапи по розміщенню проекту в кристал, що складаються з:

- трансляції вхідного файлу універсального формату у внутрішній формат;

- розбиття логіки по КЛБ;

- розміщення по кристалу елементів логіки та зв'язків;

- створення конфігураційного файлу для завантаження у кристал;

- створення звіту про статичні часові параметри і створення файлу для моделювання з врахуванням часових затримок у форматі VHDL, Verilog, EDIF чи ХNF.

LogiBLOX - графічний засіб створення параметризованих та оптимізованих під конкретну архітектуру логічних елементів (лічильники, пам'ять, регістри, мультиплексори і т. д.)

CORE Gen вбудований модуль генерації параметризованих і оптимізованих під конкретну архітектуру модулів, що виконують складні функції, наприклад такі модулі як корелятори, фільтри, спектральні перетворення, елементарні блоки ЦOС і т.д.

Floorplanner - графічний засіб, що дозволяє контролювати процес автоматичного розміщення логіки в кристал FPGA чи повністю "вручну" провести розміщення.

FPGA Editor- графічний засіб, що дозволяє переглянути і відредагувати результати розміщення логіки та зв'язків, а також "вручну" спроектувати кристал FPGA на рівні КЛБ і ліній зв'язку.

Hardware Debugger - програма завантаження та верифікації проекту з комп'ютера.

РRОМ Files Formatter - програма створення конфігураційного файлу для зберігання у послідовних чи паралельних ПЗП. Доступними є три формати МСS, ЕХО, ТЕХ. Для мікропроцесорного завантаження формуєтся файл в форматі НЕХ.

Конфігурації пакету

Foundation Series постачається в чотирьох конфігураціях:

Ваsе (FND-ВАS)

Ваsе Ехрrеs (FND-ВSХ)

Ехрrеss (FND-ЕХР)

ЕПІе (FND-ELI)

Конфігурації відрізняються логічним об'ємом кристалів що підтримуються пакетом, модулями вводу проекту та вартістю.

Приведена вище класифікація вузлів мікропроцесорних систем відповідає структурі розроблювального пристрою, тому основною задачею при розробці буде проектування ПЛІС сімейства Virtex фірми Хіlіnх із використанням програмного забезпечення Foundation Base цієї ж фірми.

Засоби розробки топології друкованої плати

Для моделювання та розробки плати управління обрано пакет проектування друкованих плат АССЕL EDA vІ5 (подальший розвиток Р-САDу, випущений у 3 кварталі 1999р). Система АССЕL EDA поєднує кращі якості пакетів АССЕL ТаngoPRO) для Windows і Р-САD для DOS. Від ТаngoPRO запозичений редактор схем і менеджер бібліотек, від Р-САD -засоби розробки друкованих плат. АССЕL ЕDА виконує повний цикл проектування друкованих плат, що включає в себе графічне введення схем, упакування схеми на друковану плату, ручне розміщення компонентів, ручне, інтерактивне і автоматичне трасування провідників, контроль помилок в схемі і друкованій платі і підготовка документації. Застосування супутніх програм дозволяє виконувати моделювання схем і аналіз паразитних ефектів, властивим реальним друкованим платам, до їхнього виготовлення, що забезпечує перевагу АССЕL EDA у порівнянні з іншими САПР DesignLab і ОгСАD.

У порівнянні з Р-САD для DOS система АССЕL EDA для Windows має й інші переваги:

• виконання стандартних команд і організація меню в стилі Windows спрощує роботу із системою та ознайомлення з нею;

• висновок результатів проектування на периферійні пристрої (принтери, плоттери), що мають драйвери для Windows;

• застосування векторних масштабуючих шрифтів Тrue Туре дозволяє наносити на схеми і друковані плати напису по-українськи, використовуючи кириличні шрифти Windows;

• можливе завдання різних типів перехідних отворів при переході провідників із шару на шар;

• можливе автоматичне трасування однієї і тієї ж ланки сегментами різної ширини;

• удосконалений алгоритм автотрасування провідників, включаючи автоматичне трасування багатошарових друкованих плат, що мають внутрішні шари металізації;

• забезпечена координація бібліотек символів і корпусів компонентів.

Підтримка текстових форматів опису баз даних DXF, PDIF, ALT і ін. дозволяє обмінюватися інформацією з такими розповсюдженими пакетами, як AutoCAD, ОгСАD та ін.

Версії АССЕL EDA 15.0 приведений опис нових модулів цієї системи (команди документування результатів проектування Восшпепі; ТооІЬох, модуль ведення документообігу Personal PDM РОМ, програма аналізу цілісності сигналів Signal Integrity і ін.), програми моделювання Dr. Spice А/D 2000, а також останніх версій програм САМ350 5.0—6.0 і SPECCTRA.

Вибір елементної бази

Пристрій спроектований з використанням сучасної елементної бази. Яка має низьке енергоспоживання і масо-габаритні характеристики. Основою пристрою є ПЛІС фірми Xilinx Spartan2 XC2S50, конфігурація якої здійснюється за допомогою конфігураційної пам'яті тієї ж фірми, XC18V02, ємність якої 1.048.576 біт.

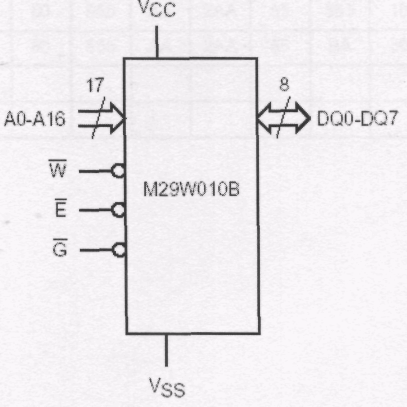

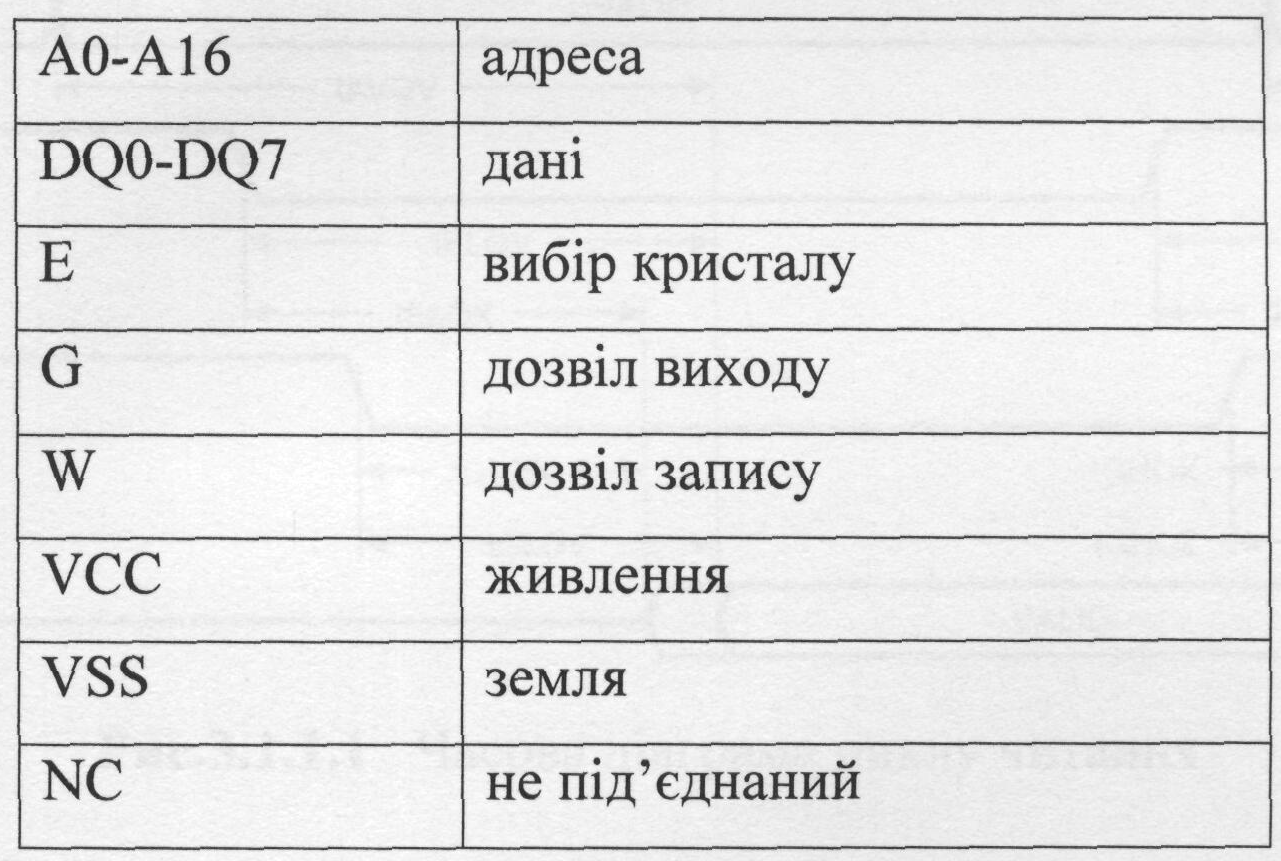

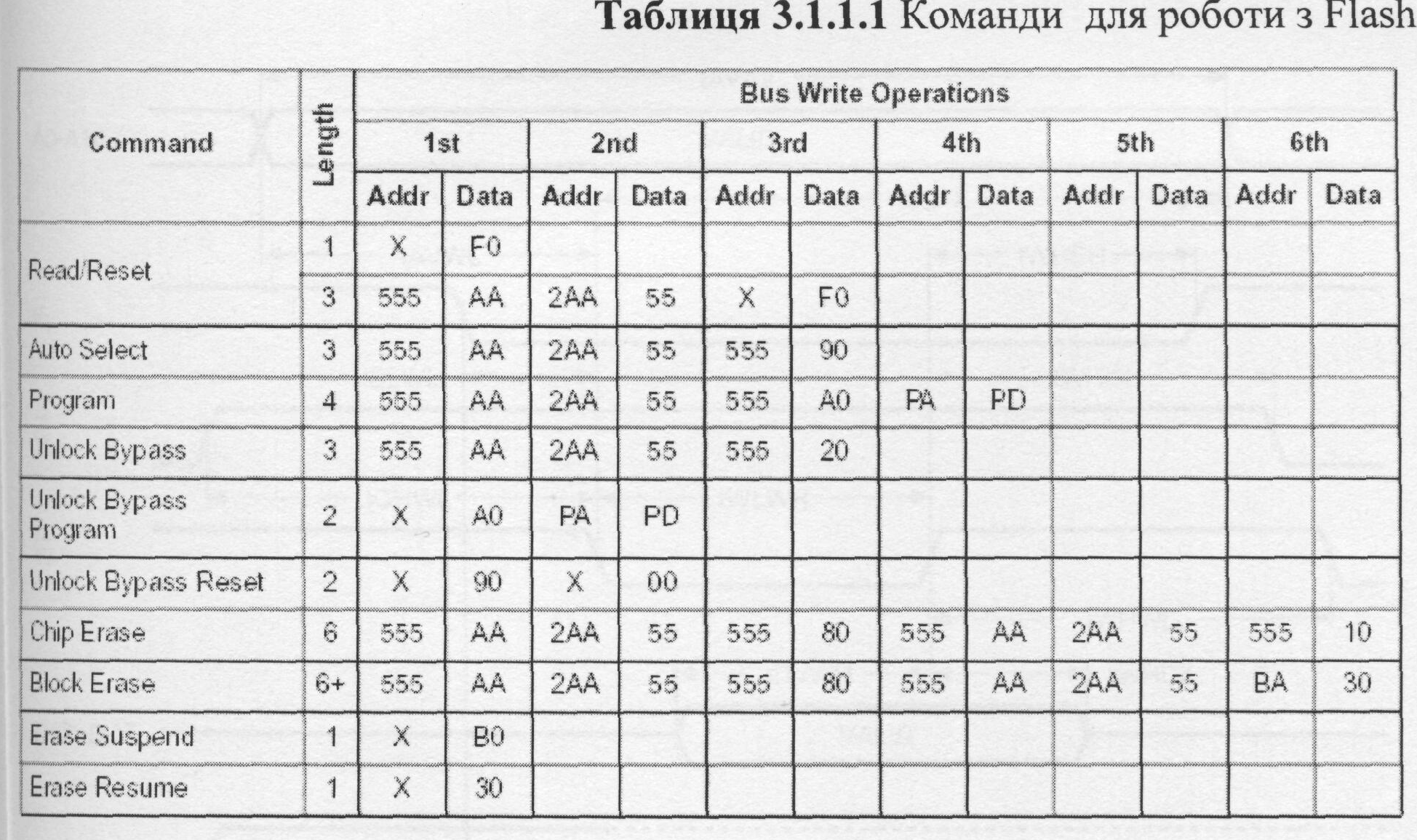

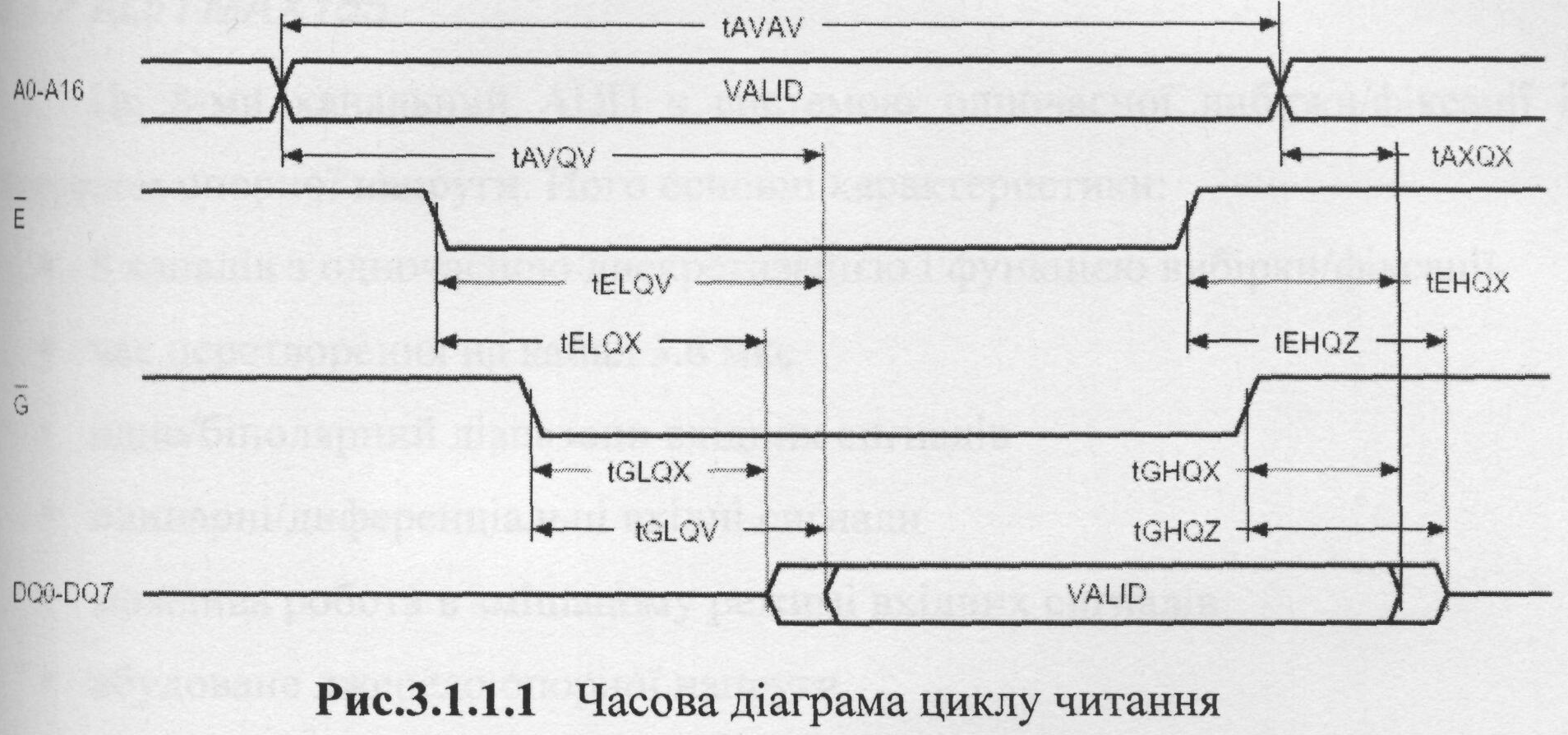

Flash пам'ять M29W010B

Це флеш-пам'ять фірми STMicroelectronics об'ємом 1Мбіт (128Кбайт х 8) вміст якої може бути прочитаний, стертий і перезаписаний. Ці операції виконуються при низькій напрузі споживання (від 2.7 до 3.6В). Після включення живлення, по замовчуванні, пам'ять встановлюється в режим читання, в якому вона працює як звичайна ROM чи EPROM. Робота з пам'яттю організовується за допомогою команд наведених в таблиці 3.1.1.1. Часові діаграми показані на рисунках 3.1.1.1 ІЗ.1.1.2.

Основні характеристики:

• напруга живлення від 2.7 до 3.6В

для всіх операцій

• час доступу 45нс

час доступу 45нс

• час запису 10 мкс

• 8 блоків розміром 16Кбайт

• режим зупинки і

відновлення процесу стирання

• режим пониженого енергоспоживання

• 100.000 циклів запису/стирання на блок

• зберігання даних 20 років

3.1.2 АЦП МАХ155

Це 8-ми канальний АЦП з системою одночасної вибірки/фіксації і джерелом опорної напруги. Його основні характеристики:

• 8 каналів з одночасною дискретизацією і функцією вибірки/фіксації

• час перетворення на канал 3.6 МКС

• одно/біполярний діапазони вхідних сигналів

• одинарні/диференціальні вхідні сигнали

• можлива робота в змішаному режимі вхідних сигналів

• вбудоване джерело опорної напруги

МАХ155 є швидкодіючим, 8-ми розрядними, багатоканальним, аналого-цифровими перетворювачем (АЦП) з системою одночасної вибірки/фіксації для виключення тимчасової неузгодженості між вхідними сигналами вибірки. Кожен з каналів має виділену систему вибірки/фіксації (Т/Н), і всі Т/Н - канали проводять вибірку сигналу в один момент часу. АЦП перетворює дані каналів за 3.6 мкс і зберігає результат у вбудованій, 8x8 RAM-пам'яті.

При роботі від однополярного джерела живлення +5В, МС здатна проводити перетворення, або з уніполярними, або з біполярними, а також, або з одиночними, або з диференціальними сигналами.

Перетворення ініціюється при надходженні імпульсу на вхід WR (активний низький рівень), а зчитування даних з RAM АЦП відбувається за імпульсом на вході RD (активний низький рівень). Двонаправленний інтерфейс обновляє конфігурацію каналів і забезпечує вивід вихідних даних.

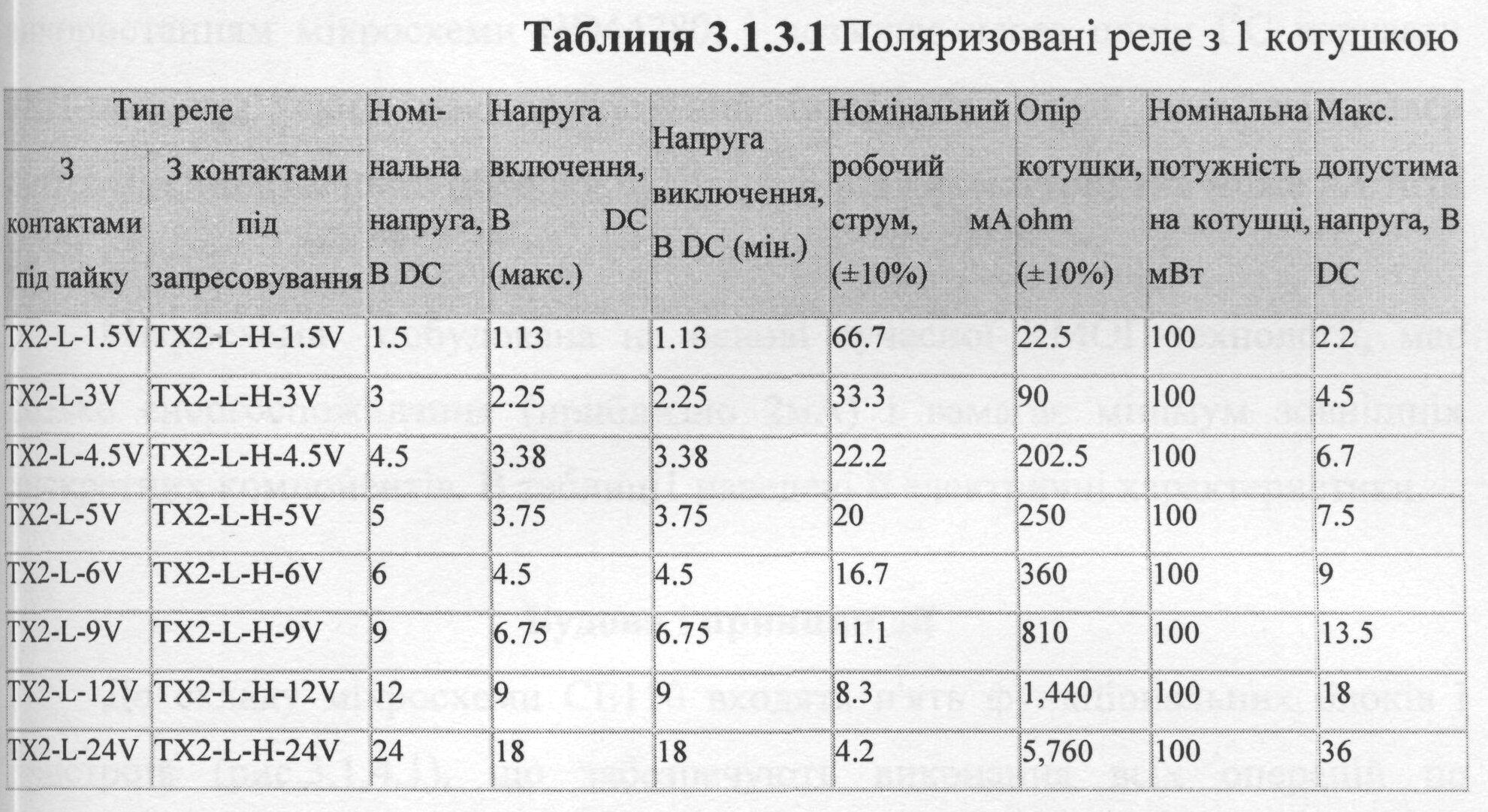

Реле ТХ2

Реле ТХ реле третього покоління, одна з найбільше широко використовуваних в даний час моделей в серійному телекомунікаційному і вимірювальному устаткуванні. Це 2-х амперне реле високої потужності з високою напругою пробою між контактами і високою напругою пробою між котушкою і контактами

Основні характеристики:

• Два перекидних контакти

• Чутливість контактів 10 мкА при 10 мВ

• Номінальне навантаження 2А 30В DC чи 0,5А 125В АС

• Максимальний комутований струм 2А, напруга 220В DC чи 230В АС

• Механічна міцність 10 мільйонів переключень, при штатному навантаженні 100 тисяч

• Реле поляризоване

• Напруга пробою між контактами 1000 В, між групами контактів 1000В, контакт-котушка 2000В, тест BellCore 2500B

• Стандартний ряд керуючих напруг: 1,5-3-5-9-12-24 VDC

• Споживання потужності котушки 140мВт (моностабільне), 100мВт (бістабильне виконання), з котушкою 24В - 270мВт відповідно

• Ступінь захисту ІР67 (газонепроникність)

• Час включення/виключення 4мс

Контролер РК-модуля і клавіатури СЕ110

Основні характеристики:

• висока

швидкість обміну по шині І2С

висока

швидкість обміну по шині І2С

• можливість підключення до 64 клавіш

• мала кількість зовнішніх компонентів

• низьке енергоспоживання

• компактний корпус з 28 контактами

Області застосування:

• мікроконтролери

• електронні пристрої

• промислове обладнання

• обладнання для телефонії

• бортова апаратура

Мікросхема призначена для побудови блоків вводу/індикації на основі широкорозповсюджених одно- і двострічкових РКД-модулів, побудованих з використанням мікросхеми HD44780, і дозволяє через шину І2С керувати РКД-модулем, який має паралельний інтерфейс. Крім того, контролер підтримує сканування і обробку інформації від клавіатури, яка може містити до 64 клавіш.

Мікросхема побудована на основі сучасної КМОП-технології, має низьке енергоспоживання (приблизно 2мА) і вимагає мінімум зовнішніх дискретних компонентів. В таблиці 1 наведені її електричні характеристики.