- •Методичні вказівки до розрахункової роботи та курсового проекту з предмету: «мікропроцесорні системи комплексної безпеки об’єктів» вступ

- •Аналітичний огляд

- •Можливість передавати інформацію та її кількість

- •Можливість керувати іншими компонентами системи безпеки

- •Коректність даних

- •Стани star і sтор

- •Формат байта

- •Підтвердження

- •Синхронізація

- •Призначення бітів першого байта

- •Порядок проводів ліній шини

- •Вибір напряму проектування

- •Основні особливості пліс Хіlіnх:

- •2.2 Пліс типу fpga

- •Основні модулі пакета Foundation Series.

- •Конфігурації пакету

- •Будова і принцип дії

- •Програмування і керування

- •Граничні експлуатаційні характеристики

- •3.16 Буфер р82в96

- •Для проектуючої пліс маємо

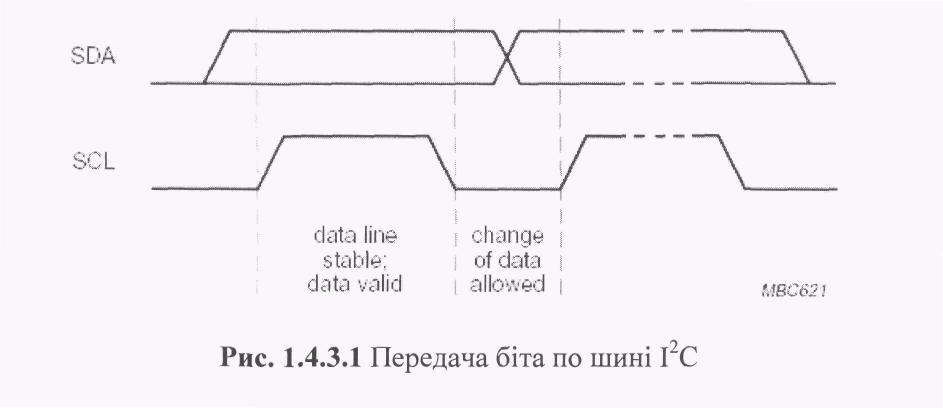

Коректність даних

Дані на лінії SDА повинні бути стабільні, коли тактовий сигнал - в стані НІGН. Стани НІGН і LOW на лінії SDА можуть змінитися тільки тоді, коли такт на лінії SCL знаходиться в стані LOW (див. рис. 1.4.3.1).

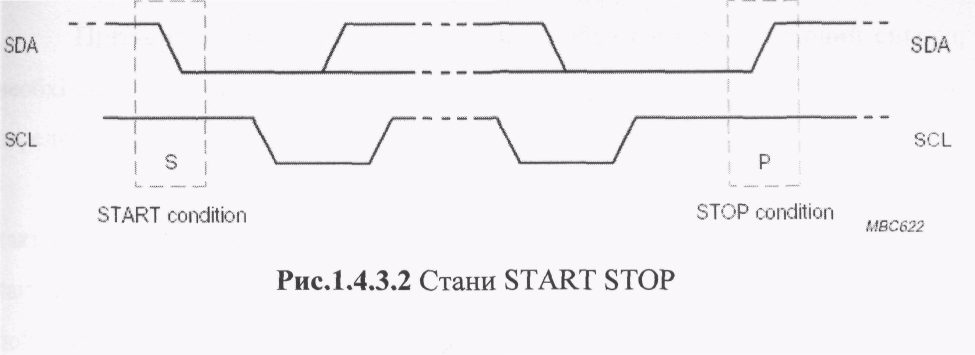

Стани star і sтор

При роботі шини І2С існує два особливих стани, які називаються STARТ і SТОР (див. рис. 1.4.3.2). Переключення лінії SDА з НІGН в LOW, коли SCL знаходиться в стані НІGН, називається станом STARТ. Переключення лінії SDА з LOV в НІGН, коли SCL знаходиться в стані НІGН, називається станом SТОР.

Ці стани завжди генерує майстер. Після появи стану STARТ, шина вважається зайнятою. Шина вважається вільною через визначений час після виникнення стану SТОР.

Передача байта

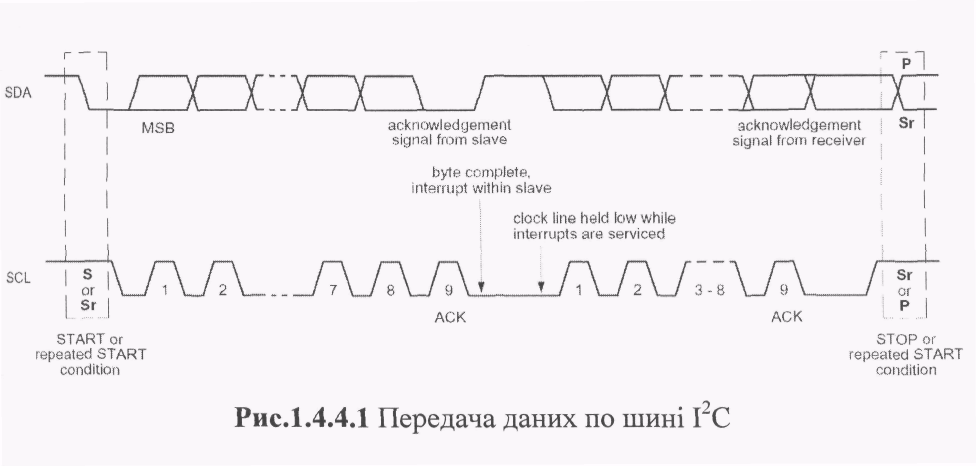

Формат байта

Кожен байт, який передається в лінію SDА, повинен мати довжину 8 біт. Кількість байт, які передаються за один раз, не обмежується. За кожним переданим байтом повинен йти біт-підтвердження. Дані передаються в порядку МSВ (Most significant Bit) (див. рис. 1.4.4.1). Якщо приймач не в змозі прийняти наступний повний байт інформації з тієї причини, що він, наприклад, зайнятий обробкою внутрішнього переривання, він може утримувати SCL у стані LOW, щоб змусити передавач перейти в стан очікування. Передача даних відновляється, коли приймач готовий до приймання чергового байта даних і відпускає лінію SCL.

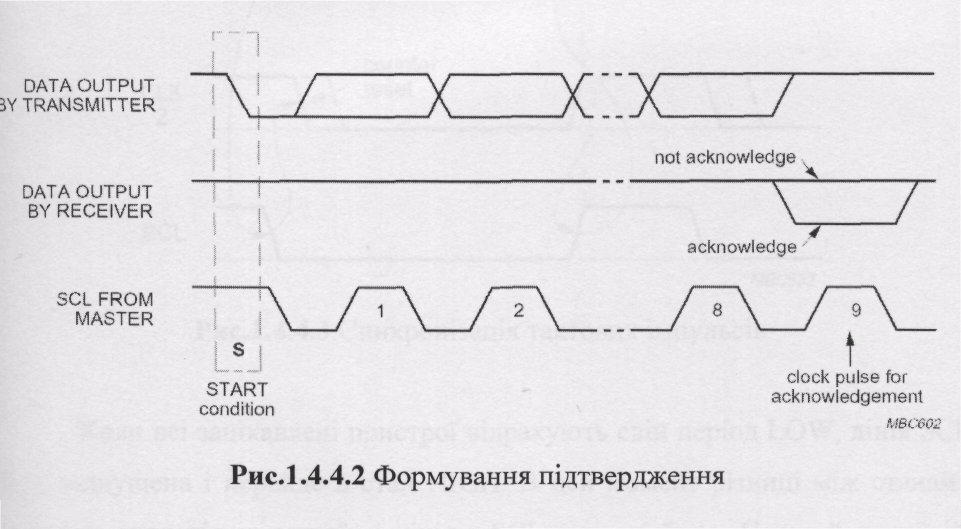

Підтвердження

Підтвердження при передачі даних є обов'язковим. Тактовий сигнал, необхідний для підтвердження, генерується майстром. При підтвердженні передавач відпускає лінію SDA (НIGH) під час тактового сигналу.

Приймач повинен опустити лінію SDА під час підтверджуючого тактового сигналу так, що вона залишається в стабільному стані LOW, коли тактовий імпульс - в стані НIGH (див. рис. 1.4.4.2). Звичайно, час set-uр і hold повинен бути врахований (див. таблицю 1.4.7.2).

Коли slave-приймач не підтверджує адресу slave (наприклад, він не готовий до приймання через виконання деякої геаl-time функції), slave повинен утримувати лінію даних у стані НIGH. В цьому випадку майстер може припинити передачу даних, згенерувавши стан SТОР.

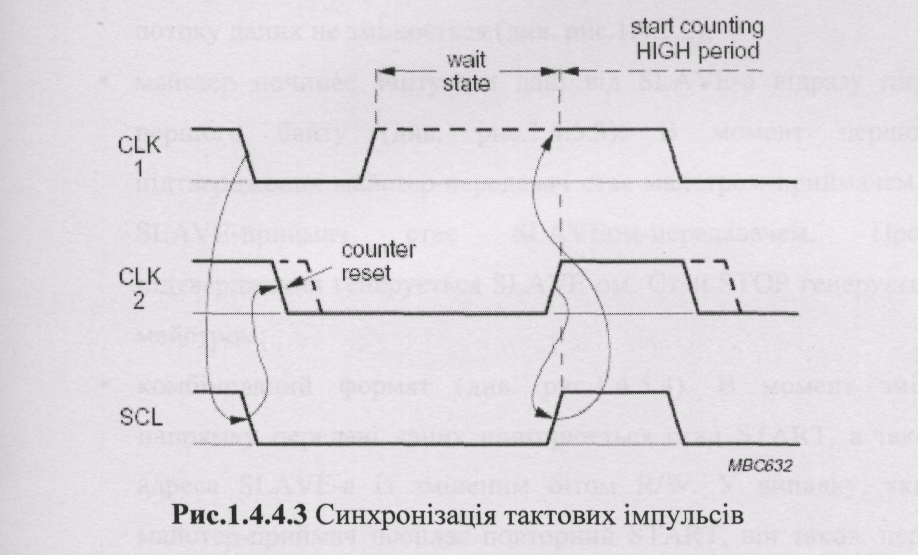

Синхронізація

Всі майстер-пристрої генерують свої тактові сигнали на лінії SCL при передачі повідомлень по шині І2С. Дані дійсні тільки тоді, коли тактовий сигнал знаходиться в стані НIGН.

Синхронізація тактових сигналів відбувається за допомогою послідовного з'єднання провідниками інтерфейсів І2С з лінією SСL. Це

означає, що переключення лінії SCL із стану НIGH буде знаком для відповідних пристроїв почати відлік їх власного періоду LOW, і, оскільки такти пристрою знаходяться в стані LOW, лінія SCL буде утримуватися в цьому стані доти, доки такт не досягне стану НIGН (див. рис. 1.4.4.3). Однак, переключення цих тактів з LOW y HIGH може не викликати зміни стану на лінії SCL, якщо інші тактові сигнали все ще знаходяться в стані LOW. Таким чином, лінія SCL буде утримуватися в стані LOW пристроєм з самим довгим періодом LOW Пристрої з більш короткими періодами LOW переходять у цей час у стан очікування НIGН.

Коли всі зацікавлені пристрої відрахують свій період LOW, лінія SCL буде відпущена і перейде в стан НIGН. В цей момент різниці між станами тактових сигналів пристроїв і лінією SCL вже не буде. Перший пристрій, який завершив свій період НIGН, знову переведе лінію SCL в LOW.

Таким методом генеруються такти синхронізації на SCL, причому, період LOW визначається пристроєм з самим довгим періодом LOW, а період НIGН визначається пристроєм з самим коротким періодом НIGН.

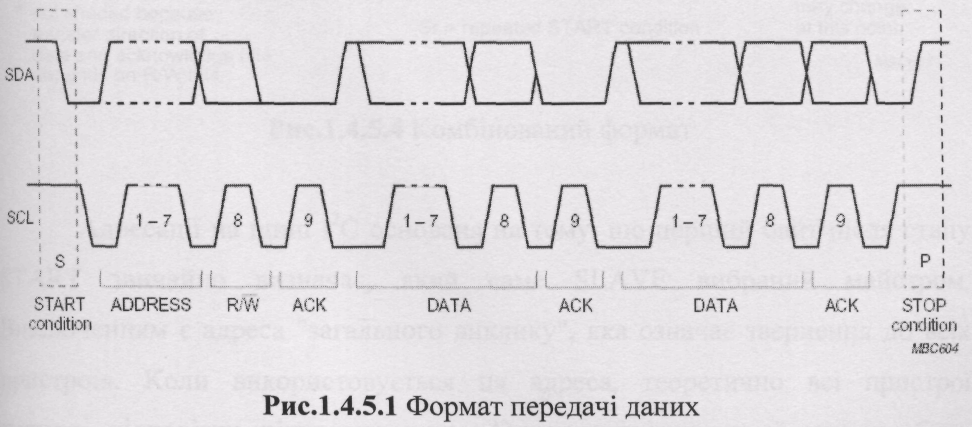

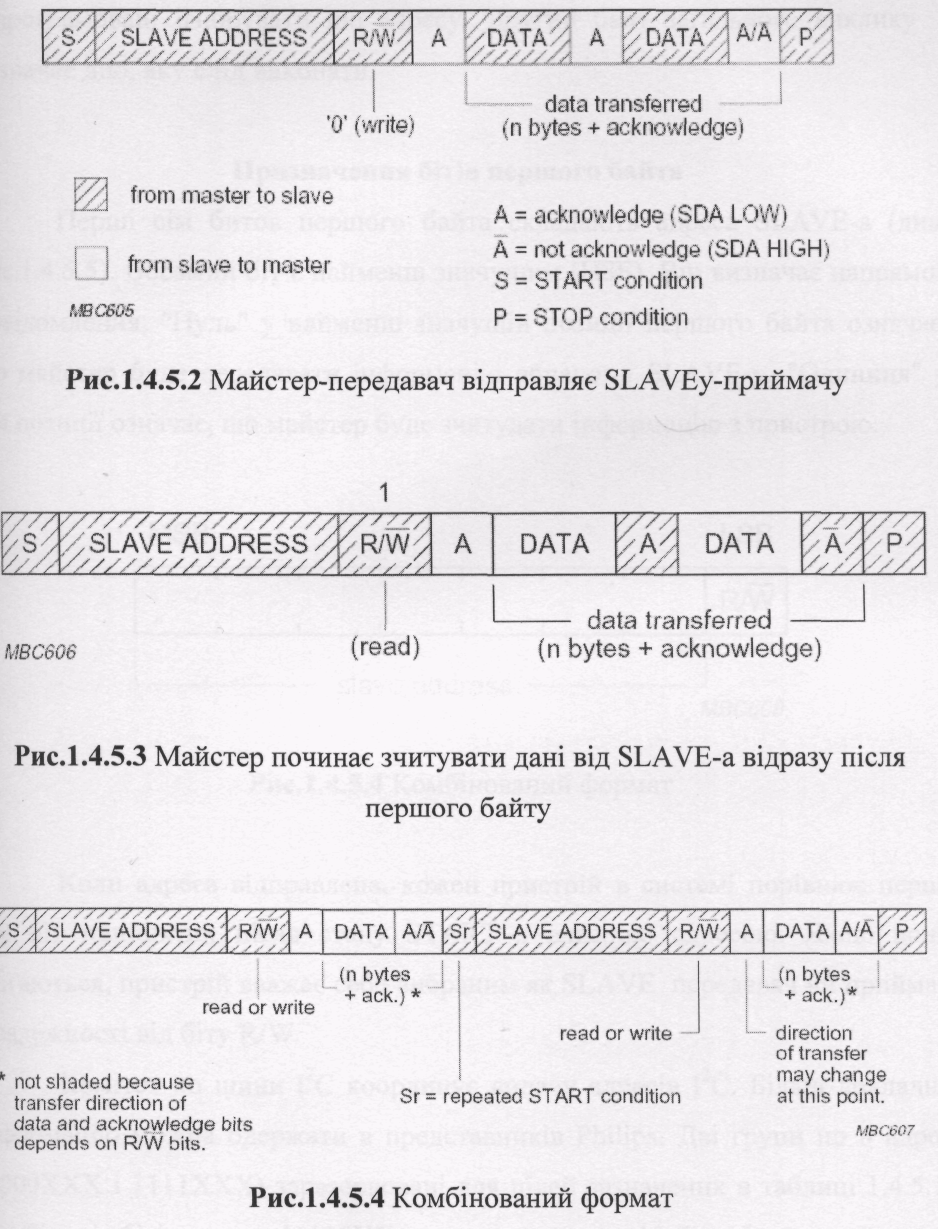

Формат з 7-бітною адресацією

Передача даних відбувається за форматом показаному на рис. Після стану SТАRT (S) посилається адреса SLAVE-а. Адреса складається з семи біт, за якими посилається біт, який визначає напрям передачі даних (R\W), в якому 'нуль' означає передачу (WRIТЕ), а 'одиниця' - запит даних (READ). Передача даних завжди переривається станом SТОР. В рамках такої передачі можливі різні комбінації форматів приймання-передачі.

Можливі наступні формати передачі даних:

• майстер-передавач відправляє SLAVЕ у приймач. Напрям потоку даних не змінюється (див. рис.);

• майстер починає зчитувати дані від SLAVЕ-а відразу після першого байту (див. рис.). В момент першого підтвердження майстер-передавач стає майстром-приймачем, а SLEVЕ-приймач стає SLEVEом-передавачем. Проте підтвердження генерується SLEVЕ-ом. Стан SТОР генерується майстром;

• комбінований формат (див. рис.). В момент зміни напрямку передачі даних повторюється стан STARТ, а також адреса SLEVЕ-а із зміненим бітом R\W. У випадку, якщо майстер-приймач посилає повторний START, він також перед цим посилає НОТ АСКNOWLEDGE.

Адресації на шині І2С основана на тому, що перший байт після стану STARТ звичайно визначає, який саме SLAVЕ вибраний майстром. Виключенням є адреса "загального виклику", яка означає звернення до всіх пристроїв. Коли використовується ця адреса, теоретично всі пристрої повинні відповісти підтвердженням. Однак деякі пристрої можуть бути

запрограмовані ігнорувати цю адресу. Другий байт загального виклику визначає дію, яку слід виконати.