- •История развития средств вычисления Этапы развития:

- •Простейшие вычислительные инструменты

- •Электронно-вычислительные машины

- •Вычислительные системы и сети эвм

- •Классификация вычислительных машин

- •По способу представления и обработки информации.

- •Аналоговые вм

- •Цифровые вм

- •По способу представления и обработки информации.

- •По производительности.

- •Принципы построения эвм

- •Архитектура эвм

- •Характеристики эвм

- •Состав программного обеспечения и возможность его замены.

- •Технические и эксплуатационные характеристики.

- •Функциональные и структурные организации процессора

- •Стандартный цикл выполнения команды

- •Программная модель микропроцессора.

- •Характеристики процессоров

- •7. Изготовитель

- •Устройство управления процессора

- •Структурная модель и схема уу

- •Конкретизованная схема уу

- •Арифметико-логическое устройство процессора (алу)

- •Структура алу

- •Классификация алу

- •I. По способу организации вычислений:

- •II. По способу представления информации

- •III. По виду связи между элементами алу

- •IV. По способу построения

- •Об универсального алу

- •Система команд

- •Форматом команд

- •Системой операций

- •Способами адресации. Формат команд

- •Система операций

- •Логические команды и команды сдвига

- •Адресация

- •Классификация методов адресации

- •I. По количеству обращений в оп

- •II. По наличию адресной информации

- •III. По времени обращения (расположения операндов)

- •IV. По способу формирования исполнительного адреса

- •Архитектура системы команд

- •Запоминающие устройства эвм

- •Классификация зу

- •I. По способу записи:

- •II. По виду операций обращения

- •III. По способу доступа к месту хранения информации

- •IV. По размещению

- •Иерархическая структура памяти эвм

- •Организация шин

- •Типы шин

- •Иерархия шин

- •Системы ввода/вывода

- •Адресное пространство системы ввода/вывода

- •Внешние устройства

- •Модули ввода/вывода

- •Методы управления вводом/выводом

- •Вычислительные системы Классификация вычислительных систем

- •Архитектура вычислительных систем

- •Классификация параллельных вычислительных систем

Характеристики процессоров

1. Тактовая частота. Позволяет косвенно определить быстродействие процессора. fсрн = n100 МГц … n ГГц.

2. Разрядность. (Внутренняя разрядность, которую может обработать процессор на аппаратном уровне). Разрядность процессора совпадает с разрядностью регистров. Nвнут 32 … 62 bit.

3. Характеристики шины Ц.П. (Взаимодействие с внешними устройствами).

Na – разрядность адресной шины. (Определяет максимальный объем ОП, который может обращаться к Ц.П. – 2Na байт)

Nвнеш – разрядность шины данных. (Количество информации, которую может получать и передавать процессор)

fFSB – частота шины. (Определяет частоту передачи данных от процессора к внешним устройствам). У современных процессоров fFSB < fсрн. Тактовая частота кратна частоте шины: fсрн = k* fFSB; fFSB (533 МГц - 1333 МГц);

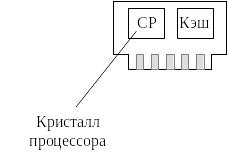

4. Емкость кэш-памяти (второго уровня). Скэш – память небольшого объема с высоким быстродействием. Скэш (8 Мб - 12 Мб);

5. Рассеиваемая мощность - тепловыделение процессора, Pвыд, Вт.

6. Степень интеграции – сложность процессора, Стинт = N*100 млн.

7. Изготовитель

Intel

IBM

Motorola

Cyrix

ADM

8. Интерфейс процессора – тип разъема.

Первоначально использовался разъем типа Socket -

Для увеличения производительности кэш-память стали помещать к процессору (Athlon, Pentium II, III) - разъем типа Slot.

Затем появилась возможность помещать кэш-память в процессор, и произошло возвращение к разъемам типа Socket (PGA, LGA).

9. Стоимость.

10. Архитектура процессора. На сегодняшний день разработана новая архитектура процессора - процессор с двумя ядрами, который по определению обходит по быстродействию одноядерные процессоры. Однако не все приложения поддерживают такую организацию процессора и работают в прежнем режиме.

Устройство управления процессора

Назначение УУ: реализует управление кодом вычислительного процесса, обеспечивая автоматическое выполнение команд программы.

Команда – это последовательность операций.

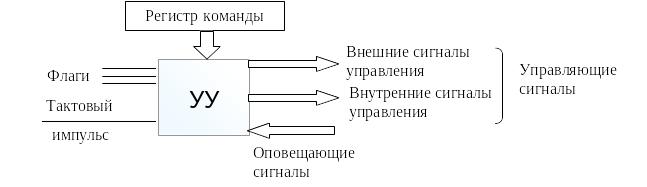

Структурная модель и схема уу

Тактовый импульс обозначает границы машинных тактов процессора, т.е. интервалы времени.

Регистр команды содержит двоичный код команды, которая подлежит выполнению.

Флаги необходимы для оценки состояния процессора и результата предыдущей операции. (Используются при выполнении команд передачи управления).

Оповещающие сигналы обеспечивают передачу УУ запросов прерываний, сигналов подтверждения и т.п.

Управляющие сигналы формируются устройством управления для инициализации определенных действий со стороны других устройств процессора ЭВМ.

В современных ЭВМ реализуется принцип микропрограммного управления:

Любая операция, реализуемая ЭВМ рассматривается как последовательность элементарных действий, называемых микрооперациями. Выполнение микрооперации не превышает 1-го такта.

Для управления порядком следования микроопераций используются логические условия, которые в зависимости от результатов выполнения предыдущих микроопераций могут принимать значения 0 или 1.

Процесс выполнения команды записывается в виде логарифма, представленного в терминах микроопераций и логических условий - микропрограмма.

Микропрограмма определяет порядок проверки логических условий и следования микроопераций, необходимый для выполнения команды. Совокупность микропрограмм для всех команд (firmWare) определяет возможности процессора по !!!!!!!!!!!!!.

Устройство (в составе УУ), отвечающее за выполнение микропрограмм называется микропрограммным автоматом (МПА).