- •История развития средств вычисления Этапы развития:

- •Простейшие вычислительные инструменты

- •Электронно-вычислительные машины

- •Вычислительные системы и сети эвм

- •Классификация вычислительных машин

- •По способу представления и обработки информации.

- •Аналоговые вм

- •Цифровые вм

- •По способу представления и обработки информации.

- •По производительности.

- •Принципы построения эвм

- •Архитектура эвм

- •Характеристики эвм

- •Состав программного обеспечения и возможность его замены.

- •Технические и эксплуатационные характеристики.

- •Функциональные и структурные организации процессора

- •Стандартный цикл выполнения команды

- •Программная модель микропроцессора.

- •Характеристики процессоров

- •7. Изготовитель

- •Устройство управления процессора

- •Структурная модель и схема уу

- •Конкретизованная схема уу

- •Арифметико-логическое устройство процессора (алу)

- •Структура алу

- •Классификация алу

- •I. По способу организации вычислений:

- •II. По способу представления информации

- •III. По виду связи между элементами алу

- •IV. По способу построения

- •Об универсального алу

- •Система команд

- •Форматом команд

- •Системой операций

- •Способами адресации. Формат команд

- •Система операций

- •Логические команды и команды сдвига

- •Адресация

- •Классификация методов адресации

- •I. По количеству обращений в оп

- •II. По наличию адресной информации

- •III. По времени обращения (расположения операндов)

- •IV. По способу формирования исполнительного адреса

- •Архитектура системы команд

- •Запоминающие устройства эвм

- •Классификация зу

- •I. По способу записи:

- •II. По виду операций обращения

- •III. По способу доступа к месту хранения информации

- •IV. По размещению

- •Иерархическая структура памяти эвм

- •Организация шин

- •Типы шин

- •Иерархия шин

- •Системы ввода/вывода

- •Адресное пространство системы ввода/вывода

- •Внешние устройства

- •Модули ввода/вывода

- •Методы управления вводом/выводом

- •Вычислительные системы Классификация вычислительных систем

- •Архитектура вычислительных систем

- •Классификация параллельных вычислительных систем

II. По наличию адресной информации

Явные методы (в адресном поле содержится вся необходимая информация).

Неявная адресации (адресная информация в команде отсутствует полностью или частично). В этом случае недостающая информация подразумевается – месторасположение операнда жестко определено для данной команды.

Например, imul var_1 (операция умножения, здесь расположение второго сомножителя располагается в регистре, куда и поместится результат выполнения) или cbw (convert by to word); Неявная адресация применяется во всех ВМ для сокращения длины команды.

III. По времени обращения (расположения операндов)

Непосредственные операнды

Регистровые операнды

Операнды в памяти

Обращение к непосредственным и регистровым операндам занимает практически одно и то же время. Операнд в памяти требует более длительного обращения.

IV. По способу формирования исполнительного адреса

Абсолютная адресация. При абсолютной адресации исполнительный адрес извлекается целиком либо из адресного поля команды (при прямой адресации), либо из другой ячейки памяти (при косвенной адресации). Никаких преобразований адреса не происходит.

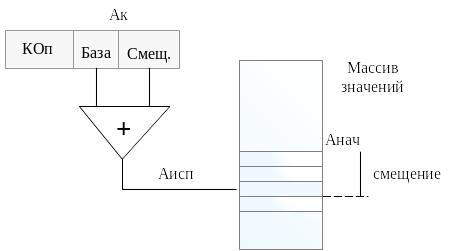

Относительная адресация. Исполнительный адрес находится как сумма нескольких составляющих (как правило, не больше трех) – база, смещение и индекс.

Длина команды в этом случае получается достаточно большой. Для сокращения длины команды и уменьшения времени выполнения базу (или смещение) помещают в регистр, а смещение указывается как переменная.

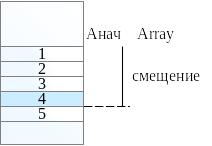

Например, объявим одномерный массив Array db 1,2,3,4,5.

Поместим смещение в ВХ: lea BX,Array

mov AL,[BX]+3

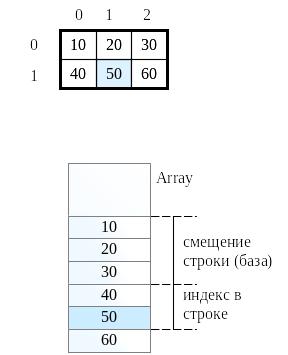

Для многомерных массивов используется базово-индексная адресация. Физически элементы массива будут располагаться один за другим, как в одномерном массиве. В этом случае необходимо задать 2 смещения - смещение строки, которое будет являться базой, и индекс в строке.

mov AL, Array + [BX] + [SI]

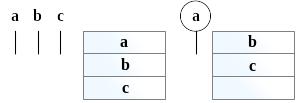

Стековая адресация

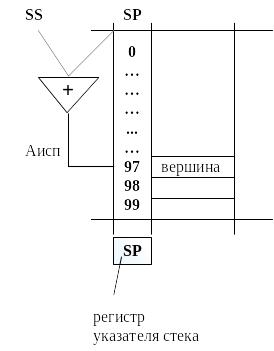

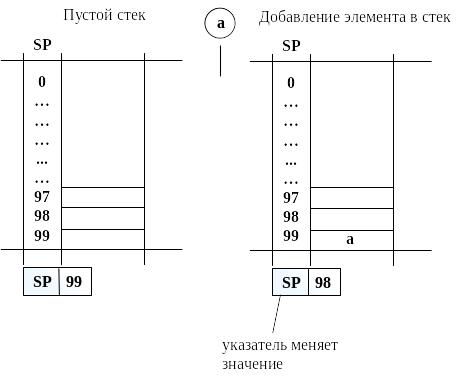

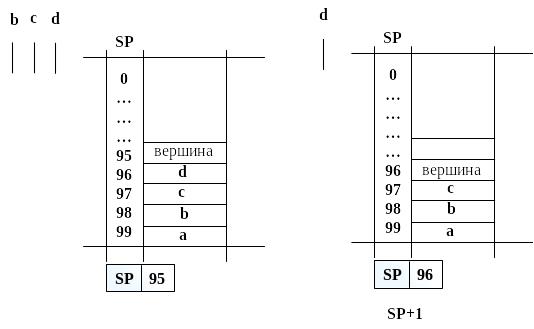

Стек – это несколько смежных ячеек памяти, обращение к содержимому которых осуществляется с помощью неявной адресации по определенному правилу.

Для работы со стеком доступны две основные команды: запись в стек (push - источник) источник –> стек; считать из стека (pop - приемник) приемник <– стек.

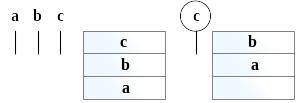

Существует два вида стека:

FIFO (First Input First Output) – считывается значение, первым записанное в стек.

LIFO (Last Input First Output) – считывается значение, последним записанное в стек.

На практике стек организуют на основе оперативной памяти и указателя стека. Для записи всегда доступна так называемая вершина стека.

Архитектура системы команд

Программное обеспечение создается в основном с помощью программирования на языках высокого уровня. Сами команды языков программирования высокого уровня удобны, но процессор выполняет простые операции и команды. Такую проблему стали называть семантическим разрывом. Перед разработчиками программного обеспечения встала задача уменьшить этот разрыв, что привело к созданию различных архитектур системы команд.

CISC-архитектура

(процессор с полным набором команд)

Целью разработки CISC-архитектуры стало создание универсального процессора, где машинные команды очень близки к операторам языка программирования высокого уровня. Это привело к тому, что система команд стала обширной (возросло количество команд), а сложность процессора значительно увеличилась.

Особенности структуры:

В процессоре присутствует небольшое количество регистров общего назначения

Наличие нескольких методов адресации

Различие форматов команд

Наличие команд, где обработка совмещается с обращением к памяти

Сложность и стоимость таких процессоров были достаточно велики, а производительность наоборот была небольшой. К тому же в результате исследований в 80-х годах выяснилось, что 80% времени выполнения процессором команд выполняются почти одни и те же команды, которые занимали около 20% от общего числа команд. Таким образом, оказалось, что использование CISC-архитектуры неэффективно и невыгодно. На смену ей пришла новая архитектура с сокращенным набором команд.

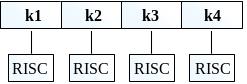

RISC-архитектура

(процессор с сокращенным набором команд)

В таких процессорах система команд была существенно сокращена за счет того, что были оставлены лишь наиболее часто используемые команды.

Особенности RISC-архитектуры:

Сокращено количество методов адресации (все операции обработки выполняются лишь над регистровыми операндами);

Обращение к памяти допустимо лишь с целью записи или чтения, что позволило разделить операции обработки данных и обращения к памяти;

Все это привело к упрощению команд, сокращению времени их выполнения (большинство команд обработки выполняются за один такт). Отсутствующие команды образуются за счет комбинаций имеющихся, и выполняются гораздо быстрее. Процессор становится более простым, дешевым и доступным. Но для того чтобы такой процессор работал эффективно, необходимо было увеличить количество регистров, которое могло исчисляться сотнями. Подобные процессоры выпускаются с 80-х годов.

MISC-процессор

(процессор с минимальным набором команд)

В таком процессоре команды выполняются параллельно, а каждый RISC-процессор еще более упрощается.