- •Содержание

- •Введение

- •Анализ исходных данных

- •Описание алгоритма реализации заданной операции.

- •2.1 Операция умножения двух чисел используя алгоритм Бута

- •Блок вычитания двух чисел

- •Разработка блок-схемы устройства и описание работы цикла .

- •Составление и минимизация комбинационной схемы.

- •Представление основных элементов в требуемом базисе.

- •Описание регистров.

- •Описание работы компараторов.

- •Описание работы сумматоров.

- •Описание работы мультиплексора.

- •Реализация блока перевода в дополнительный код.

- •Составление комбинационной схемы дешифратора.

- •Реализация блока перевода в код с избытком 3.

- •Описание работы устройства для реализации заданной операции.

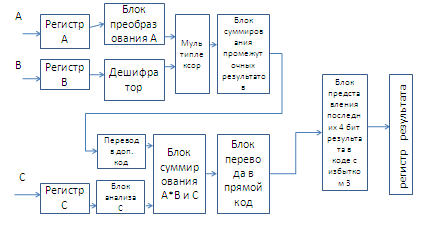

Разработка блок-схемы устройства и описание работы цикла .

Рис 3.1 блок-схема устройства.

Теперь следует кратко описать принцип работы данного устройства:

Числа А,В и С записываются параллельно в соответствующие регистры.

После того как числа были записаны с параллельные регистры, число А представляется как А, -А, 2А, -2А. Данные значения передаются на информационные входы мультиплексора. Множитель В поступает на дешифратор (логический преобразователь), который в свою очередь анализирует тройки разрядов, декодирует их и передаёт результат декодирования на мультиплексор. Мультиплексор исходя их полученных данных выбирает один из вариантов частичного произведения, а именно: 0, А, -А, 2А, -2А. Мультиплексор по данному сигналу выбора передаёт на сумматор необходимый вариант частичной суммы, которая уже умножена в зависимости от i-го разряда тройки.

После этого числа значение А*В переводится в дополнительный код и подаётся на сумматор. Обновремменно число С анализируется. Если С отрицательное, то на блок перевода в дополнительный код подаётся данное число без преобразований, но уже со знаковым битом равным 0 . А если число число положительное, то на блок перевода в дополнительный код подаётся данное число без преобразований, но уже со знаковым битом равным 1.

После прохождения чисел через сумматора на выходе получается число, которое представлено в дополнительном коде. Его нужно перевести в прямой код. Для этого нужно проанализировать результат. Если у получившиеся при суммировании число положительное, т.е. знаковый бит равен 0, то это число и будет результатом сложения чисел (А*В)-С. Если же результат отрицательный, т.е. знаковый бит равен 1, то нужно от результата отнять 1 и после этого проинвертировать все биты числа (кроме знакового). Получившиеся число и будет результатом суммирования (А*В)-С.

После того как получена значение функции, оно передаются на блок представления последних 4 бит результата в с избытком 3.

После преобразования последних 4 бит значение передаётся на регистр результата.

Составление и минимизация комбинационной схемы.

Представление основных элементов в требуемом базисе.

По условию курсового проекта нужно разработать комбинационную схему в алгебре Жегалкина, т.е. все элементы в комбинационной схеме должны быть выражены через элемент исключающее ИЛИ, логическую единицу и конъюнкцию.

Исключающие ИЛИ:

Конъюнкция:

Основные соотношения алгебры Жегалкина:

х

=1

х

=1

х

х

v y=x y x*y

v y=x y x*y

Эти два соотношения позволяют перейти от любого выражения в булевой алгебре к соответствующему выражению в алгебре Жегалкина

Описание регистров.

Регистры – самые распространенные узлы цифровых устройств. Они оперируют с множеством связанных переменных, составляющих число. Над числами выполняется ряд операций:

Прием

Выдача

Хранение

Сдвиг в разрядной сетке

Поразрядные логические операции

Регистры состоят из разрядных схем, в которых имеются триггеры и, чаще всего, также логические элементы.

Все регистры данного устройства имеют общую особенность – они реализованы на базе триггеров типа D. Триггеры типа D принимают информацию по одному входу и реализуют задержку сигнала с помощью тактирования. Момент принятия информации триггером определяется тактовым сигналом С.

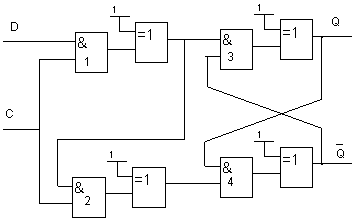

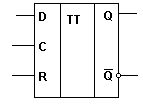

Рассмотрим D-триггер.

Рис . 4.1 схема D-триггера.

При С=0 на выходах элементов 1 и 2 действуют единичные сигналы и цепь памяти сохраняет своё состояние. При С=1 состояние элементов 1 и 2 определяется информационным сигналом: если D=1, то и на выходе Q установиться единица, а при D=0 будет Q=0.

Понятно, что при записи новой информации, удаляется старая.

Иногда данная ситуация не допустима. Бывают случаи, когда нужно при чтении новой информации сохранить на некоторое время старую.

Решение данной проблемы было найдено в двухступенчатом триггере, именно путём введения второго запоминающего элемента (второй ступени). Новая информация формируется сначала только во входной ступени триггера при сохранении старой информации в выходной его ступени. Когда новое состояние входной ступени сформировано и снят активный уровень сигнала с синхровхода С, происходит её перезапись в выходную ступень устройства. В принципе, двухступенчатый триггер состоит из двух последовательно соединённых триггеров – ведущего и ведомого.

Рис. 4.2 схема двухступенчатого триггера и условное обозначение

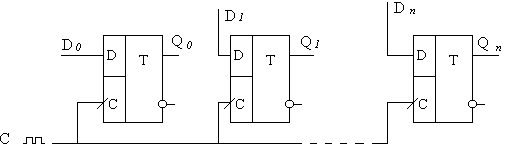

Параллельные регистры состоят из разрядных схем, в данном случае D-триггеров, не связанных между собой:

Рис. 4.3 схема параллельного регистра.

Вход D – информационный; С – синхровход, по которому подаётся сигнал, разрешающий смену состояния триггера.

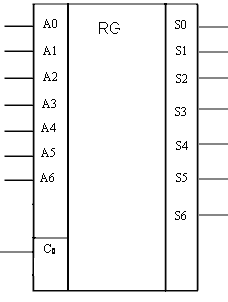

Рис. 4.4 условное обозначение параллельного семиразрядного регистра

Последовательно-параллельный регистр является, как правило, универсальным и может выполнять все доступные для регистров микрооперации:

Приём

Хранение

Выполнение поразрядных логических операций над не сколькими словами

Сдвиг слов в разрядной сетке

Для этого разрядные схемы, входящие в его состав, соединены между собой следующим образом:

Рис. 4.5 схема последовательно-параллельного регистра

Так же следует отметить, что в последовательно-параллельных и последовательных (сдвигающих) регистрах используются только двухступенчатые триггеры или триггеры с динамическим управлением. Такая особенность обусловлена тем, что это гарантирует сдвиг информации строго на один разряд по каждому импульсу синхронизации. Если же не использовать триггеры такого типа, то процесс сдвига становится неуправляемым, и за один импульс синхронизации информация может быть сдвинута на несколько разрядов, что будет недопустимо в нашем случае.

Выбор режима работы последовательно-параллельного регистра определяется значением сигнала на входе СL.

При подаче импульса на вход CL(С0=0) регистр работает как сдвиговый регистр.

При подаче импульса на вход С0(CL=0) регистр работает как параллельный регистр.

В нашем случае изображена схема регистра, который выполняет сдвиг выполняется влево, т.е. из младшего разряда в старший.

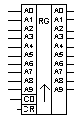

Рис . 4.6 условное обозначение последовательно-параллельного регистра для сдвига влево

Для создания регистра сдвигающего вправо надо всего лишь поменять порядок соединения между собой регистров.

Рис . 4.7 условное обозначение последовательно-параллельного регистра для сдвига вправо.

В нашем случае для умножения мы будем использовать 10-разрядные регистры. Это объясняется тем, что из условия курсового проекта дано, что числа А и В должны быть представлены пятиразрядными числами.

Следовательно например:

А=31 (11111)2 = (31)10

В=31 (11111)2 = (31)10

F=A*B=31*31=961

(961)10 =(1111000001)2

Как видно из примера для работы с перемножение чисел A и В нужно использовать 10-разрядные регистры. Знак получившегося произведения будет считаться отдельно и подаваться на блок перевода в дополнительный код.

Для суммирования А*В и С мы будем пользоваться 11-разрядными регистрами.

Например:

С=31 (11111)2 = (31)10

А*В=961 (1111000001)2 = (961)10

F=(A*B)-С=961+31=992

(992)10 =(1111100000)2

Если учесть еще 1 знаковый бит, то получается , что результат суммирования будет 11-битное число.

Регистр результата вычислений будет 11разрядным.