- •111Equation Chapter 1 Section 1Содержание

- •Введение

- •Анализ исходных данных

- •Алгоритм работы устройства

- •2.1 Операция умножения двух чисел по алгоритму Бута

- •В сумматоре sm

- •2.2 Блок сложения двух чисел

- •3. Описание алгоритма реализации заданной операции.

- •4. Составление и минимизация комбинационных схем.

- •4.1. Составление комбинационной схемы регистра.

- •4.3 Описание регистров.

- •Составление комбинационной схемы одноразрядного сумматора

- •4.5 Описание работы мультиплексора.

- •Общая комбинационная схема разработанного устройства

3. Описание алгоритма реализации заданной операции.

В данной курсовой работе необходимо разработать арифметическое устройство, отвечающее определённым требованиям.

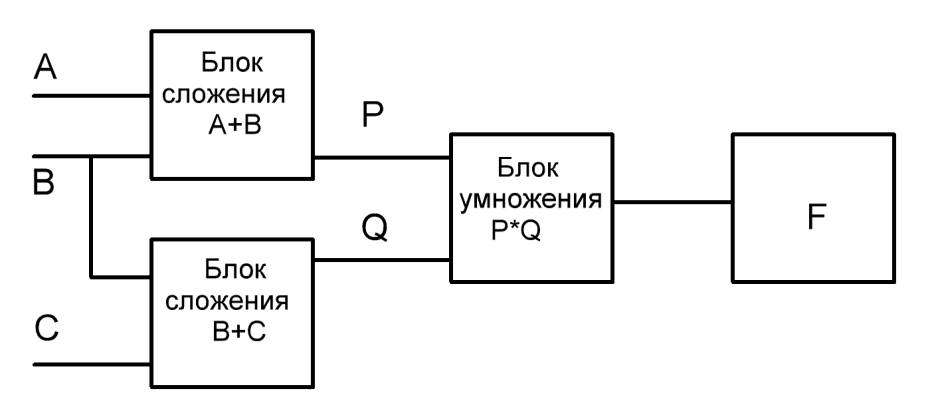

Вышеупомянутое устройство должно выполнять послебовательно действия, представленные на схеме:

Рис.2 Описание алгоритма реализации

Схема состоит из блоков сложения, блока умножения.Блок сложения

АВ представляет собой многоразрядный сумматор. На его

входы подаются значения А,В и С,где 0<A,B,C<1.

Сложение реализуется в два такта

Для того, чтобы получить окончательное число, используется мультиплексор.

На его информационные входы подаётся результат, полученный на выходе

сумматора.

Блок умножения, реализованного по алгоритму Бута, исключив нечётные

степени множителя, имеет довольно сложную реализацию.

На информационные входы мультиплексора подаются 0, выходное

значение из блока вычитания АВ, оно же сдвинутое на один разряд

влево (т.е. увеличенное в два раза). Это осуществляется при помощи

сумматора, на входы которого подаются 0 и инвертированная форма числа.

Число в регистре сдвигается на два разряда вправо.

Выходное значение мультиплексора подаётся на один из входов

сумматора. На другой вход подаётся значение из запоминающего регистра

(первоначальное значение 0). Полученная сумма передаётся в запоминающий

регистр. Цикл повторяется до тех ,пор пока в сдвигающем регистре не

останется 0.

4. Составление и минимизация комбинационных схем.

4.1. Составление комбинационной схемы регистра.

Регистры – самые распространённые узлы ЭВМ. Они состоят из разрядных схем, число которых соответствует разрядности обрабатываемых слов. В каждом разряде имеются триггер (иногда и не один) и чаще всего логические элементы.

Регистры выполняют ряд микроопераций над словами. Нам понадобятся три основных группы микроопераций: приём слова (которое будет храниться в регистре, пока не появится команда на их смену), выдача слова и сдвиг слов в разрядной сетке.

Первые две группы операций могут выполнять статические регистры, а вот сдвиг кода в разрядной сетке в нашем случае будут выполнять регистры сдвига (им, впрочем, подвластны все виды микроопераций над словами).

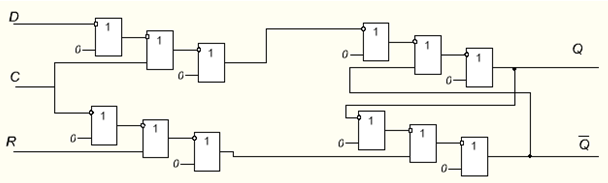

Параллельные

регистры будут построены на триггерах

типа D. Такой триггер имеет вид:

Где D – информационный

вход триггера, С – разрешение на запись

(управляющий сигнал), Q и

–

прямой и инверсный выходы. Информация,

пришедшая в триггер по входу D

параллельная запись информации происходит

синхронно, по положительному значению

тактового импульса.

–

прямой и инверсный выходы. Информация,

пришедшая в триггер по входу D

параллельная запись информации происходит

синхронно, по положительному значению

тактового импульса.

Вывод информации из регистра осуществляется через прямые выходы соответствующих триггеров.

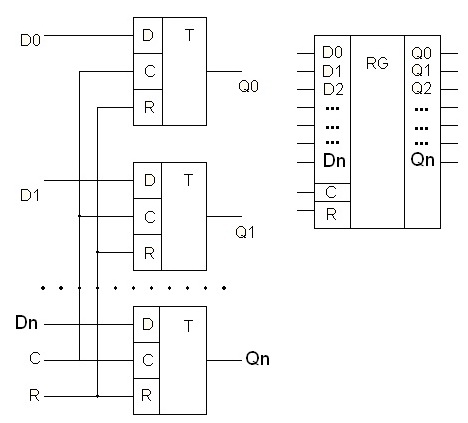

То статический n-разрядный регистр имеет вид:

Универсальные регистры так же будут построены на D-триггерах, однако там каждая ячейка содержит два D-триггера и логические элементы, с помощью которых регистр будет принимать либо режим параллельного, либо сдвигающего.

4.2 Представление основных элементов в требуемом базисе.

По условию курсового проекта нужно разработать комбинационную схему в базисе импликации, логический 0, т.е. все элементы в комбинационной схеме должны быть выражены через элемент дизьюнкцию.

Рис.4.1 Графическое представление импликации

F=x→y

Это соотношение позволяет перейти от любого выражения в булевой алгебре к соответствующему выражению в базисе импликации, логический 0.