- •Содержание

- •Введение

- •Анализ исходных данных

- •2. Описание алгоритма реализации заданной операции

- •3.Блок-схема устройства и описание работы цикла

- •4. Составление и минимизация комбинационных схем.

- •4.1. Составление комбинационной схемы регистра.

- •4.2.Составление комбинационной схемы сумматора

- •4.3. Составление комбинационной схемы мультиплексора.

- •4.3 Составление логической регистра сдвига.

- •4.4. Составление комбинационной схемы дешифратора.

- •4.5. Составление комбинационной схемы регистров сдвига.

- •4.6.Составление логической схемы компаратора

- •4.4. Составление комбинационной схемы бс.

- •5.Анализ и синхронизация работы устройства

- •Заключение

4.3. Составление комбинационной схемы мультиплексора.

Большая часть данных в цифровых системах передается непосредственно по проводам и проводникам печатных плат. Обычно возникает необходимость в многократной передаче информационных двоичных сигналов из одного места в другое. В некоторых случаях нужно передавать данные на большие расстояния по телефонным линиям и кабелям. Если бы все данные передавались одновременно по параллельным линиям связи, общая длина таких кабелей была бы слишком велика и они были бы слишком дороги. Вместо этого данные передаются по одному проводу в последовательной форме и группируются в параллельные данные на приемном конце этой единственной линии связи. Устройства используемые для последовательной посылки и приема данных, называются соответственно мультиплексор и демультиплексор. Параллельные данные одного из цифровых устройств с помощью мультиплексора преобразуются в последовательные информационные сигналы, которые передаются по одному проводу. На выходе демультиплексора эти последовательные сигналы снова группируются в параллельные данные.

Входы мультиплексора делятся на две группы: информационные и управляющие (адресующие).

Мультиплексором (multiplexor) - комбинационное устройство, обеспечивающее коммутацию одного из входов на общий выход под управлением сигналов на адресных входах.

Схема мультиплексора:

Если на Y подать 1, то он пропустит шину А, иначе В.

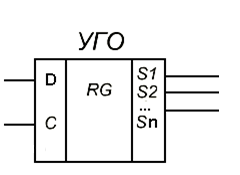

4.3 Составление логической регистра сдвига.

По приходу тактового импульса С первый триггер записывает код X (0 или 1), находящийся в этот момент на его входе D а каждый следующий триггер переключается в состояние, в которой до этого находился предыдущий. Так происходит потому, что записываемый сигнал проходит со входа D триггера к выходу Q с задержкой, большей длительности фронта тактового импульса (в течение которого происходит запись). Каждый тактовый импульс последовательно сдвигает код числа в регистре на один разряд. Поэтому для записи N-разрядного кода требуется N тактов. На диаграмме видно, что четырёх разрядное число 011 было записано в соответствующие разряды регистра (0-S2, 1-S2, 1-Q1) после прихода четвёртого тактового импульса. До прихода следующего тактового импульса это число хранится в регистре в виде параллельного кода на выходах Sn-S1. Если необходимо получить последовательную информацию в последовательном коде, то её снимают с выхода S4 в момент прихода следующих четырёх импульсов такой режим называется режимом последовательного считывания.

С – синхронизация; D – входные данные, Sn –выходы.

4.4. Составление комбинационной схемы дешифратора.

|

По условию задания результат необходимо представить в коде 2-4-2-1. Для перевода воспользуемся, приведенной ниже таблицей:

Таблица 4.1 Таблица представления кодирования двоичных и десятичных чисел в код 2-4-2-1

код 2421 |

десятичные |

двоичные числа |

|||||||||||

|

|

|

1 |

2 |

4 |

2 |

1 |

||||||

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

|

|

|

|

0 |

0 |

0 |

1 |

0 |

2 |

0 |

0 |

1 |

0 |

|

|

|

|

0 |

0 |

0 |

1 |

1 |

3 |

0 |

0 |

1 |

1 |

|

|

|

|

0 |

0 |

1 |

0 |

0 |

4 |

0 |

1 |

0 |

0 |

|

|

|

|

0 |

1 |

0 |

1 |

1 |

5 |

0 |

1 |

0 |

1 |

|

|

|

|

0 |

1 |

1 |

0 |

0 |

6 |

0 |

1 |

1 |

0 |

|

|

|

|

0 |

1 |

1 |

0 |

1 |

7 |

0 |

1 |

1 |

1 |

|

|

|

|

0 |

1 |

1 |

1 |

0 |

8 |

1 |

0 |

0 |

0 |

|

|

|

|

0 |

1 |

1 |

1 |

1 |

9 |

1 |

0 |

0 |

1 |

|

|

|

|

1 |

0 |

0 |

0 |

0 |

10 |

1 |

0 |

1 |

0 |

|

|

|

|

1 |

0 |

0 |

0 |

1 |

11 |

1 |

0 |

1 |

1 |

|

|

|

|

1 |

0 |

0 |

1 |

0 |

12 |

1 |

1 |

0 |

0 |

|

|

|

|

1 |

0 |

0 |

1 |

1 |

13 |

1 |

1 |

0 |

1 |

|

|

|

|

1 |

0 |

1 |

0 |

0 |

14 |

1 |

1 |

1 |

0 |

|

|

|

|

1 |

1 |

0 |

1 |

1 |

15 |

1 |

1 |

1 |

1 |

|

|

|

|

Q4 |

Q3 |

Q2 |

Q1 |

Q0 |

F |

D3 |

D2 |

D1 |

D0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

По таблицы видим, что на выходе должно быть 5 бит.

Составим карты Карно:

Значение Q4:

|

|

D3D2 |

|||

|

|

OO |

O1 |

11 |

10 |

D1D0 |

OO |

0 |

0 |

1 |

0 |

O1 |

0 |

0 |

1 |

0 |

|

11 |

0 |

0 |

1 |

1 |

|

10 |

0 |

0 |

1 |

1 |

|