- •Цифровой фильтр

- •Постановка задачи (введение)

- •Формализация задачи (определение функций аппаратной части и программы и способов их реализации)

- •Функциональная схема цифрового фильтра

- •Исходное состояние Фильтра после включения питания

- •2.3 Формализация настроек для инициализации фильтра

- •. Формализация определений для рабочего цикла фильтра

- •Разработка и описание общего алгоритма функционирования фильтра

- •Обоснование построения аппаратной части фильтра

- •Назначение выводов и настройки ad9708

- •Разработка и отладка программы на языке команд мк

- •Исходные определения и ручной расчет результатов работы программы: «Цифровой фильтр»

- •Для положительных входных отсчётов

- •Для отрицательного входного отсчёта

- •Составление электрической принципиальной схемы и описание функционирования фильтра

- •Расчет быстродействия фильтра

- •Тип частотной избирательности фильтра. Характеристики для заданных и реальных значений коэффициентов (нули и полюсы, ачх, фчх)

- •Заключение (оценка результатов проектирования)

- •10. Список использованных источников

Федеральное государственное бюджетное образовательное учреждение высшего профессионального образования

Рязанский государственный радиотехнический университет

Кафедра радиотехнических систем

Пояснительная записка к курсовому проекту по дисциплине

«Цифровые устройства и микропроцессоры»

Цифровой фильтр

Выполнил: ст.гр. 013

Бочков В.В.

Проверил: доцент, к.т.н.

Сальников Н.И.

Рязань 2013

СОДЕРЖАНИЕ ПОЯСНИТЕЛЬНОЙ ЗАПИСКИ

2

2. Формализация задачи (определение функций аппаратной части и программы и способов их реализации) 4

3. Разработка и описание общего алгоритма функционирования фильтра 12

4. Обоснование построения аппаратной части фильтра 14

5. Разработка и отладка программы на языке команд МК 17

6. Составление электрической принципиальной схемы и описание функционирования фильтра 30

7. Расчет быстродействия фильтра 32

8. Тип частотной избирательности фильтра. Характеристики для заданных и реальных значений коэффициентов (нули и полюсы, АЧХ, ФЧХ) 34

9. Заключение (оценка результатов проектирования) 36

10. Список использованных источников 37

Постановка задачи (введение)

Курсовой проект (КП) предусматривает проектирование специализированного цифрового микропроцессорного устройства, работающего в реальном времени и выполняющего необходимый набор и необходимую последовательность операций над входным сигналом для его преобразования (обработки) по заданному правилу. Суть преобразований входного сигнала вытекает из темы и технического задания на КП.

Проектируемое устройство, его базовая конфигурация должны содержать минимальные аппаратные и программные средства, достаточные для выполнения конкретно поставленной задачи обработки. Специализированные аппаратные и программные средства, “привязанные” к решаемой задаче, должны обеспечивать максимально эффективную реализацию функций по совокупности критериев (стоимость, потребление, быстродействие, точность и т.д.).

Формализация задачи (определение функций аппаратной части и программы и способов их реализации)

Формализация задачи при выполнении всех этапов проектирования предполагает представление выполнение функций фильтра на языке логических и математических связей, в виде логических, математических моделей. Задачей формализации является согласование структурное, логическое, алгоритмическое, электрическое всех аппаратных и программных модулей устройства, обеспечивающее разработку работоспособной электрической схемы (аппаратная часть) и работоспособной программы фильтра, согласованной с аппаратной частью.

Функциональная схема цифрового фильтра

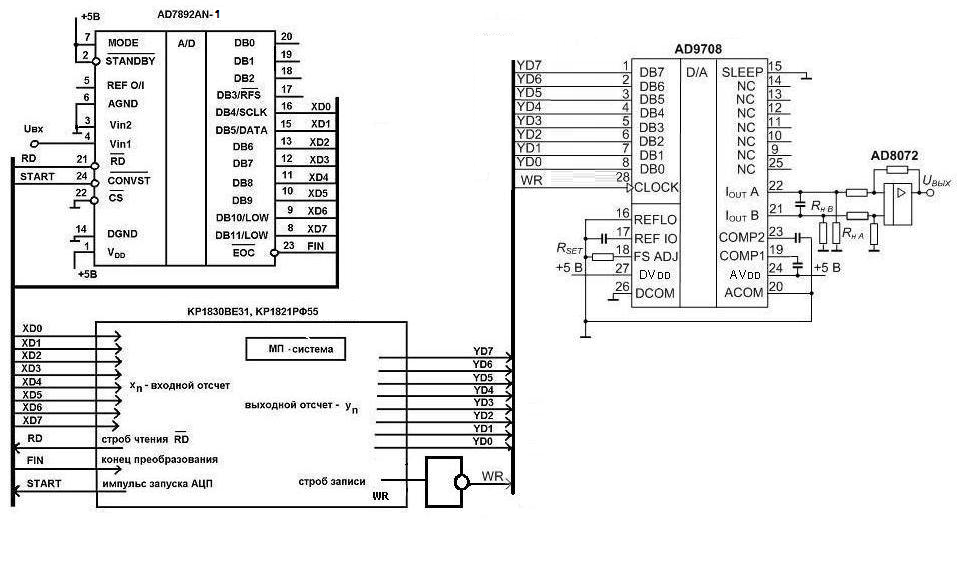

Рис.1 Функциональная схема цифрового фильтра

В качестве БИС АЦП выбрана модификация AD7892AN - 1, для которой диапазон изменения напряжения на входе АЦП равен (-10 ... + 10) В, что соответствует техническому заданию. Вход Vin2 должен быть соединён с аналоговой землёй (Vin2=AGND), опорное напряжение REF IN равно плюс 2.5 В, полный перепад напряжения Vfs равен 20 В, шаг квантования входного сигнала по напряжению 1МЗР= Vfs/212=20 В/4096=4.88 В

Выходной код – дополнительный.

Для чтения результата преобразования входного напряжения выбран параллельный способ (параллельный интерфейс), как более быстрый и простой (для программной реализации). Поэтому на вывод MODE подано напряжение плюс 5 В, что соответствует уровню логической 1.

Напряжение плюс 5 В на выводе STANDBY задает стандартный (нормальный) режим энергопотребления.

Для работы АЦП выбран внутренний источник опорного напряжения, поэтому вывод REF O/I оставлен свободным.

Вход Vin2 остается неподключенным (внутри БИС он никуда не подсоединен).

Напряжение UВХ подаётся непосредственно на вход Vin1 , поскольку АЦП содержит внутреннюю схему выборки хранения (СВХ). Реализация алгоритма последовательных приближений осуществляется под управлением внутреннего тактового генератора, поэтому внешние тактовые импульсы для работы АЦП не требуются.

Пуск АЦП выполняется путём подачи импульса нулевого уровня на вывод CONVST по сигнальной линии START из МП-системы, поскольку БИС AD7892AN-1 всегда выбрана (вывод CS - заземлен). Импульсы с частотой дискретизации FД равной 8000 Гц для запуска АЦП должны формироваться в МП-системе. Определим для этой функции внутренний аппаратный узел МК - таймер/счётчик Т/С0. Для вывода импульсов запуска АЦП из МК назначим вывод Р1.2 порта Р1 БИС КР1830ВЕ31 (по линии START сигнальной шины В рис.1)

Числовые значения отсчётов (двоичные коды), получаемые путем преобразования входного напряжения, в режиме параллельного интерфейса поступают с частотой дискретизации FД на выводы DB0...DB11. Поскольку, в соответствии с ТЗ, разрядность данных равна 8, параллельная шина для чтения данных XD0... XD7 подключена к старшим выводам чтения 12-разрядного кода отсчета - DB4...DB11. Младшие разряды DB0...DB3 - теряются.

Готовность кода для отсчёта входного напряжения обозначает импульс нулевого уровня на выводе ЕОС, вырабатываемый АЦП после каждого цикла преобразования. Импульсы ЕОС, следующие с частотой дискретизации FД равной 8000 Гц, по сигнальной линии FIN поступают в МП-систему для инициирования операций чтения кода из АЦП с такой же частотой.

Для ввода кода текущего входного отсчёта (xn) и запуска цикла вычисления кода текущего выходного отсчёта (уn) определим режим прерываний МК по линии запроса внешних прерываний INT0.

В цикле чтения данных из АЦП процессор вырабатывает управляющий строб для копирования кода отсчёта xn. Управляющий строб по сигнальной линии RD поступает на вывод RD БИС AD7892AN - 1. В соответствии с требованием ТЗ определим, что код отсчёта xn (XDO... XD7) копируется в аккумулятор процессора через порт РA БИС КР1821РФ55 - по линиям шины С, в режиме простого ввода без квитирования.

Вывод (копирование) кода выходного отсчета yn (YD7… YD0) во входной буферный регистр ЦАП определим через порт PB БИС КР1821РФ55, в режиме простого вывода. Запись кода yn в регистр ЦАП выполняется при поступлении нарастающего фронта управляющего строба WR на вход синхронизации CLOCK. Управляющий строб записи вырабатывается процессором в каждом машинном цикле записи данных во внешнее устройство.

Настройка выводов БИС АD9708

Вывод SLEЕP заземлён - работа в нормальном режиме энергопотребления. Вывод REFLO заземлён, вывод REFIO через конденсатор С равный 0.1 мкФ соединен с аналоговой землей –используется внутренний источник опорного напряжения плюс 1,2 В для получения весовых токов ЦАП. Резистор Rset на входе FS ADJ задает максимальное значение выходных токов ЦАП. Наличие конденсаторов, подключенных к входам СОМР1 и СОМР2, обусловлено требованиями подавления внутренних шумов и надежной работы переключателей тока в ЦАП.

Преобразование выходных токов IoutA и IoutB в выходные напряжения в униполярном режиме работы выхода осуществляется с помощью резисторов нагрузки Rнa и Rнв. Знакопеременное выходное напряжение

Uвых=-4…+4В получается с помощью операционного усилителя с дифференциальным включением входов.