- •Комплексная цель третьего модуля.

- •Буферные элементы

- •Пороговые устройства. Триггеры Шмитта.

- •Формирование импульсов

- •Генераторы прямоугольных импульсов.

- •Комбинационные арифметико-логические устройства (калу)

- •Запоминающие устройства

- •Типы зу и их назначение

- •Классификация и основные характеристики полупроводниковых зу

- •Постоянные запоминающие устройства

- •Наращивание размерности блока постоянной памяти

- •Некоторые интегральные микросхемы пзу

- •Динамическое питание пзу

- •Статические оперативные запоминающие устройства

- •Некоторые интегральные микросхемы статических озу

- •Наращивание размерности блока статического озу.

- •Динамические оперативные запоминающие устройства

- •Некоторые интегральные микросхемы дозу

- •Блок озу динамического типа

- •Наращивание размерности динамических озу

- •Регистровые озу (регистровые файлы)

- •Наращивание размерности многоадресного регистрового озу

- •Проектные задания к третьему модулю.

- •Пример выполнения заданий к третьему модулю.

- •Итоговый тестовый контроль знаний по курсу «Схемотехника эвм» Вариант № 1 Инструкция по выполнению работы

- •Желаем успеха! Часть 1

- •Часть 2

- •Список литературы

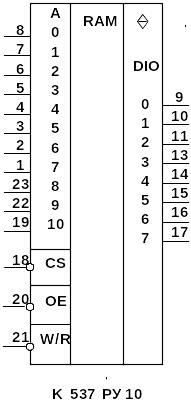

Некоторые интегральные микросхемы статических озу

|

|

|

Наращивание размерности блока статического озу.

Предположим, что в соответствии с техническим заданием необходимо разработать блок статического ОЗУ емкостью N*M, где N – число слов, М – разрядность слов, с быстродействием tвыб, потребляемой мощностью Рпотр и стоимостью С.

Процесс построения будет повторять все этапы синтеза блока ПЗУ, касающиеся выбора ИМС, определения формата блока (Кстрок * Ккол), разрядности регистра адреса, построения дешифратора адреса, подключения управляющих входов CS к выходам дешифратора адреса. Кроме того, добавляются следующие особенности.

Если используется БИС ОЗУ с матричной организацией и раздельными входами DI и выходами DO, то входы DI объединяются по столбцам в один информационный вход блока, выходы D0 также объединяются по столбцам в один информационный выход блока.

Если используется БИС со словарной организацией, то одноименные входы-выходы объединяются по столбцам и подключаются к соответствующим входам-выходам проектируемого блока ОЗУ.

Входы всех микросхем объединяются в один общий вход записи/чтения блока.

Одним из возможных вариантов подключения входов OE является их объединение в один общий вход разрешения выходов блока ОЗУ.

Наличие нескольких входов CS следует использовать для упрощения дешифратора адреса.

Пример: разработать блок статического ОЗУ емкостью 64Кх16 – разрядных слов с заданными tвыб, Рпотр, С и т.д.

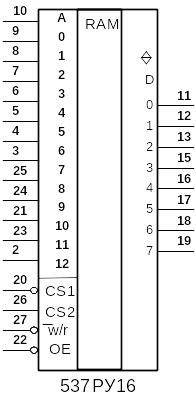

Предположим, что по большинству параметров нас устраивает микросхема КР537РУ16. n=8К, N=64К, m=8, M=16.

Определяем количество колонок и строк в проектируемом блоке статического ОЗУ:

![]()

Для построения блока памяти потребуется 16 микросхем.

Определяем разрядность адреса (число линий адреса) Na=log264К=16. Первая группа адресных входов состоит из na=13 линий, вторая группа адресных ходов состоит из 16-13=3 адресных линий, т.е. для построения блока статического ОЗУ потребуется дешифратор адреса DCA размерностью 3х8.

Сделав эти простые вычисления, можно приступить к построению схемы.

Рассмотрим назначение элементов схемы. Формирователи DD1, DD2 обеспечивают развязку наиболее нагруженных линий связи источника адреса и управляющих сигналов с блоком ОЗУ. Дешифратор адреса DD3 необходим для управления построчной выборкой микросхем ОЗУ в блоке. Элемент «И» (DD4.1) разрешает работу дешифратора при наличии обращения к блоку ОЗУ для записи или чтения информации. Позиции DD5…DD20 представлены микросхемами статического ОЗУ. Данные считываются или записываются с шины данных D0…D15.

Динамические оперативные запоминающие устройства

Динамические ОЗУ (ДОЗУ) могут иметь словарную или матричную организацию, но чаще имеют матричную. В качестве элемента памяти используется конденсатор внутри МДП – структуры. Наличие токов утечки конденсатора обусловливает необходимость периодической регенерации хранимой информации. Для отечественных микросхем период регенерации одна, две мсек. Чаще используют n-МДП структуру, так как она позволяет обеспечить более высокое быстродействие, большую емкость, меньшую потребляемую мощность. Для построения используются элементы памяти, выполненные по одно, двух или трех - транзисторной схеме.

Простейшие матричное ДОЗУ выполненное по одно-транзисторной схеме можно представить следующим образом:

Информация хранится на конденсаторах C1. С приходом сигнала выбор строки транзисторы VT1 соответствующей строки открываются, и заряд конденсатора С1 через усилитель записи/регенерации переписывается на конденсатор C2. Далее в зависимости от режима.

В режиме чтения приходит сигнал выбор столбца, открывается один из транзисторов VT3, и заряд с соответствующего конденсатора C2 попадает на выход I/O. Затем приходит сигнал запись/регенерация, значение сигналов со всех конденсаторов С2 в строке вновь восстанавливается (переписывается) на конденсатор С1.

Режим записи отличается тем, что после выбора столбца информация на конденсаторе С2 обновляется с входа I/O через открытый транзистор VT3. Затем через транзистор VT2 по сигналу запись/регенерация попадает на С1. Одновременно на остальных конденсаторах С1 выбранной строки восстанавливается прежняя информация.

В режиме регенерации сигналы выбор столбца не подаются, а по сигналу запись/регенерация регенерируется прежняя информация.

Ниже представлена структурная схема БИС ДОЗУ на примере микросхемы К565РУ5. На схеме применены следующие обозначения узлов:

ДшХ — дешифратор строк;

Дш У — дешифратор столбцов;

МЭП — матрица элементов памяти ЭП;

ГСЗ — генератор сигнала записи;

УВвИ — устройство ввода информации;

УВывИ — устройство вывода информации;

РгА — регистр адреса;

ГТС1 — первый генератор тактовых сигналов;

ГТС2 — второй генератор тактовых сигналов;

УСч — усилитель считывания;

A0..A7 – адресные входы;

DI – вход данных;

DO – выход данных;

W / R – сигнал записи-считывания;

RAS – строб адреса строк;

СAS – строб адреса столбцов.

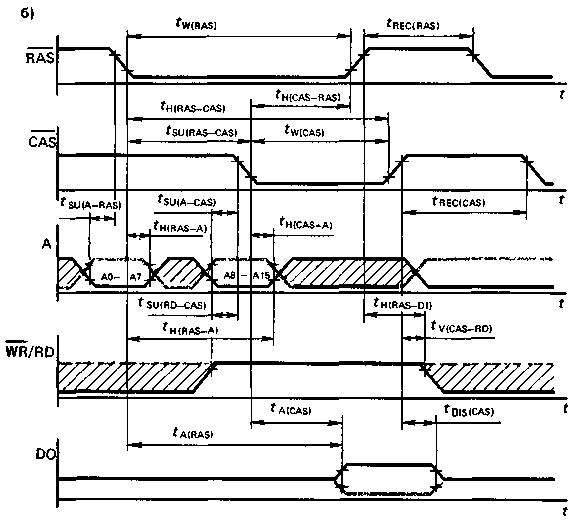

БИС динамического ОЗУ К565РУ5 представляет собой запоминающее устройство с произвольной выборкой, организованное в виде 65536 одноразрядных слов (64Кх 1). Работа микросхемы памяти инициируется при подаче двух внешних тактовых сигналов RAS и CAS, обеспечивающих с помощью ГТС1 и ГТС2 формирование внутренней временной диаграммы работы БИС ЗУ. Элементы памяти организованы в виде матрицы ЭП, состоящей из 128 строк и 512 столбцов. Для выбора любого из 65 536 элементов памяти необходимо на 8-разрядный регистр адреса подать в мультиплексном режиме (за два последовательных сообщения) 16-разрядный код адреса. При этом восемь разрядов кода адреса строк (А0—А7) принимаются на РгА с помощью сигнала RAS, а восемь разрядов кода адреса столбцов (А8—А15) — с помощью сигнала CAS. Дешифрация строк и столбцов осуществляется с помощью ДшА и ДшУ.

Условное графическое обозначение микросхемы представлено на рисунке.

Микросхема работает в следующих основных режимах: запись; считывание; считывание — модификация — запись; страничная запись; страничное считывание; регенерация.

В режиме записи после перехода сигналов RAS, W/R и CAS в активное состояние — (логический 0) входная информация DI принимается сначала на входной триггер — защелку, расположенный в УВвИ, а затем перезаписывается в выбранный ЭП. Стробом приема числа DI является тот из сигналов W/R или СAS, который позже переходит в активное состояние. При этом если сигнал W/R становится активным раньше сигнала CAS, то время установления и удержания числа DI отсчитывается от момента подачи сигнала CAS. Это так называемый режим ранней записи. В режиме поздней записи сигнал W/R задерживается относительно сигнала CAS, а время установления и удержания входных данных отсчитывается от перехода сигнала W/R в активное состояние. Наличие перечисленных режимов записи позволяет более гибко использовать ДБИС ЗУ при построении на ее основе запоминающих устройств.

Временная диаграмма работы ДОЗУ в режиме записи

В режиме считывания информация DO появляется на выходе устройства вывода информации УВывИ через время tA (RAS) после перехода сигнала RAS в активное состояние и сохраняется на выходе микросхемы памяти до тех пор, пока CAS не перейдет в состояние логической 1. Считывание информации происходит без ее разрушения. Выходная информация не инвертируется относительно записываемой.

Временная диаграмма работы ДОЗУ в режиме считывания

В режиме считывание — модификация — запись происходит считывание информации, ее модификация (изменение) в случае необходимости с последующей записью данных по одному и тому же адресу. Этот режим используется, например, в запоминающих устройствах с коррекцией ошибок или в ЗУ с побайтной записью информации. Так как длительность цикла режима считывания — модификации — записи меньше суммарной длительности циклов считывания и записи, то применение этого режима позволяет в ряде случаев улучшить технические характеристики запоминающих устройств.

Временная диаграмма работы ДОЗУ в режиме

считывание-модификация-запись

В режиме страничной записи (считывания) происходит запись (считывание) информации в ЭП, расположенных в разных столбцах одной из постоянно выбранных в пределах цикла обращения строки. В этом режиме достигается повышение быстродействия ДБИС ЗУ.

Временная диаграмма работы ДОЗУ в страничном режиме записи

Временная диаграмма работы ДОЗУ в страничном режиме считывания

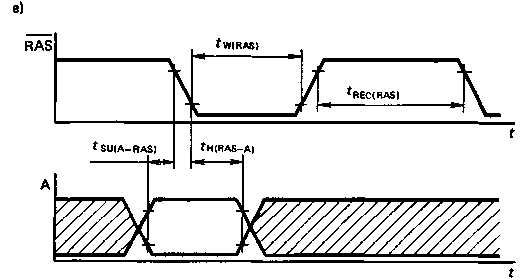

В режиме регенерации за один цикл происходит восстановление данных всех 512 элементов памяти, расположенных в пределах той строки, адрес которой соответствует коду адреса регенерации. Восстановление информации во всей ДБИС ЗУ осуществляется при периодическом переборе всех 128 строк за время, не превышающее 2 мс. В этом режиме на входы ДБИС ЗУ достаточно подать сигнал RAS и адрес строки (А0—А7).

Временная диаграмма работы ДОЗУ в режиме регенерации

Так как сигнал CAS равен при этом логической 1, то выход ДБИС ЗУ находится в состоянии высокого импеданса. Описанный режим называется только RAS. Существует еще так называемый режим скрытой регенерации.

Он реализуется, если после цикла обращения, предшествующего циклу только RAS, сигнал CAS остается в состоянии логического 0. В этом случае выход ДБИС ЗУ не меняет того состояния, в которое он установился в предыдущем цикле обращения. Эта особенность ДБИС ЗУ используется для организации скрытой регенерации, когда повторная подача сигнала RAS при активном сигнале CAS формирует цикл регенерации при сохранении на выходе ДБИС ЗУ информации, считанной в предыдущем цикле.

Из всех перечисленных режимов микросхема памяти потребляет минимальную мощность в режиме только RAS. Следует отметить также, что и при обычных циклах считывания, записи и т.д. регенерация информации также выполняется, причем в той строке ЭП, адрес которых соответствует строчной части адреса обращения.