- •Комплексная цель третьего модуля.

- •Буферные элементы

- •Пороговые устройства. Триггеры Шмитта.

- •Формирование импульсов

- •Генераторы прямоугольных импульсов.

- •Комбинационные арифметико-логические устройства (калу)

- •Запоминающие устройства

- •Типы зу и их назначение

- •Классификация и основные характеристики полупроводниковых зу

- •Постоянные запоминающие устройства

- •Наращивание размерности блока постоянной памяти

- •Некоторые интегральные микросхемы пзу

- •Динамическое питание пзу

- •Статические оперативные запоминающие устройства

- •Некоторые интегральные микросхемы статических озу

- •Наращивание размерности блока статического озу.

- •Динамические оперативные запоминающие устройства

- •Некоторые интегральные микросхемы дозу

- •Блок озу динамического типа

- •Наращивание размерности динамических озу

- •Регистровые озу (регистровые файлы)

- •Наращивание размерности многоадресного регистрового озу

- •Проектные задания к третьему модулю.

- •Пример выполнения заданий к третьему модулю.

- •Итоговый тестовый контроль знаний по курсу «Схемотехника эвм» Вариант № 1 Инструкция по выполнению работы

- •Желаем успеха! Часть 1

- •Часть 2

- •Список литературы

Постоянные запоминающие устройства

Внутреннюю структуру большинства схем однократно программируемых ПЗУ можно пояснить на примере микросхемы К556РТ7:

Входные усилители развязывают источник адреса с многочисленными приемниками адреса внутри микросхемы. В соответствии с одним из активных выходов на дешифраторе строк DCX выбирается одинаковая строка во всех матрицах накопителя М, а дешифратор столбцов DCY определяет, какую одну из этих строк передать на выход. Сигналы выборки кристалла Csi управляют режимом работы – чтение или хранение. В приведенном примере таких входов несколько и они объединены логической функцией «И».

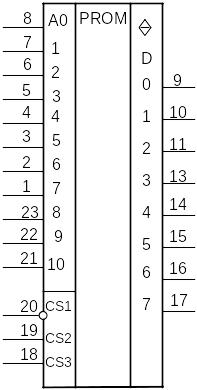

На принципиальном уровне такая микросхема обозначается следующим образом:

-

В однократно программируемых ПЗУ матрица накопитель М представляет собой ортогональные проводники, в местах пересечения которых находится полупроводниковый элемент (диод или транзистор), с последовательно включенной плавкой перемычкой.

В отсутствии плавкой перемычки (после прожигания) при поступлении сигналов по шине Х цепь эмиттера транзистора разомкнута, на выходе логический нуль. При наличии перемычки транзистор включен по схеме с общим эмиттером и при появлении потенциала на базе на выходе появится логическая единица.

Работу ПЗУ поясняет временная диаграмма:

Диаграмма определяет последовательность подачи адресного сигнала и управляющего сигнала на входе CS (выбора микросхемы). Их взаимное расположение и длительность регламентируются паспортными данными на микросхему. С некоторой задержкой относительно сигнала CS выходы переходят в рабочее состояние и информация будет готова к считыванию.

Наращивание размерности блока постоянной памяти

Предположим, что в соответствии с техническим заданием необходимо разработать блок постоянной памяти емкостью N*M, где N – число слов, М – разрядность, с быстродействием tвыб (tсчит), потребляемой мощностью Рпотр и стоимостью С. Поэтапно процесс построения можно представить следующим образом.

Выбор типа интегральной микросхемы ПЗУ по заданным N,M, tвыб, Рпотр, С и другим характеристикам.

Определение формата блока памяти. Блок памяти будет представлять собой прямоугольную матрицу размером Ккол*Кстрок. (Общее количество микросхем ПЗУ Q в блоке будет равно Q=Ккол*Кстрок, Если выбранная микросхема имеет m информационных выходов и na – адресных входов (n - слов), то

![]()

Разрядность регистра адреса определяется по формуле Na=]log2N[ с округлением в большую сторону.

Весь регистр адреса делится на две группы:

1-я группа - na (по количеству адресных входов у микросхем)

2-я группа – (Na-na)

1-я группа адресных входов подключается к адресным входам всех микросхем и в случае необходимости усиливается.

2-я группа адресных входов подключается к дешифратору адреса.

Строится дешифратор адреса, размерностью (Na-na)*Кстр. Дешифратор будет полным, если Кстр=2Na-na и неполным, если Кстр меньше.

Входы CS микросхем ПЗУ построчно объединяются и подключаются к соответствующим выходам дешифратора адреса. (Нулевая строка к нулевому выходу, первая строка – к первому выходу и т.д.). Дешифратор адреса должен управляться внешним (системным) сигналом CS. В микропроцессорных системах для этих целей используется сигнал MEMR (чтение памяти).

Одноименные информационные выходы ПЗУ объединяются по колонкам и подключаются к соответствующим выходам блока ПЗУ.

Примечания:

Если Na-na=0, то в блоке ПЗУ одна строка, а при Ккол=1 даже одна микросхема, потребность в дешифраторе адреса отсутствует.

Если Na-na=1, то в блоке ПЗУ две строки и необходим дешифратор адреса размерностью 1*2. Его можно реализовать, в том числе, на обычной логике так, как это показано ниже.

Если в микросхеме ПЗУ несколько входов CS объединенных знаком «&», то их можно рассматривать как встроенный распределенный дешифратор и использовать для упрощения (или замены) дешифратора адреса.

В качестве примера построим принципиальную схему блока ПЗУ емкостью 32К*16 – разрядных слов (N=32K, М=16) с заданными временем выборки tвыб, потребляемой мощностью Рпотр, стоимостью С и т.д. Предположим, что заданным значениям tвыб, Р,С и др. соответствует микросхема 556РТ16. Ее условное графическое обозначение представлено ниже.

С учетом сделанного выбора:

n=8К (na=13), m=8;

Всего для построения блока памяти потребуется Q=8 микросхем ПЗУ КР1556РТ16. Для адресации блока потребуется шина адреса разрядностью (регистр адреса разрядностью) Na=log232K=15.

Первая группа адресных линий равна na=13 (по разрядности адреса микросхем). Вторая группа Na-na=15-13=2. . Внешний дешифратор адреса DCA будет иметь размерность 2*4. В этом качестве может быть использован, например, дешифратор КР1533ИД4.

Проведя несложные предварительные расчеты, можно приступить к построению схемы. Схема представлена ниже.

Если представленную схему выполнить в соответствии с требованиями стандартов, в частности, без пропуска микросхем, то схема электрическая принципиальная потребует формата А3 или А2. Однако ее можно упростить, используя разрешенное «наложение» («совмещение») одинаково подключаемых полей. После такого упрощения схема окончательно примет вид:

В упрощенном варианте для микросхем DD3-DD5 и DD7-DD9 показан только вход CS, т.к. только его подключение отличается от подключения одноименного входа других микросхем. Адресное поле и поле данных микросхем DD2-DD5 и DD6-DD9 в пределах одной колонки подключается одинаково, поэтому эти поля совмещены с микросхемой DD2 в первой колонке и микросхемой DD6 во второй колонке. Упрощенный вариант схемы легко читается и требует для графического исполнения меньшего формата. Это преимущество проявляется в большей степени с увеличением количества микросхем.