- •Комплексная цель третьего модуля.

- •Буферные элементы

- •Пороговые устройства. Триггеры Шмитта.

- •Формирование импульсов

- •Генераторы прямоугольных импульсов.

- •Комбинационные арифметико-логические устройства (калу)

- •Запоминающие устройства

- •Типы зу и их назначение

- •Классификация и основные характеристики полупроводниковых зу

- •Постоянные запоминающие устройства

- •Наращивание размерности блока постоянной памяти

- •Некоторые интегральные микросхемы пзу

- •Динамическое питание пзу

- •Статические оперативные запоминающие устройства

- •Некоторые интегральные микросхемы статических озу

- •Наращивание размерности блока статического озу.

- •Динамические оперативные запоминающие устройства

- •Некоторые интегральные микросхемы дозу

- •Блок озу динамического типа

- •Наращивание размерности динамических озу

- •Регистровые озу (регистровые файлы)

- •Наращивание размерности многоадресного регистрового озу

- •Проектные задания к третьему модулю.

- •Пример выполнения заданий к третьему модулю.

- •Итоговый тестовый контроль знаний по курсу «Схемотехника эвм» Вариант № 1 Инструкция по выполнению работы

- •Желаем успеха! Часть 1

- •Часть 2

- •Список литературы

ТРЕТИЙ МОДУЛЬ

Комплексная цель третьего модуля.

Познакомиться с основами структурной и функциональной организации буферных элементов, пороговых устройств, формирователей и генераторов импульсов, комбинационных арифметико-логических устройств, полупроводниковых запоминающих устройств, а также с одноименными интегральными микросхемами в составе различных серий. Приобрести навыки построения принципиальных схем на основе различных микросхем запоминающих устройств.

Буферные элементы

Буферные элементы служат для буферирования шин и управляющих сигналов, формирования сигналов (улучшения фронтов), усиления по току, включения или выключения третьего состояния. В основном эти элементы используются для обслуживания общих шин (шины адреса, шины данных) в частности, включают или выключают приемники и передатчики сигналов от этих шин, могут инвертировать принимаемые или передаваемые сигналы.

Например, в составе серии КР1533 несколько таких схем:

В каждой из приведенных схем (1533АП3…1533АП5) по две четверки буферов-формирователей линий. Отличаются они только прямыми или инверсными выходами и прямым или инверсным входом управления тремя состояниями выходов ОЕВ. На примере 1533АП5 приведена таблица состояний, поясняющая работу схем (L- низкий уровень сигнала; H- высокий уровень сигнала; X- безразличное состояние L или H; Z- высокоомное (третье) состояние выходов).

В составе серии 1533 есть также схемы, позволяющие менять направление передачи информации в зависимости от управляющего сигнала. Например, микросхема 1533АП6.

-

EAB – вход разрешения переключения направления передачи.

ОЕ - управление третьим состоянием входов-выходов DА и DВ одновременно. Принцип работы поясняется нижеприведенной таблицей.

Пороговые устройства. Триггеры Шмитта.

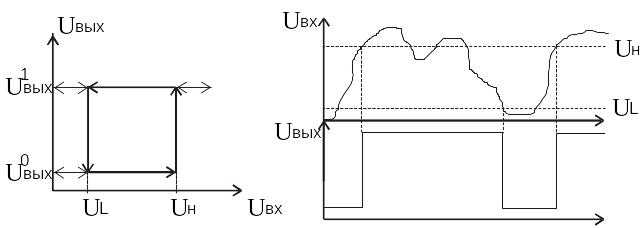

Схемы, имеющие разные уровни или пороги включения-выключения, называются триггерами Шмитта. При повышении напряжения у них один порог срабатывания UH, при понижении другой UL. В отличие от обычных триггеров они имеют один вход, могут управляться как цифровым, так и аналоговым сигналами и не обладают свойствами запоминающего элемента. Принцип работы триггера поясняют диаграммы:

Триггер Шмитта обладает гистерезисом, поэтому основное его назначение – повышение крутизны фронтов импульсов, формирование импульсов из искаженного или аналогового сигнала, построение мультивибраторов и т.д. На функциональном и принципиальном уровнях он обозначается следующим образом:

![]()

Входы триггера Шмитта могут быть дополнены логикой, например, логическим «И»:

Формирование импульсов

Устройства, формирующие короткие импульсы по фронтам входного сигнала, называют формирователями импульсов. Сформированные таким образом сигналы можно использовать для установки в ноль, записи, синхронизации и т.д. В зависимости от требуемой длительности формируемых импульсов можно использовать различные схемы.

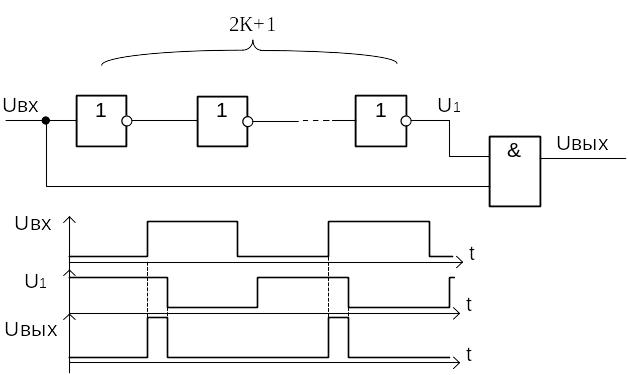

Формирователи импульсов малой длительности (десятки, сотни наносекунд) можно построить на цепочке логических элементов.

До поступления входного импульса U1=1; Uвых=0. С появлением входного импульса на втором входе элемента «И» появится логическая единица. Выходной сигнал Uвых изменится и будет равным логической единице до тех пор, пока входной сигнал не преодолеет задержку из цепочки элементов «НЕ», сменив значение U1 с единицы на ноль. Таким образом, длительность выходного сигнала определяется длительностью задержки (2К+1) элементов. Задержки микросхем имеют большой разброс и нестабильны, поэтому область применения таких формирователей ограничивается отсутствием высоких требований к стабильности длительности выходного сигнала.

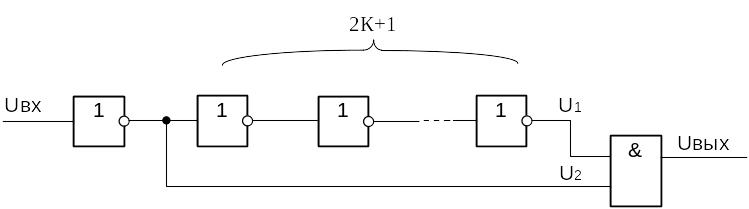

Аналогичная схема, формирующая импульсы по заднему фронту, может быть представлена следующим образом:

Схема, формирующая на выходе импульсы и по заднему и по переднему фронтам одновременно, может быть реализована с применением на выходе элемента «исключающее ИЛИ» вместо элемента «И»:

Временные диаграммы работы двух последних схем формирователей предлагается нарисовать самостоятельно.

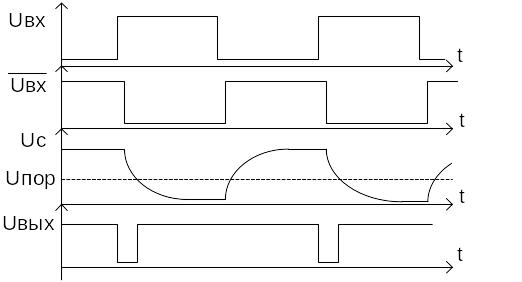

Формирователи импульсов большой длительности можно построить по тому же принципу, используя специальные элементы задержки или интегрирующие RC-цепочки. Интегрирующая цепочка ставится вместо логических элементов и, также как они, обеспечивает задержку сигнала. Величина сопротивления R в цепи для ТТЛ схем R<1 кОм, для МОП – схем десятки и сотни КОм. Например, схема формирования по переднему фронту может иметь вид:

Длительность выходного импульса в такой схеме зависит от постоянной времени зарядки конденсатора τ≈RC и ограничивается допустимыми пределами изменения значений R и С. При этом диапазон изменения выходного сигнала более широк по сравнению с предыдущими схемами, но стабильность длительности выходного сигнала по-прежнему невысокая.

Импульсы практически любой длительности, в том числе, с программируемой (настраиваемой) длительностью могут быть получены с помощью специально выпускаемых микросхем таймеров, генераторов [ ].