4. Синхронные триггеры

В цифровой схемотехнике наибольшее применение нашли синхронные (тактируемые) триггеры. Указанные триггеры имеют специальный вход «С» тактовых сигналов (Clock - часы). Восприятие входных сигналов в синхронных триггерных устройствах выполняется только во время действия тактовых сигналов. Асинхронные сигналы используются лишь для установки и сброса внутренних фрагментов в синхронных триггерных схемах.

Синхронные триггеры подразделяются на триггеры, управляемые уровнем (статические триггеры), и триггеры, управляемые фронтом тактового сигнала (триггеры с динамическим управлением).

Управление уровнем предполагает, что при одном уровне тактового сигнала триггер воспринимает входные сигналы, а при другом уровне триггер не изменяет своего состояния.

При управлении фронтом переключение триггера осуществляется только в моменты перепада тактового сигнала.

На рис. 7 показаны процессы, происходящие в синхронных триггерах, и приведены условно-графические обозначения тактовых входов различных синхронных триггеров по ГОСТ 2.743-91.

Двухступенчатые триггеры – одна из разновидностей триггеров с динамическим управлением. Разрешающим фронтом тактового сигнала двухступенчатых триггеров считается фронт, при котором выполняется перенос информации из первой ступени во вторую.

4.1 Синхронные статические триггеры

Синхронный RS-триггер со статическим управлением отличается от асинхронного RS-триггера наличием синхронизирующего входа. Таблица функционирования синхронного RS-триггера приведена в табл. 3.

Таблица 3

S |

R |

C |

Q n |

Режим |

х |

х |

0 |

Q n-1 |

Хранение |

0 |

0 |

1 |

Q n-1 |

Хранение |

1 |

0 |

1 |

1 |

Запись 1 |

0 |

1 |

1 |

0 |

Запись 0 |

1 |

1 |

1 |

з |

Запрещенный |

Входы S и R являются информационными. Сигналы на этих входах должны переключаться до поступления активного уровня синхроимпульса. Функциональную схему такого триггера (рис. 8,а) достаточно просто можно построить на базе асинхронного RS-триггера с инверсными входами. Другие методы синтеза логической структуры данного триггера, рассмотренные в разделе 3, трудоемки и не эффективны.

Рисунок 7. Временные диаграммы работы синхронных триггеров с прямым (а) и инверсным управлением уровнем (б), с прямым (в) и инверсным динамическим управлением (г), двухступенчатых триггеров с динамическим управлением (д)

Рисунок 8. Функциональная схема (а) и условно-графическое отображение (б) синхронного статического RS-триггера

Комбинационная схема управления асинхронным RS-триггером содержит два логических элемента И-НЕ. При С=0, независимо от входных информационных сигналов, на выходах схемы управления присутствуют пассивные единичные уровни сигналов, обеспечивающие режим хранения триггера. При С=1 оба логических элемента открыты для прохождения информационных сигналов, устанавливающих асинхронный RS-триггер в заданное состояние. Запрещенной комбинацией информационных сигналов является S=R=1. Условно-графическое отображение синхронного RS-триггера со статическим управлением приведено на рис. 8,б. Временная диаграмма работы триггера представлена на рис. 9.

Рисунок 9

Синхронный D-триггер со статическим управлением. В D- триггерах имеется только один информационный вход D и вход синхроимпульсов С. Функционирование триггера задается таблицей 4.

Таблица 4

D |

C |

Q n |

Режим |

х |

0 |

Q n-1 |

Хранение |

1 |

1 |

1 |

Запись 1 |

0 |

1 |

0 |

Запись 0 |

Схема D- триггера может быть получена путем соединения информационных входов синхронного RS-триггера через инвертор (рис. 10,а). В данной схеме исключается возможность поступления на входы RS-триггера запрещенной комбинации R=S=1.

Несмотря на это преимущество, D- триггер уступает RS-триггеру по быстродействию из-за дополнительной задержки информационного сигнала в инверторе. Поэтому в цифровой схемотехнике при организации регистровых схем для хранения последовательности кодовых комбинаций часто применяют RS-триггеры.

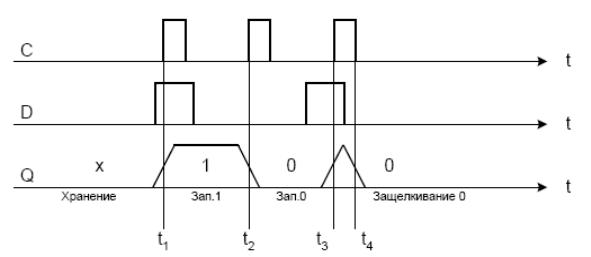

Условно-графическое отображение и временная диаграмма синхронного статического D-триггера приведены на рис. 10,б и рис. 11.

Рисунок 10

Рисунок 11

Из временной диаграммы просматривается одна особенность синхронного статического D-триггера: на временном интервале t3 – t4 в триггер записывается последнее значение информационного сигнала, соответствующее моменту завершения синхроимпульса. Такой процесс называют «защелкиванием», а синхронный D-триггер со статическим управлением называют так же «триггер-защелка». Это свойство используется в цифровых схемах для фиксации быстроизменяющейся последовательности данных в строго определенные моменты времени. Кроме того, данные триггеры часто используют для реализации цифровых линий задержки, поскольку выходная информация (выход Q) задерживается относительно входной (вход D) на период синхроимпульса.