- •2. За допомогою ключів (керуються клавішами [w] і [q]) подати на вхід схеми комбінації значень r і s. Значення виходів занести в таблицю 1.3. 10

- •Лабораторна робота № 1. Дослідження rs тригера. Тригери асинхронні і з синхронізуючим входом.

- •Основні теоретичні відомості

- •Порядок виконання роботи

- •Питання і завдання для повторення:

- •Лабораторна робота № 2. Дослідження послідовного та паралельного регістрів.

- •Основні теоретичні відомості

- •2.1 Паралельний регістр

- •2.2 Послідовний регістр

- •Порядок виконання роботи

- •2.1. Дослідження паралельного регістра.

- •2.2. Дослідження послідовного регістра

- •Питання і завдання для повторення:

- •Лабораторна робота № 3. Дослідження лічильників на jk та d тригерах.

- •Основні теоретичні відомості

- •Порядок виконання роботи

- •Питання і завдання для повторення:

- •Лабораторна робота № 4. Дослідження дешифраторів, шифраторів.

- •Основні теоретичні відомості

- •Порядок виконання роботи

- •Питання і завдання для повторення:

- •Лабораторна робота № 5. Дослідження мультиплексорів.

- •Основні теоретичні відомості

- •Порядок виконання роботи

- •Питання і завдання для повторення:

- •Лабораторна робота № 6. Дослідження Арифметико-Логічного Пристрою (алп).

- •Основні теоретичні відомості

- •Порядок виконання роботи

- •Питання і завдання для повторення:

- •Лабораторна робота № 7. Дослідження Оперативного Запам'ятовуючого Пристрою (озп).

- •Основні теоретичні відомості

- •Порядок виконання роботи

- •Питання і завдання для повторення:

- •Лабораторна робота № 8. Дослідження Постійного Запам'ятовуючого Пристрою (пзп).

- •Основні теоретичні відомості

- •Порядок виконання роботи

- •Питання і завдання для повторення:

- •Лабораторна робота № 9 Аналогo-цифрові та цифро-аналогові перетворювачі.Ацп прямогоперетворення.

- •Основні теоретичні відомості

- •Порядок виконання роботи

- •Питання і завдання для повторення:

- •Лабораторна робота № 10 Аналогo-цифрові та цифро-аналогові перетворювачіЦап сходовоготипу.

- •Основні теоретичні відомості

- •Порядок виконання роботи

- •Питання і завдання для повторення:

- •Лабораторна робота № 11 Система команд микроконтроллера pic16fxх

- •Порядок виконання роботи

- •Лабораторна робота № 12 Програмування портів вводу-виводу мікроконтролера pic.

- •Основні теоретичні відомості

- •Текст файла Project3.Asm

- •Індивідуальні завдання

- •Питання і завдання для повторення:

- •Завдання для самостійної роботи студентів Додаток а.Дослідження лічильників на jk та d тригерах .

- •6.Дослідження синхронного реверсивного лічильника

- •Додаток б.Дослідження комбінаційних схем. Базові логічні елементи.

- •Додаток в.Дослідження тригерів

- •Додаток г.Дослідження регістрів

- •Список рекомендованої літератури

Порядок виконання роботи

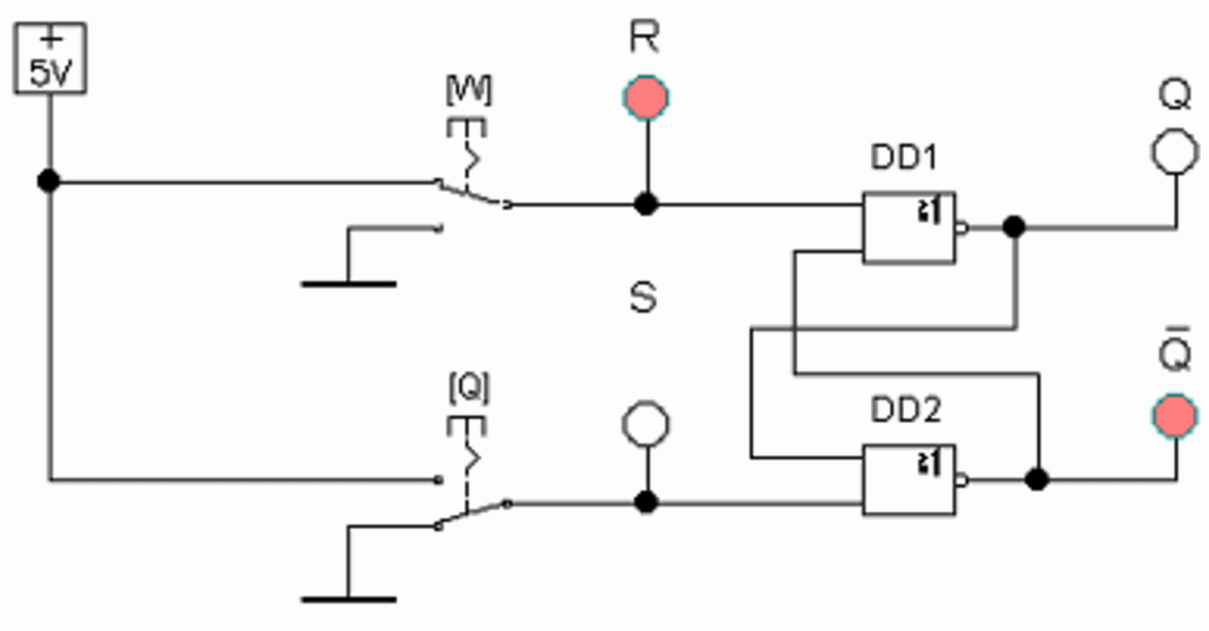

1.Зібрати схему, зображену на малюнку 1.4.

2. За допомогою ключів (керуються клавішами [W] і [Q]) подати на вхід схеми комбінації значень R і S. Значення виходів занести в таблицю 1.3.

Мал.

1.4. Схема для дослідження асинхронного

RS-тригера

Мал.

1.4. Схема для дослідження асинхронного

RS-тригера

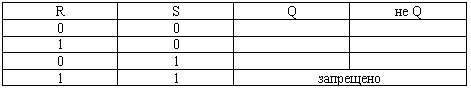

Таблиця

1.3.

Таблиця істинності синхронного

RS-тригера

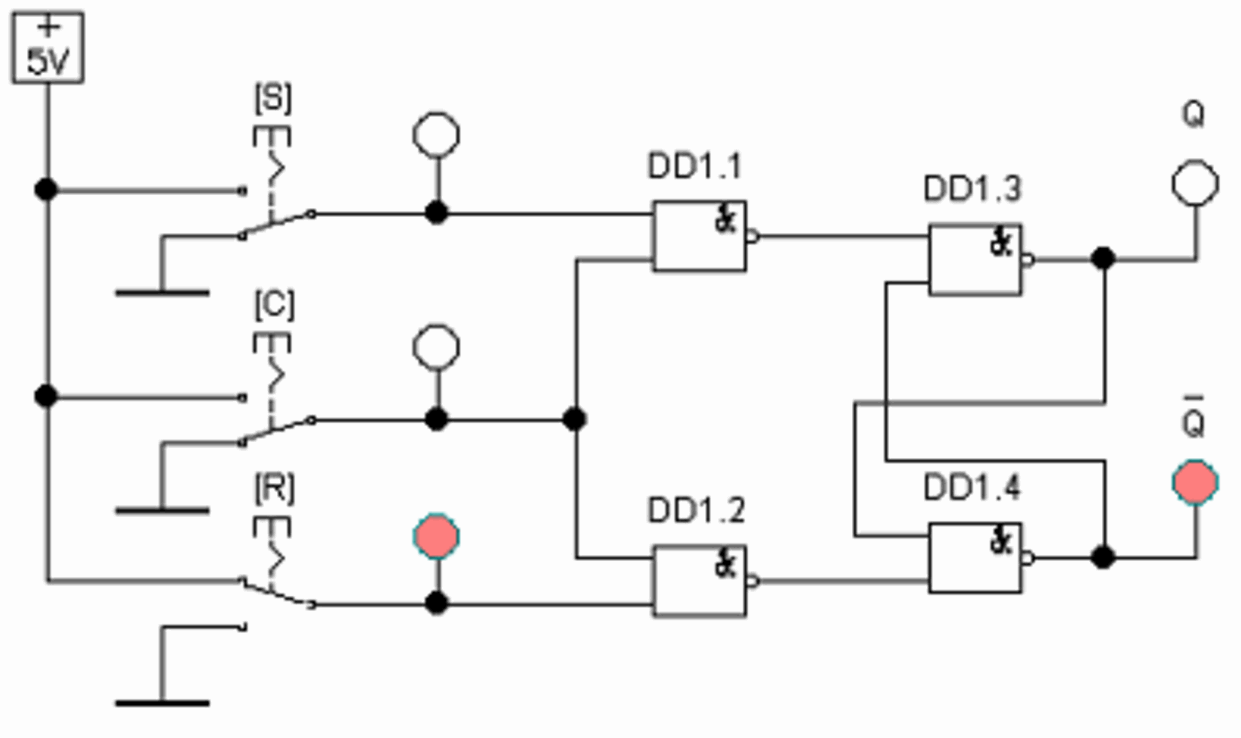

Мал.

1.5.

Схема для дослідження синхронного

RS-тригера

Мал.

1.5.

Схема для дослідження синхронного

RS-тригера

3. Зібрати схему, зображену на малюнку 1.5.

4. Проаналізувати роботу тригера в залежності від наявності логічної одиниці на тактовому вході С.

5. Зробити висновок.

Питання і завдання для повторення:

Що таке тригер? Які типи тригерів вам відомі?

Намалюйте схему RS-тригера на транзисторах, поясніть принцип її роботи.

Намалюйте схему асинхронного RS-тригера на логічних елементах. Поясніть принцип його роботи.

Намалюйте таблицю станів асинхронного RS-тригера.

Намалюйте схему синхронного RS-тригера на логічних елементах. Поясніть принцип його роботи.

Намалюйте схему D-тригера на логічних елементах. Поясніть принцип його роботи.

Розкажіть про JK-тригер і Т-тригер.

Намалюйте схему перетворення JK-тригера в Т-тригер.

Розкажіть про область застосування тригерів.

Лабораторна робота № 2. Дослідження послідовного та паралельного регістрів.

Мета:Побудова схем та вивчення принципу роботи послідовного і паралельного регістрів на D-тригерах.

Програмне забезпечення: програмне забезпечення комп'ютерного моделювання електронних схем (програма Electronic Workbench).

Основні теоретичні відомості

Регістром називається послідовнісний цифровий пристрій, що використовується для запису і зберігання n-розрядного двійкового слова. Крім зберігання деякі види регістрів можуть перетворювати інформацію, наприклад, з паралельної в часі форми подання (паралельний код) в послідовну (послідовний код) і навпаки; з прямого коду в зворотний і навпаки; зрушувати інформацію на один або декілька розрядів в сторону молодшого або старшого розрядів.

Регістри будуються на базі тригерів, число тригерів у схемі регістра відповідає числу розрядів двійкового слова, що підлягає зберіганню. Розряди регістра крім тригерів можуть містити й деякі ЛЕ, за допомогою яких забезпечується можливість виконання перерахованих вище перетворень інформації. Основним класифікаційним ознакою регістрів є спосіб прийому (записи) та видачі (читання) інформації. За цією ознакою розрізняють паралельні, послідовні та паралельно-послідовні регістри.

2.1 Паралельний регістр

Паралельним називають регістр, в який n-розрядне двійкове слово записується одночасно по всіх n розрядів. Аналогічним чином здійснюється зчитування зберігається в регістрі слова - одночасно по всьому його розрядами. При зчитуванні інформація, що зберігається в регістрі, зберігається, тобто видається її копія. Паралельний регістр часто іменують регістром пам'яті. Основу регістрів пам'яті складають одноступінчасті синхронні D-або RS-тригери. У цій якості можуть застосовуватися і JK-тригери, але їх можливості більше, ніж потрібно для регістрів пам'яті. Приклад схемної реалізації чотирирозрядний регістра пам'яті наведено на мал. 2.1.

Мал. 2.1. Регістр пам'яті: а) схема, б) умовне зображення

Як

елементи регістра тут використані

синхронні D-тригери. Зі схеми випливає,

що окремі розряди регістра пам'яті не

обмінюються даними між собою. Спільними

для розрядів регістра є ланцюга

управління: синхронізації або дозволу

запису (С) і скидання або початкової

установки "0". З принципу роботи

синхронного D-тригера випливає, що

розряди числа

А=а3а2а1а0запишуться

у відповідні тригери Тільки після подачі

сигналу (імпульсу) на вхід синхронізації

С, тоб при С = 1. Після Зміни сигналу на

вході С на "0" тригери переходять

в режим зберігання. У цю годину на входь

D тригерів можна подати таке слово,

наприклад, В=b3b2b1b0,

яке

при появі сигналу С = 1 запишеться в

регістр. Зчитування слова здійснюється

з прямих () виходів тригерів (можливо

зчитування і з інверсних виходів -![]() ).

Для

установки тригерів в нульовий стан

застосовується спеціальна шина "Уст.

"0", пов'язана з асинхронними

R-входами кожного тригера.

).

Для

установки тригерів в нульовий стан

застосовується спеціальна шина "Уст.

"0", пов'язана з асинхронними

R-входами кожного тригера.