- •Курсовая работа

- •Содержание. Введение…………………………………………………………...………………3

- •Введение.

- •Теоретическая часть

- •Микропроцессор кр580вм80а

- •Тактовый генератор кр580гф24.

- •Т аймер кр580ви53

- •Дешифратор

- •Практическая часть

- •Структурная схема устройства

- •Описание работы алгоритма и блок-схема программы

- •Программа и её распределение по ячейкам памяти

- •Расчет емкости требуемой памяти и времени выполнения программы

- •Заключение.

- •Список использованной литературы.

МИНИСТЕРСТВО

ОБРАЗОВАНИЯ РОССИЙСКОЙ ФЕДЕРАЦИИ

МИНИСТЕРСТВО

ОБРАЗОВАНИЯ РОССИЙСКОЙ ФЕДЕРАЦИИ

КАЗАНСКИЙ НАЦИОНАЛЬНЫЙ ИССЛЕДОВАТЕЛЬСКИЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ им. А.Н.Туполева

Институт Радиоэлектроники и телекоммуникаций

Кафедра Радиоэлектронных и телекоммуникационных систем

Курсовая работа

на тему:

«Устройство обработки запросного кода»

Выполнил: студент гр. 5306 Подкурков И.А.

Проверил ассистент каф. РТС Галимзянов Э.Р.

Казань 2013.

Содержание. Введение…………………………………………………………...………………3

Теоретическая часть

Микропроцессор КР580ВМ80А……………………….….………….4

Тактовый генератор КР580ГФ24………………...……..…….………6

Таймер КР580ВИ53………………………………...……….………...7

Дешифратор…………………………………….….………..…………8

Практическая часть

Структурная схема устройства……….………………………………9

Описание работы алгоритма и блок-схема программы …………..10

Программа и её распределение по ячейкам памяти .…………..…13

2.4 Расчет емкости требуемой памяти и времени выполнения программы…………………………..…………………………………...…..16

Заключение ………………………………………………………...……17

Список использованной литературы……………………………..……..17

Введение.

В данной курсовой работе разработано устройство обработки запросного кода. Данное устройство работает по следующему принципу: если на вход устройства поступает запросный код – последовательность импульсов определённой формы, то устройство формирует на выходе ответный код – также последовательность импульсов определённой формы.

Система состоит из центрального микропроцессора КР580ВМ80А, тактового генератора КР580ГФ24, двух двунаправленных шинных формирователей КР580ВА86, системного контроллера КР580ВК28, дешифратора и двух таймеров КР580ВИ53.

Теоретическая часть

Микропроцессор кр580вм80а

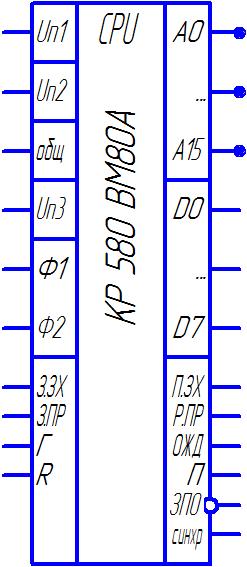

Данный микропроцессор представляет собой однокристальный микропроцессор с тремя шинами: шестнадцатиразрядная шина адреса, двунаправленная восьмиразрядная шина данных, двенадцатиразрядная шина управления. Условно-графическое обозначение приведено на рис.1.

Рис.1 УГО МП КР580ВМ80А.

-

шина адреса с тремя состояниями, которая

предназначена для обращения к любой из

216

ячеек памяти или портам ввода/вывода.

-

шина адреса с тремя состояниями, которая

предназначена для обращения к любой из

216

ячеек памяти или портам ввода/вывода.

-

шина данных с тремя состояниями, которая

предназначена для обмена данными между

микропроцессором и периферийными

устройствами.

-

шина данных с тремя состояниями, которая

предназначена для обмена данными между

микропроцессором и периферийными

устройствами.

П.ЗХ (подтверждение захвата) - единичный сигнал на этом выходе появляется в ответ на единичный сигнал, посылаемый от внешних устройств. При этом микропроцессор переходит в состояние «Захват», при котором ША и ШД переводятся в высокоомное состояние и микропроцессор отключен от всех шин. Эта особенность используется для реализации режима прямого доступа к памяти.

Р.ПР (разрешение прерывания) - на этот выход выдается состояние внутреннего триггера разрешения прерывания. Если на выходе РПР логическая единица, то микропроцессор способен воспринимать запросы на прерывание. Установка РПР осуществляется с помощью команд – EI (разрешить прерывание = уст. 1) и DI (запретить прерывание = сброс в 0). Запрос на прерывание не будет восприниматься, если не установлена 1, т.е. триггер или микропроцессор находится в состоянии «захват».

ОЖД (ожидание) - единичный сигнал на этом выходе информирует о том, что микропроцессор находится в состоянии ожидания, при котором остановлен процесс обработки.

(запись)

- нулевой сигнал на этом выходе указывает

на то, что данные микропроцессора

выставлены на шину данных и могут быть

восприняты внешними устройствами.

(запись)

- нулевой сигнал на этом выходе указывает

на то, что данные микропроцессора

выставлены на шину данных и могут быть

восприняты внешними устройствами.

(прием)

- единичный сигнал указывает на то, что

микропроцессор готов к приему данных.

(прием)

- единичный сигнал указывает на то, что

микропроцессор готов к приему данных.

Синхр. - синхросигнал появляется на этом выходе в начале каждого машинного цикла.

Г (готов) - единичный сигнал на этом выходе приводит микропроцессор в режим обработки данных. При логическом нуле микропроцессор переходит в состояние ожидания, информируя об этом единицей на выходе ОЖД.

R (сброс) - единичный сигнал обнуляет программный счетчик, внутренние регистры прерывания и захвата. Состояние регистров блока РОН при этом не меняется.

З.ЗХ (HLD) – запрос захвата. Запрос на захват поступает от внешних устройств уровня логической единицы.

З.ПР (INT) – запрос прерывания. Запрос на прерывание поступает от внешних устройств и будет восприниматься только тогда, когда будет установлен в единицу внутренний триггер разрешения прерываний. Запрос не будет восприниматься, если МП находится в состоянии «захват» или на выходе Р.ПР установлен «0».

Ф1 и Ф2 - входы тактового генератора.

Динамика работы МП КР580ВМ80А следующая. Выполнение каждой команды в микропроцессоре производится в определенной последовательности, определенным кодом команды и синхронизируется во времени сигналами Ф1, Ф2 тактового генератора. Период синхросигналов Т1 и Т2 – называется машинным тактом. Длительность машинного такта устанавливается произвольно в пределах 0,5-1,6 мкс, что соответствует частоте 2 МГц-600 кГц.