- •Передмова

- •Intel 430lx

- •Intel 430nx

- •Intel 430fx

- •Intel 430hx

- •Intel 430vx

- •Intel 430tx

- •Intel 450gx/kx

- •Intel 440fx

- •Intel 440lx agPset

- •Intel 440ex

- •Intel 440bx agPset

- •Заняття 1. Поняття про систему переривання пеом

- •Принципи організації системи переривання програм

- •Слово стану процесора (програми)

- •Характеристики системи переривання

- •Організація переходу до перериваючої програми та пріоритетне обслуговування запитів переривання

- •Процедура переривання з опитуванням джерел (прапорців) переривання

- •Програмно-керований пріоритет перериваючих програм

- •Методи використання механізму переривань

- •Класи переривань пеом

- •Призначення контролера апаратних переривань пеом

- •Опис основних елементів і8259а

- •Стани програмованого контролера переривань

- •Заняття 5. Керування режимами роботи пкп

- •Void main (void){

- •Int mask;

- •Заняття 6. Керування пріоритетами переривань

- •Install proc near

- •Заняття 8. Особливості практичного використання апаратних та програмних переривань

- •Volatile long ticks;

- •Void main(void) {

- •Void _interrupt _far timer(void) {

- •Int8 proc near cli

- •Int09 proc near

- •Розділ 3. Підсистема таймера та годинника реального часу

- •Заняття 3. Системні засоби програмного доступу до ресурсів таймера

- •Void tm_delay(int ticks) {

- •Void main (void){

- •Void main(void){

- •Заняття 4. Приклади використання функціональних можливостей таймера в прикладних задачах

- •Void main(void){ int Frac; char k;

- •Void tm_sound(int freq, int time) {

- •Void tm_delay(int ticks) {

- •Void tm_sound(int freq, int time){

- •Void main(){

- •Void main() { int I,j; clrscr();

- •Заняття 5. Архітектура та принципи функціонування годинника реального часу

Intel 450gx/kx

Набори мікросхем Intel 450GX/KX (Orion) були розроблені для перших процесорів Pentium Pro. Chipset Intel 450GX призначений для застосування на серверах. Він підтримував 8 Гб оперативної пам'яті та дві незалежні шини РСІ. На сьогодні це поки що єдиний Chipset, що підтримує 4 процесори. Chipset Intel 450KX призначався для встановлення на материнські плати PC, що виконують функцію «автоматизованого робочого місця». Цей Chipset підтримував два процесори та пам'ять об'ємом до 1 Гб.

У наш час Ви навряд чи побачите ці Chipset, але слід сказати, що вони фактично стали стандартом Chipset для серверів. Та невдовзі був розроблений Chipset 440 FX (Natoma).

Intel 440fx

На сьогодні переважна кількість системних плат використовує Chipset 440FX (Natoma). В Chipset Natoma усунені деякі технологічні недоліки Chipset Orion, крім того, він дешевший.

Основним недоліком Chipset Natoma є те, що він не підтримує останні технологічні новинки (пам'ять SDRAM, шину AGP та ін.), тому фірма випустила нові набори мікросхем — Intel 440LX та Intel 440BX.

Intel 440lx agPset

Chipset Intel 440LX AGPset повинен стати фундаментальною апаратною основою нового класу PC на базі Slot 1, що орієнтовані на обробку ЗБ-графіки та відеоданих.

Chipset підтримує шини AGP та USB, прискорений доступ до модулів пам'яті SDRAM, дозволяє оснастити сучасні PC засобами підтримки технології Plug&Play та інтерфейсом для контролю за енергоспоживанням (ACPI). Підтримка інтерфеиса ACPI дозволяє виробникам PC доповнити свою продукцію сітьовими функціями віддаленого керування енергоспоживанням, виводу PC з неактивного стану або підтримка його в постійно активному (AlwaysOn) режимі.

Набір мікросхем Intel 440LX AGPset дає можливість розробникам створювати продукти, що відповідають сучасним вимогам для роботи з мультимедіа, з недорогими PC. Набір мікросхем розширює можливості AGP за рахунок підтримки високошвидкісної пам'яті SDRAM.

Chipset складається з двох мікросхем — контролера PCI/AGP Controller (РАС) та акселератора PCI/ISA/IDE Accelerator (PIIX4).

Intel 440ex

Chipset 440EX розроблений корпорацією Intel спеціально для процесора Celeron та орієнтований на використання в недорогих системних платах для домашніх PC. Цей Chipset є спрощеною версією Chipset 440LX AGPset. Зокрема, Chipset 440EX не підтримує роботу кількох процесорів і більше трьох слотів РСІ, не забезпечує контроль за ларитетом, обмежує об'єм оперативної пам'яті до 256 Мб.

Intel 440bx agPset

Через півроку після появи Chipset Intel 440LX AGPset корпорація Intel випустила новий продукт — Intel 440BX AGPset. Цей Chipset призначений для системних плат, орієнтованих на роботу з CPU Pentium II з тактовою частотою 350, 400 МГц та більше. Основна його відмінність від Chipset 440LX полягає в тому, що тактова частота системної шини збільшена з 66 МГц до 100 МГц та забезпечена підтримка двох процесорів. У табл. 1.2 наведені основні характеристики Chipset шостого покоління, випущених корпорацією Intel. Зверніть увагу, що, оскільки кеш-пам'ять другого рівня процесорів Pentium Pro та Pentium II встановлена на ядрі або платі процесора, її об'єм не залежить від типу Chipset.

У табл. 1.2 наводяться деякі характеристики чипсетів 82440 фірми Intel для процесорів класу Pentium PRO, Pentium II, Celeron. На рис. 1.10 зображена структурна схема системної плати на базі чипсета Triton 440BX AGPset

Таблиця 1.2 Основні характеристики чипсетів для процесорів класу Pentium PRO, Pentium II, Celeron

Підтримувані функції |

i440FX |

i440LX |

І440ЕХ |

І440ВХ |

1 |

2 |

3 |

4 |

5 |

Кількість підтримуваних процесорів |

2 |

2 |

1 |

2 |

Тактова частота системної шини, МГц |

60-66 |

60-66 |

60-66 |

66-100 |

DRAM: Максимальний об'єм, Мбайт Контроль PARITY Виявлення та виправлення помилок, ЕСС Тип пам'яті Тип модуля пам'яті |

1000 + + FPM, EDO, BEDO SIMM, DIMM |

1000 + + EDO, SDRAM SIMM, DIMM |

256 EDO, SDRAM SIMM, DIMM |

1000 + + EDO, SDRAM SIMM, DIMM |

Кількість каналів IDE/ATA |

2 |

2 |

2 |

2 |

Підтримка AGP |

- |

+ |

+ |

+ |

Наявність контролера USB |

+ |

+ |

+ |

+ |

Версія РСІ |

2.1 |

2.1 |

2.1 |

2.1 |

Підтримка Plug&Play |

+ |

+ |

+ |

+ |

Режим РІО |

4 |

4 |

4 |

5 |

|

2 |

3(Ultra DMA) |

3(Ultra DMA) |

3(Ultra DMA) |

|

+ |

+ |

+ |

+ |

Питання для самоконтролю знань

Які функціональні елементи оточення процесора входять до складу чипсета І82430?

Які задачі розв'язує чипсет в архітектурі системної плати?

Скільки та які мікросхеми входять у набір І82430?

Які функції виконує системний контролер TSC 82437FX?

Які функції виконує міст РІІХ (РСІ IDE ISA Xcelerator)?

6. Як

залежать параметри системної плати від

типів контролерів

гнучких дисків, інтерфейсних портів,

клавіатури,

CMOS

RTC.

6. Як

залежать параметри системної плати від

типів контролерів

гнучких дисків, інтерфейсних портів,

клавіатури,

CMOS

RTC.

7. Які чипсети входять до групи чипсетів п'ятого покоління?

8.Дайте коротку характеристику чипсетів п'ятого покоління.

9.Які чипсети входять до групи чипсетів шостого покоління?

10.Дайте коротку характеристику чипсетів шостого покоління.

11.Які конфігурації системної плати підтримують чипсети шостого покоління?

Резюме

Чипсет (Chipset) — це набір мікросхем, встановлених на системній платі для забезпечення обміну даними між CPU та периферійними пристроями. Chipset визначає функціональні можливості системної плати: тип встановлюваних процесорів, тип та об'єм оперативної та кеш-пам'яті другого рівня, тактову частоту системної шини, підтримувані шини та ін.

Чипсет розв'язує такі задачі:

обслуговування керуючих та конфігураційних сигналів процесора;

мультиплексування адреси та формування керуючих сигналів динамічної пам'яті, зв'язок шини даних пам'яті з локальною шиною;

формування керуючих сигналів вторинного кеша, порівняння його тегів з поточною адресою звертання на локальну шину;

забезпечення когерентності (узгодженості) даних в обох рівнях кеш-пам'яті та основної пам'яті при звертанні як з боку процесора (процесорів), так і від контролерів шини РСІ;

зв'язок мультиплексованої шини адреси та даних шини РСІ з локальною шиною процесора та шиною динамічної пам'яті;

формування керуючих сигналів шини РСІ, арбітраж контролерів шини.

РПХ є багатофункціональним пристроєм, на який покладено такі функції:

організація мосту між шинами РСІ та (E)ISA з узгодженням частот синхронізації цих шин;

реалізація високопродуктивного, звичайно двоканального інтерфейса ATA (AT Attachment, інтерфейс підключення пристроїв IDE до комп'ютера), підключеного до шини РСІ;

реалізація стандартних системних засобів вводу/ виводу — двох контролерів переривань, двох контролерів прямого доступу до пам'яті, триканального системного лі-чильника-таймера, каналу керування динаміком, логіки немаскованого переривання;

комутація ліній запитів переривання шин РСІ та ISA, а також вмонтованої периферії на лінії запитів контролерів переривань, керування їх чуттєвістю (за перепадом або рівнем), обслуговування переривання від співпроцесора;

комутація каналів прямого доступу до пам'яті;

підтримка режимів енергозбереження — обробка SMM, програмування подій керування споживанням, керування частотою процесора (використовуючи сигнал STPCLK#), перемикання режимів;

реалізація мосту з внутрішньою шиною X-Bus, що використовується для підключення мікросхем контролера клавіатури, BIOS, CMOS RTC, контролерів гнучких дисків та інтерфейсних портів;

реалізація контролера USB.

У чипсеті Intel 82430FX, наприклад, ці функції (крім контролера USB) виконує мікросхема 82371FB. Реалізація перелічених функцій впливає на такі параметри системної плати, як:

продуктивність шини ISA (міст PCI-ISA використовує буферизацію запитів операцій);

продуктивність, число каналів ATA (AT Attachment, інтерфейс підключення пристроїв IDE до комп'ютера AT), можливі режими звертання (якщо режими РЮ (Programming Input/Output, програмований ввід/вивід) Mode 3 або 4 підтримують майже всі чипсети, АТА-33 ще не дуже розповсюджений);

гнучкість системи керування енергоспоживанням;

гнучкість конфігурування системних ресурсів та підтримка Р&Р (Plug and Play, «під'єднуй та працюй» — стандарт програмної настройки конфігурації пристроїв, що підключаються);

гнучкість керування адресацією ROM BIOS, що дозволяє використовувати великий об'єм коду, що зберігається, не займаючи лишнього простору у верхній пам'яті.

Ваш наступний крок

Ви отримали базові знання про ядро обчислювальної системи — системної плати та про її функціональні елементи. Від знання принципів організації та функціонування системної плати залежить розуміння роботи всього комп'ютера; Ви зможете кваліфіковано вибрати конфігурацію системного блока, виконати оптимізацію при його настройці.

Тепер можна перейти до закріплення пройденого матеріалу. Виконайте всі запропоновані вправи. Уважно вивчіть проблеми, які можуть виникнути при практичному використанні функціональних можливостей апаратних засобів системної плати. При розв'язанні практичних задач буде краще, якщо Ви запропонуєте кілька альтернативних варіантів та дасте повну характеристику кожному з них.

Закріплення матеріалу

Основні положення

У розділі 1, «Типова базова архітектура системних блоків ПЕОМ» розглянено архітектурні особливості системних блоків ПЕОМ, побудованих на базі 32-розрядних мікропроцесорів, починаючи з процесорів класу І80368 та закінчуючи процесорами Pentium II.

Незважаючи на різноманітність структур моделей ПЕОМ/386, архітектурно вони практично однакові: програмно сумісні, базуються на архітектурі процесора І386, використовують функціонально подібні ОС — MS-DOS, мають у своєму складі практично однакові комплекти ВІС оточення: контролер переривання, контролер ПДП, таймер, задаваль-ний генератор, паралельний та послідовний порти вводу/виводу і т. п. Специфіка визначається типами системних інтерфейсів, конкретними типами мікросхем оточення, типом оперативної пам'яті (швидкодія, способи кешування, об'єм), додаткової до базової периферії і т. п.

Основна обчислювальна продуктивність ПЕОМ забезпечується базовим процесором І386 (32-розрядним, з робочою тактовою частотою 16 МГц) та співпроцесором І387. На системній платі є:

розетка для підключення співпроцесора І287 (16-роз-рядний, тактова частота 4/8 МГц — настройка апаратна);

розетка для підключення співпроцесора І387 (32-роз-рядний, тактова частота 16 МГц).

Характеристики високошвидкісної локальної шини визначають час вибірки кодів з пам'яті та включають:

тип протоколу — синхронний;

робоча частота — 16 МГц;

режим використання ЛІП процесором — монопольний;

адресний простір оперативної пам'яті — 16 Мбайт (використовується 24-розрядна адресна шина);

підтримує конвеєрний режим процесора та поза-процесорні звертання з боку АТ-шини;

забезпечує узгодження роботи модулів основної пам'яті різної швидкодії за рахунок введення додаткових станів очікування мікропроцесора;

забезпечує можливість підключення одного модуля пам'яті з розмірами АТ-адаптера.

Продуктивність обчислювальної системи на базі високошвидкісних процесорів значною мірою залежить від швидкісних характеристик оточення процесора. Підвищення продуктивності мікросхем оточення за рахунок підвищення тактової частоти обмежується значним територіальним розміщенням на системній платі. Важливим кроком у розв'язанні цієї проблеми було розроблення багатофункціональних ВІС, на одному кристалі яких розміщують практично всі основні елементи оточення процесора. Такою мікросхемою є багатофункціональний контролер І82380. У складі цього пристрою реалізовано:

восьмиканальний контролер ПДП;

логічні схеми системного скидання;

20-ти рівневий програмований контролер переривання (функціональне розширення каскадно ввімкнених І82С59А);

чотириканальний 16-розрядний таймер;

програмований генератор зі станом очікування;

контролер регенерації динамічного ОЗП;

схеми арбітражу внутрішньої шини.

Для підвищення продуктивності обчислювальних пристроїв на базі 32-розрядних процесорів у їх архітектуру ввели систему кешування основної пам'яті.

Системам кеш-пам'яті властиві переваги як статичних, так і динамічних запам'ятовуючих пристроїв. Запам'ятовуючі пристрої статичного типу характеризуються високою швидкодією, що дозволяє повною мірою реалізувати швидкісні можливості системної шини, але вартість цих мікросхем достатньо висока. Схеми динамічної пам'яті дешевші, але менш швидкодіючі. Але хоча час вибірки для запам'ятовуючих пристроїв динамічного типу досягає 50-60 не, цього недостатньо, щоб перевершити статичні ОЗП. У системах кеш-пам'яті використовуються статичні запам'ятовуючі пристрої звичайно невеликого об'єму в якості пам'яті з безпосередньою вибіркою; основний об'єм пам'яті відводиться під динамічні ОЗП в якості вторинної пам'яті. Такий підхід дозволяє імітувати всю систему пам'яті як швидкодіючий запам'ятовуючий пристрій. У результаті отримується система пам'яті, що характеризується швидкодією статичних ОЗП та вартістю ОЗП динамічного типу.

У сучасних комп'ютерах кеш звичайно будується за дворівневою схемою. Первинний кеш (LI Cache) вмонтовано в усі процесори класу 486 та старші, він є і в деяких моделях 386. Об'єм його невеликий (8-32 Кбайт), та для підвищення продуктивності часто використовується роздільне кешування команд та даних. Швидкодію внутрішніх кешів можна порівняти з швидкодією регістрів процесора. Вторинний кеш (L2 Cache), як правило, встановлюється на системній платі. Типовим для комп'ютерів на процесорах класу 486 вважається об'єм кеша 64-256 Кбайт, для Pentium — 256-512 Кбайт. У процесорах Pentium Pro синхронний L2 Cache розміщений в одному корпусі з процесором та працює на його внутрішній частоті. Найбільш суттєвою відмінністю організації роботи кеш-пам'яті є способи запису та вибірки кодів. У сучасних комп'ютерах найчастіше використовуються три способи організації кеш-пам'яті: асоціативний, з прямим відображенням та комбінований або множинно асоціативний.

Взаємодія між компонентами та пристроями PC, підключеними до різних шин, здійснюється за допомогою так званих мостів, реалізованих на одній з мікросхем Chipset.

Чипсет (Chipset) — це набір мікросхем, встановлених на системній платі для забезпечення обміну даними між CPU та периферійними пристроями. Chipset визначає функціональні можливості системної плати: тип встановлювальних процесорів, тип та об'єм оперативної та кеш-пам'яті другого рівня, тактову частоту системної шини, підтримувані шини та ін.

Чипсет розв'язує такі задачі:

обслуговування керуючих та конфігураційних сигналів процесора;

мультиплексування

адреси та формування керуючих сигналів

динамічної пам'яті, зв'язок шини даних

пам'яті з локальною шиною;

мультиплексування

адреси та формування керуючих сигналів

динамічної пам'яті, зв'язок шини даних

пам'яті з локальною шиною;

формування керуючих сигналів вторинного кеша, порівняння його тегів поточною адресою звертання на локальній шині;

забезпечення когерентності (узгодженості) даних в обох рівнях кеш-пам'яті та основної пам'яті при звертанні як з боку процесора (процесорів), так і від контролерів шини РСІ;

зв'язок мультиплексованої шини адреси та даних шини РСІ з локальною шиною процесора та шиною динамічної пам'яті;

формування керуючих сигналів шини РСІ, арбітраж контролерів шини.

Одним із найбільш «популярних» у виробників системних плат є чипсет Intel 430 НХ.

Chipset Intel 430 НХ (Triton 11) складається з двох мікросхем: 82439 НХ та 82371 SB. Розглянемо докладніше їх характеристики та призначення.

82439 НХ називається системним контролером (ТХС). Він виконує дві основні задачі: забезпечує зв'язок між системною шиною CPU Pentium та шиною РСІ, а також здійснює взаємозв'язок з контролером РСІ IDE/ISA Xcelerator (PIIX3), який є другою мікросхемою набору 82371 SB. Системний контролер керує роботою оперативної пам'яті та кеш-пам'яті другого рівня. Завдяки вдосконаленням мікросхема 82439 НХ може підтримувати 512 Мб оперативної пам'яті.

Системний контролер забезпечує підтримку до чотирьох пристроїв IDE (вінчестерів, CD-ROM та ін.). Максимальна швидкість передачі по шині РСІ для операцій читання досягає 112 Мб/с, а для запису — 121 Мб/с.

82371 SB

Цей елемент називають контролером РСІ IDE/ISA Xcelerator, тому що він служить мостом (PCI-to-ISA) для даних та керуючих сигналів, що пересилаються по шинах РСІ та ISA. Крім того, ця мікросхема забезпечує роботу шини Universal Serial Bus для зовнішньої периферії та підтримку технології Plug&Play. У цій мікросхемі також інтегровані всі пристрої, необхідні для забезпечення функціонування систем з шиною ISA,— 7-канальний контролер DMA на базі вдосконалених каскадно ввімкнених контролерів 82С37А, два каскадно ввімкнені контролери переривань типу 82С59А, таймер, годинник реального часу (RTS), декодер керуючих сигналів BIOS та контролер клавіатури.(Ш)

Перевірочна робота

Вправа 1. Закінчіть фразу

Зіставте початок фрази з лівої колонки з найбільш відповідним її кінцем з колонки справа. Вибравши варіант, закінчіть фразу. Кожний пункт правої колонки можна використовувати тільки один раз.

1. КСШ виконує |

А) доступ мікропроцесора до системної периферії |

2. До складу КСШ входять: |

В) автономні вузли, що розміщуються на системній платі комп'ютера |

3. За допомогою блока керування КСШ здійснюється |

С) узгодження алгоритмів роботи, частот та форматів даних 32-розрядної ЛШ, 8/16-роз-рядної АТ-шини та її 8-розрядного відгалуження (Х-шини) |

4. Обладнання СП забезпечує: |

D) узгодження роботи модулів основної пам'яті різної швидкодії за рахунок введення додаткових станів очікування мікропроцесора |

5. Високошвидкісна локальна шина забезпечує |

Е) 7 каналів ПДП; 15 каналів маскованих переривань; 3 канали таймера; годинник реального часу з автономним джерелом живлення; підключення ІВМ-сумісної клавіатури |

6. До складу багатофункціонального контролера І82380 входять: |

F) порт вводу/виводу — порт вводу/виводу; пам'ять - пам'ять; порт вводу/виводу -пам'ять; пам'ять - порт вводу/виводу |

7.Контролер І82380 |

G) контролер регенерації динамічного ОЗП |

8. У підпорядкованому режимі І82380 |

Н) звичайно будується за дворівневою схемою |

9. ПДП-контролер у складі І82380 може підтримувати обмін даними таких типів: |

І) восьмиканальний контролер ПДП; логічні схеми системного скидання; 20-ти рівневий програмований контролер переривання (функціональне розширення каскадно ввімкнених І82С59А); чотириканальний 16-розрядний таймер; програмований генератор зі станом очікування; контролер регенерації динамічного ОЗП; схеми арбітражу внутрішньої шини |

10. У складі контролера І82380 передбачено |

J) підключається безпосередньо до локальної шини процесора І386 |

11. Зовнішні кеші є |

К) конвертер шини даних; буферні підсилювачі та регістр адреси; блок керування локальною шиною, АТ-шиною та Х-шиною |

12. У сучасних комп'ютерах кеш |

L) контролює лінії стану та керування процесора |

Вправа 2. Оберіть правильну відповідь

Завдання 1. Вкажіть призначення функціональних елементів, перелічених у колонці справа.

1. AGP |

А) Багатофункціональний контролер |

2. ISA |

В) Міст для з'єднання шини ISA та РСІ |

3. USB |

С) Контролер кеш-пам'яті |

4. PCI |

D) Локальна швидкісна шина вводу/виводу |

5. Host Bus |

Е) Набір мікросхем, встановлених на системній платі для забезпечення обміну даними між CPU та периферійними пристроями |

6. Bridge System I/O |

F) Стандартна шина вводу/виводу використовується для підключення повільних пристроїв (миші, клавіатури, модемів, старих звукових карт та ін.) |

7.Chipset |

Н) Локальна шина процесора |

8. І82380 |

І) Високошвидкісний графічний порт, призначений для ефективної реалізації ЗО-графіки |

9. І82385 |

J) Універсальний послідовний порт |

Завдання 2. Основні функції, що реалізує чипсет. (Вкажіть неправильні відповіді).

1. Обслуговування керуючих та конфігураційних сигналів процесора.

2. Підвищення навантажувальної властивості системної шини.

3. Мультиплексування адреси та формування керуючих сигналів динамічної пам'яті, зв'язок шини даних пам'яті з локальною шиною.

4. Формування керуючих сигналів вторинного кеша, порівняння його тегів поточною адресою звертання на локальній шині.

5. Діагностика помилок процесора.

6. Забезпечення когерентності (узгодженості) даних в обох рівнях кеш-пам'яті та основної пам'яті при звертанні як зі сторони процесора (процесорів), так і від контролерів шини РСІ.

7. Підвищення продуктивності системи при кешуванні пам'яті.

8. Зв'язок мультиплексованої шини адреси та даних шини РСІ з локальною шиною процесора та шиною динамічної пам'яті.

9. Формування керуючих сигналів шини РСІ, арбітраж контролерів шини.

10. Керування периферійними пристроями ПЕОМ.

Завдання 3. Правильно розставте типи чипсетів у колонках 2, 3, 4, 5 таблиці.

Підтримувані функції |

І430УХ |

І430НХ |

І430ТХ |

i430FX |

Два процесори |

- |

+ |

- |

- |

Тактова частота системної шини, МГц |

50-66 |

50-66 |

50-66 |

50-66 |

Кеш другого рівня: |

|

|

|

|

Максимальний розмір, Кбайт |

512 |

512 |

512 |

512 |

Розмір кешованої DRAM, |

|

|

|

|

Мбайт |

64 |

64/512 |

64 |

64 |

Тип кеш-пам'яті |

Async, |

Pipelined |

Async, |

Pipelined |

|

Sync, |

Burst |

Sync, |

Burst, |

|

Burst, |

|

Burst, |

|

|

Pipelined |

|

Pipelined |

|

|

Burst |

|

Burst |

|

Цикл читання кеш-пам'яті |

3-1-1-1 |

3-1-1-1 |

3-1-1-1 |

3-1-1-1 |

DRAM: |

|

|

|

|

Кількість ліній RAS |

4 |

8 |

4 |

6 |

Цикл читання на частоті |

|

|

|

|

66МГц |

|

|

|

|

FPM |

7-3-3-3 |

5-3-3-3 |

6-3-3-3 |

5-3-3-3 |

EDO |

7-2-2-2 |

5-2-2-2 |

6-2-2-2 |

5-2-2-2 |

BEDO |

- |

- |

- |

- |

SDRAM |

- |

- |

7-1-1-1 |

5-1-1- |

Максимальний об'єм, Мбайт |

128 |

512 |

128 |

1256 |

Контроль PARITY |

- |

+ |

- |

- |

Виявлення та виправлення |

|

|

|

|

помилок, ЕСС |

- |

+ |

- |

- |

Модулі пам'яті |

SIMM |

SIMM, |

SIMM, |

SIMM, |

|

|

DIMM |

DIMM |

DIMM |

Максимальна кількість |

|

|

|

|

SIMM/DIMM |

4 |

8/4 |

4/2 |

6/3 |

Підтримка АТА-33 |

- |

|

- |

+ |

Підтримка AGP |

- |

- |

- |

— |

Наявність контролера USB |

- |

+ |

+ |

+ |

Версія РСІ |

2.0 |

2.1 |

2.1 |

2.1 |

Підтримка Plug&Play |

+ |

+ |

+ |

+ |

ВІДПОВІДІ

Вправа 1. Закінчіть фразу

1 - С; 2 - К; 3 - А; 4 - Е; 5 -F; 10-G; 11 -В; 12 - H.

- D; 6 - І; 7 - J; 8 - L;

Вправа 2. Оберіть правильну відповідь

1) 1 -1; 2 - F; 3 - J; 4 - D; 5 - Н; 6 - В; 7 - Е; 8 - А; 9 - С.

2) 2; 5; 7.

3) 2 - i430FX; 3 - І430НХ; 4 - i430VX; 5 - І430ТХ.

Прикладні задачі

Початкові умови

Нехай у Вашому комп'ютері встановлена системна плата з процесором i80486DX4. На системній платі встановлено 16Мбайт оперативної пам'яті, організованої у вигляді двох SIMM-модулів.

Задача

Замінити системну плату з таким розрахунком, щоб до нової системної плати були підключені старі карти розширення та приводи зовнішніх пристроїв, а також був встановлений процесор типу Celeron та додатково 16 Мбайт пам'яті.

Ваше розв'язання

Цей список питань допоможе Вам виділити проблему та визначити шляхи її розв'язання.

1. Які типи чипсетів найбільш доцільні в архітектурі системної плати з процесором Celeron_________________?

2. Скільки та які слоти для модулів пам'яті повинні бути на новій платі___________________?

3. Скільки та які слоти розширення для зовнішніх пристроїв повинні бути на новій платі ____________?

4. Які характеристики має процесор, який Ви збираєтесь встановити на нову системну плату _________?

5. Чи повинна системна плата бути модернізованою в подальшому та в яких межах____________?

6. Які характеристики системної шини Вас задовольняють _________________________________?

Можливі розв'язки

У зв'язку з тим, що Ви вже маєте два SIMM-модулі пам'яті по 8 Мбайт та хочете збільшити її до 32 Мбайт, необхідна системна плата, на якій є як мінімум два слоти розширення для SIMM-модулів та два для DIMM-модулів. Але практика показує, що «змішування» SIMM- та DIMM-модулів не завжди коректне з точки зору надійності функціонування пам'яті. Можуть з'явитися проблеми, наприклад, при підвищенні температури в приміщенні. Таким чином, можливі два розв'язки:

спробувати знайти системну плату з чотирма слотами для SIMM-модулів (щоб встановити ще два SIMM-модулі по 8 Мбайт) та двома DIMM-модулями (для подальшої модернізації);

змінити Ваші 16 Мбайт у двох SIMM-модулях на один 16 Мбайтний DIMM-модуль (купивши додатково ще один 16 Мбайтний DIMM-модуль).

На системній платі повинні бути реалізовані засоби встановлення: напруга живлення процесора — 2,8 В; тактової частоти — 266 МГц та частоти системної шини 66 МГц, а також слот для встановлення процесора — Slot 1.

Слід пам'ятати, що спеціально для сім'ї Celeron корпорація Intel розробила чипсет типу І82440ЕХ.

Далі необхідно впевнитися в тому, що встановлена на системній платі BIOS підтримує процесор Celeron.

Та, нарешті, необхідно підібрати системну плату зважаючи на те, що на ній встановлено достатнью кількість рознімань розширення, необхідних для встановлення Ваших плат адаптерів зовнішніх пристроїв.

Ваш наступний крок

У першому розділі Ви вивчили архітектурні особливості побудови системних плат та призначення функціональних елементів «оточення» процесора. Слід зазначити, що з точки зору функціональності системні блоки практично не змінились та містять всі підсистеми: апаратних маскованих переривань, службу часу (RTS та таймер), прямого доступу до пам'яті, інтерфейси зовнішніх пристроїв (послідовний та паралельний), BIOS, контролер клавіатури та ін.

У перших 32-розрядних системах кожна підсистема була реалізована окремою мікросхемою або кількома ввімкненими каскадно. В сучасних системних платах функції вказаних підсистем виконуються засобами відповідних чипсетів. Але з метою програмної сумісності були збережені їх архітектурні особливості, принципи функціонування та призначення.

У наступних розділах навчального комплексу Ви приступите до вивчення архітектури, принципів функціонування та методів програмного задання режимів функціональних підсистем оточення процесора, цікавих з точки зору використання отриманих знань у прикладному та системному програмуванні. Нагадаємо, що фахівець вищої кваліфікації в галузі обчислювальних систем повинен досконало знати потенційні можливості наданих йому апаратних ресурсів та вміло використовувати свої знання та навички у практичній діяльності.

Оволодівайте «вищим пілотажем» керування апаратними ресурсами Вашого PC. Успіхів Вам та найкращих побажань.

Заняття І. Поняття про систему переривання ПЕОМ.

Заняття 2. Контролер переривання — апаратне забезпечення системи переривання ПЕОМ.

Заняття 3. Стани ПКП, керуючі слова ініціалізації та операційні слова робочих команд.

Заняття 4. Підготовка ПКП до роботи.

Заняття 5. Керування режимами роботи ПКП.

Заняття 6. Керування пріоритетами переривань.

Заняття 7. Принципи організації оброблювачів переривань.

Заняття 8. Приклади використання апаратних переривань.

Закріплення матеріалу.

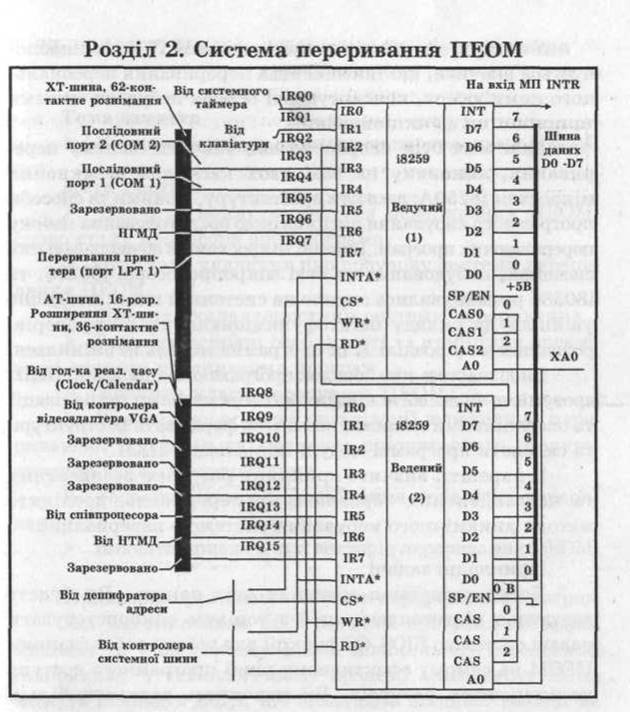

У розділі 2, «Система переривання ПЕОМ», пропонується вивчити, що таке система переривання персонального комп'ютера, концептуальні основи побудови системи та принципи функціонування.

Далі Вам буде запропоновано вивчити систему переривання, виконану на базі двох каскадно ввімкнених мікросхем І8259А; засвоїти архітектуру, режими та способи програмного керування дисципліною обслуговування потоку перериваючих програм. Вказані мікросхеми в обчислювальних системах, побудованих на базі мікропроцесорів i80286, та i80386 розміщувались окремо на системній платі, а пізніше увійшли до складу багатофункціональних контролерів, розглянених у розділі 1. їх програмна модель не змінилася.

Ви дізнаєтесь про порядок програмної ініціалізації ПКП, зрозумієте та засвоїте відмінності між словами ініціалізації та операційними словами, навчитесь формувати їх структури та складати програмні модулі ініціалізації ПКП.

І, нарешті, вивчите принципи розробки резидентних та нерезидентних оброблювачів переривань, дослідите методи динамічного керування системою переривання.

Прикладні задачі

Добре засвоївши матеріал усіх занять, Ви будете достатньо підготовлені, щоб з успіхом використовувати надані системою BIOS OS функції для роботи з обладнанням ПЕОМ на самому ефективному рівні програмного доступу до апаратних ресурсів. Ви навчитесь задавати більш ефективний для поточного додатку режим роботи системи переривання та розподіляти пріоритети обслуговування переривань обладнання з метою оптимізації часу реакції обчислювальної системи на запити.

Розв'яжіть проблему

У цій частиш перелічено проблеми, які можуть виникнути при неправильному розподіленні рівнів пріоритетів між пристроями ПЕОМ, при використанні різних способів завершення процедури обробки переривання, при використанні апаратних переривань для запуску користувальницьких програм і т. п. Ви повинні запропонувати свій варіант дій, для того щоб коректно розв'язати вказані проблеми.