- •Передмова

- •Intel 430lx

- •Intel 430nx

- •Intel 430fx

- •Intel 430hx

- •Intel 430vx

- •Intel 430tx

- •Intel 450gx/kx

- •Intel 440fx

- •Intel 440lx agPset

- •Intel 440ex

- •Intel 440bx agPset

- •Заняття 1. Поняття про систему переривання пеом

- •Принципи організації системи переривання програм

- •Слово стану процесора (програми)

- •Характеристики системи переривання

- •Організація переходу до перериваючої програми та пріоритетне обслуговування запитів переривання

- •Процедура переривання з опитуванням джерел (прапорців) переривання

- •Програмно-керований пріоритет перериваючих програм

- •Методи використання механізму переривань

- •Класи переривань пеом

- •Призначення контролера апаратних переривань пеом

- •Опис основних елементів і8259а

- •Стани програмованого контролера переривань

- •Заняття 5. Керування режимами роботи пкп

- •Void main (void){

- •Int mask;

- •Заняття 6. Керування пріоритетами переривань

- •Install proc near

- •Заняття 8. Особливості практичного використання апаратних та програмних переривань

- •Volatile long ticks;

- •Void main(void) {

- •Void _interrupt _far timer(void) {

- •Int8 proc near cli

- •Int09 proc near

- •Розділ 3. Підсистема таймера та годинника реального часу

- •Заняття 3. Системні засоби програмного доступу до ресурсів таймера

- •Void tm_delay(int ticks) {

- •Void main (void){

- •Void main(void){

- •Заняття 4. Приклади використання функціональних можливостей таймера в прикладних задачах

- •Void main(void){ int Frac; char k;

- •Void tm_sound(int freq, int time) {

- •Void tm_delay(int ticks) {

- •Void tm_sound(int freq, int time){

- •Void main(){

- •Void main() { int I,j; clrscr();

- •Заняття 5. Архітектура та принципи функціонування годинника реального часу

Заняття 5. Архітектура та принципи функціонування годинника реального часу

Тема заняття

Призначення, архітектура та принципи функціонування годинника реального часу.

Мета заняття

Зрозуміти та засвоїти функціональне призначення годинника реального часу в структурі ПЕОМ.

Вивчити архітектуру, характеристики та принципи функціонування компонентів МС 146818.

Ознайомитись із функціональним призначенням вхідних та вихідних сигналів МС 146818.

Отримати уявлення про можливості формування періодів переривання та вихідних частот генератора прямо кутних імпульсів.

Призначення годинника реального часу

Додаткові можливості з координації подій у часі в обчислювальних системах IBM PC AT реалізовані в годиннику реального часу. Його основна функція — відстежувати календарний (абсолютний, астрономічний) час.

У більшості систем, в якості годинника використовується ВІС RTC (Real-Time Clock) MC 146818 фірми Motorola. Можливості МС 146818 (особливо наявність 64-байтного вмонтованого ЗП) дозволяють годиннику виконувати, крім основної, й інші важливі для системи вцілому функції, як-от: збереження інформації про конфігурацію системи та формування запиту на переривання при відмові живлення. З метою попередження втрати інформації про астрономічний час та перекручування системної конфігурації годинник «живиться» від автономного акумулятора (6 В). Оскільки годинник реалізований по КМОП-технології, то акумулятора вистачає на 2-3 роки. Від нього живиться також власний тактовий 32 КГц генератор.

Архітектура годинника реального часу МС146818

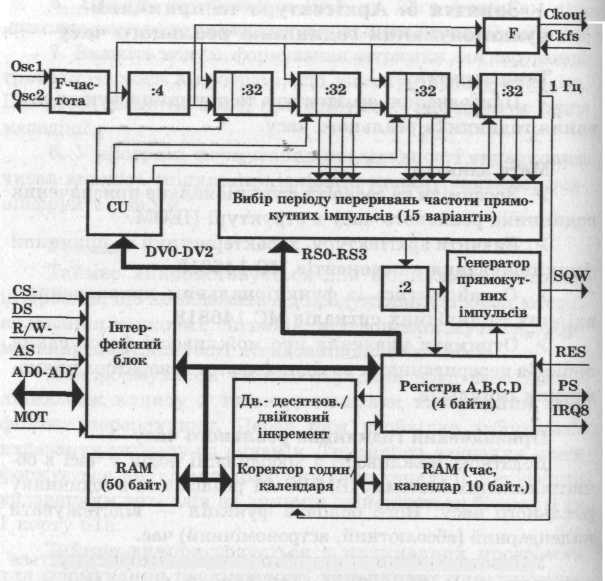

Блок-схема годинника реального часу МС146818 наведена на рис. 3.7.

Рис. 3.7. Блок-схема годинника реального часу

Формувач базової частоти у випадку підключення до нього виводів 0SC1 та 0SC2 кварцевого резонатора призначений для формування прямокутних імпульсів з частотою вхідного базового сигналу 0SC1. Вихід формувача подається на виходи п'яти послідовних каскадів дільника частоти та повторювача базової частоти. Вихідна частота першого каскаду дільника в 4 рази менша від його вхідної частоти; коефіцієнт ділення не залежить від вхідної базової частоти. Всі інші каскади мають максимально можливий коефіцієнт ділення — 32, що при максимальній вхідній базовій частоті 4.194304 МГц дозволяє отримати на виході останнього каскаду потрібну частоту 1 Гц. Якщо вхідна базова частота менша за максимальну (1.048576 МГц або 32.768 КГц), то в другому каскаді дільника треба зменшити коефіцієнт ділення так, щоб вихідна частота останнього каскаду залишилась незмінною (1 Гц).Керування коефіцієнтом ділення, скиданням та режимом роботи дільника виконує блок керування дільника згідно зі станом розрядів 4-6 регістра А (див. табл. 3.5 та рис. 3.7) — трьох розрядів шини даних дільника DV0-DV2 (Divider).

Мікросхема МС146818 забезпечує три незалежні джерела маскованих переривань роботи процесора, що програмуються: переривання за показниками RTC з частотою від 1 разу за секунду до 1 разу в день, періодичні переривання з частотою від 1 разу за 0.5 секунди до 1 разу за 30.5 мкс та переривання по завершенню циклу корекції (обновлення).

Базова опорна частота |

Стан розрядів регістра А |

Робочий режим |

Скидання дільника |

Обхід перших N розрядів дільника |

||

|

6 |

5 |

4 |

|

|

|

4.194304 мГц |

0 |

0 |

0 |

Так |

|

0 |

1.048576 мГц |

0 |

0 |

1 |

Так |

|

2 |

32.768 кГц |

0 |

1 |

0 |

Так |

|

7 |

Будь-яка |

1 |

1 |

0 |

Ні |

Так |

- |

Будь-яка |

1 |

1 |

1 |

Ні |

Так |

- |

Дозвіл переривань трьох видів здійснюється встановленням на 1 розрядів 4—6 регістра В; факт переривання фіксується в розрядах 4-6 регістра С (прапорець переривання). Частота періодичних переривань програмується встановленням розрядів 0-3 регістра А (див. табл. 3.6).

Програмувальний генератор прямокутних імпульсів призначений для зовнішнього використання, наприклад, для синтезу звуку або для програмного керування звуковим тоном. Частота сигналу на виході SQW програмується встановленням розрядів 0-3 регістра А і залежно від вхідної базової частоти може змінюватись у діапазоні від 2 Гц до 32 КГц. Формування сигналу SQW може бути заборонене або дозволене програмуванням стану розряду 3 регістра В.