- •Передмова

- •Intel 430lx

- •Intel 430nx

- •Intel 430fx

- •Intel 430hx

- •Intel 430vx

- •Intel 430tx

- •Intel 450gx/kx

- •Intel 440fx

- •Intel 440lx agPset

- •Intel 440ex

- •Intel 440bx agPset

- •Заняття 1. Поняття про систему переривання пеом

- •Принципи організації системи переривання програм

- •Слово стану процесора (програми)

- •Характеристики системи переривання

- •Організація переходу до перериваючої програми та пріоритетне обслуговування запитів переривання

- •Процедура переривання з опитуванням джерел (прапорців) переривання

- •Програмно-керований пріоритет перериваючих програм

- •Методи використання механізму переривань

- •Класи переривань пеом

- •Призначення контролера апаратних переривань пеом

- •Опис основних елементів і8259а

- •Стани програмованого контролера переривань

- •Заняття 5. Керування режимами роботи пкп

- •Void main (void){

- •Int mask;

- •Заняття 6. Керування пріоритетами переривань

- •Install proc near

- •Заняття 8. Особливості практичного використання апаратних та програмних переривань

- •Volatile long ticks;

- •Void main(void) {

- •Void _interrupt _far timer(void) {

- •Int8 proc near cli

- •Int09 proc near

- •Розділ 3. Підсистема таймера та годинника реального часу

- •Заняття 3. Системні засоби програмного доступу до ресурсів таймера

- •Void tm_delay(int ticks) {

- •Void main (void){

- •Void main(void){

- •Заняття 4. Приклади використання функціональних можливостей таймера в прикладних задачах

- •Void main(void){ int Frac; char k;

- •Void tm_sound(int freq, int time) {

- •Void tm_delay(int ticks) {

- •Void tm_sound(int freq, int time){

- •Void main(){

- •Void main() { int I,j; clrscr();

- •Заняття 5. Архітектура та принципи функціонування годинника реального часу

Гуржій А. М.

Коряк С. Ф.

Самсонов В. В.

Скляров О. Я.

АРХІТЕКТУРА,

ПРИНЦИПИ

ФУНКЦЮНУВАННЯ

ТА КЕРУВАННЯ

РЕСУРСАМИ

ІВМРС

Рекомендовано:

Міністерством

освіти і науки України

як навчальний посібник

Харків 2003

УДК 681.325.5-181.4 ББК 32.973.2 Г 95

Г95 Гуржій А. М., Коряк С. Ф., Самсонов В. В., Скляров О. Я.

Архітектура, принципи функціонування i керування ресурсами IBM PC: Навч. посібник. Харків: ТОВ «Компанія CMІT», 2003.-512 с.

Рецензенти:

Путятін В. П. — д.т.н., проф., зав. каф. Технічної кібернетики Харківського технічного університету сільського господарства;

Пушкар О. I. — д.е.н., проф., зав. каф. Обчислювальної техніки i програмування Харківського економічного університету;

Скобцов Ю. О. — д.т.н., проф., зав, каф. Автоматизовані системи управління Донецького національного технічного університету

Даний навчально-методичний комплекс (НМК) присвячений питаниям побудови, принципам функціонування i програмного керування апаратними ресурсами персонального комп'ютера. НМК містить повний обсяг інформації, необхідний для ycпішного засвоєння матеріалу в умовах дистанційного навчання (самостійного вивчення), об'еднує переваги практично вcix форм викладення матеріалу з метою вивчення: конспекту лекцій; методичних посібників до практичних занять, лабораторних po6iт i курсовому проектуванню; довідкової літератури.

НМК містить вичерпні відомості про архітектуру, режими i програмне керування функціональним обладнанням i підсистемами; практичні заняття i вправи з прикладами i розв'язаннями; лабораторний практикум з відлагодженими програмами, докладними коментарями операторів i функціональних модулів; приклади прикладних задач, методику їх розв'язання, програми; аналіз проблем, що виникають в обладнанні PC, технологію ix дослідження, поради фахівців; питания для самоконтролю ступеня засвоєння матеріалу, рекомендації з методики вивчення матеріалу.

Книга адресована вам, хто хоче отримати фундаментальні знания i набути практичні навички експлуатації персональних комп'ютерів.

Іл.: 85. Табл.: 35. Бібліогр.: 27 назв. ISBN 966-95983-3-8

© Гуржій А. М., Коряк С. Ф.,

Самсонов В. В., Скляров О. Я., 2003

Зміст

Передмова 14

Концепція навчального комплексу 16

Розділ 1. Типова базова архітектура системних

блоків ПЕОМ 19

Заняття 1. Архітектура 32-розрядно1 ПЕОМ 21

Базова структура 32-розрядної ПЕОМ на

прикладі Compaq Deskpro 21

Процесорна підсистема 22

Конвертер-узгоджувач шин 22 Основні технічні характеристики системної

плати 32-розрядно1 ПЕОМ 23

Питания для самоконтролю знань 25

Резюме 25

Заняття 2. Спеціалізовані багатофункціональні

HBIC для ПЕОМ-32 27

Архітектурні особливості контролера i82380 27

Функції та характеристика контролера ПДП 29

Програмований контролер переривань 30

Програмовані інтервальні таймери 31

Контролер регенерації динамічного ОЗП 31

Питания для самоконтролю знань 32

Резюме 32

Заняття 3. Апаратні засоби кешування

пам'яті 32-розрядних ПЕОМ 33

Переваги обчислювальних систем з

кеш-пам'яттю 33

Способи організації кеш-пам'яті 37

Цілісність даних в системах кеш-пам'яті 39

Високопродуктивний контролер

кеш-пам'яті i82385 40

Загальні характеристики 44

Деякі визначення та характеристики

контролера кеш-пам'яті 45

Робота контролера i82385 у складі системи 48

Інтерфейс контролера i82385 50

Докладніше про системний Інтерфейс 51

Встановлення даних для читання по лініях ВДО-ВД31 51

16-розрядний простір 52

Локальний інтерфейс 53

Питання для самоконтролю знань 54

Резюме 55

Заняття 4. Спеціалізовані багатофункціональні набори НВІС І82430 та І82440

Основні компоненти системної плати 58

Чипсет 61

Сhipset п'ятого покоління 65

Сhipset шостого покоління 70

Питання для самоконтролю знань 73

Резюме 74

Закріплення матеріалу 76

Основні положення 76

Перевірочна робота 81

Прикладні задачі 84

Розділ 2. Система переривання ПЕОМ 87

Заняття 1. Поняття про систему переривання ПЕОМ 89

Принципи організації системи переривання програм 89

Слово стану процесора (програми) 91

Характеристики системи переривання 92

Організація переходу до перериваючої програми та пріоритетне обслуговування запитів

переривання 94

Процедура переривання з опитуванням джерел (прапорців)

переривання 95

Програмно керований пріоритет перериваючих програм 95

Методи використання механізму переривань 97

Класи переривань ПЕОМ Таблиця векторів переривань ПЕОМ 97

Вправа 101

Практикум 101

Питання для самоконтролю знань 101

Резюме 102

Заняття 2. Контролер переривання — апаратне забезпечення системи переривання ПЕОМ 103

Призначення контролера апаратних переривань ПЕОМ 103

Основні функції, що реалізуються мікросхемою і8259А 105

Функціональні елементи мікросхеми і8259А 105 Короткий опис сигналів і8259А 105

Опис основних елементів і8259А 107

Режими обслуговування джерел переривань

Призначення та характеристики 110

Практикум 111

Питання для самоконтролю знань Резюме 112

Заняття 3. Стани ПКП, керуючі слова ініціалізації

та операційні слова робочих команд 115

Стани програмованого контролера переривань 115

Призначення та формати керуючих слів

ініціалізації ПКП 116

Призначення та формати операційних слів ПКП 118

Вправа 121

Питання для самоконтролю знань 121

Резюме 122

Заняття 4. Підготовка ПКП до роботи 123

Ініціалізація системи переривання ПЕОМ 123 Алгоритми ініціалізації системи переривання

ПЕОМ 123

Вправа 126

Питання для самоконтролю знань 126

Заняття 5. Керування режимами роботи 128

Керування режимами роботи 128

Режим повного вкладення (фіксованих

пріоритетів) 128

Способи завершення переривання (ЕОІ) 131

Звичайна команда ЕОІ 131

Спеціальна команда ЕОІ 132

Автоматичний режим ЕОІ (АЕОІ) 133

Маскування переривань 134

Спеціальний режим маскування (SMM) 134

Спеціальний режим повного вкладення (SFNM) 136

Режим розпізнавання запиту на переривання 137

Режим читання стану контролера і8259А 139

Режим опитування джерел переривань (POLL) 140

Вправи 141

Практикум 141

Лабораторна робота 1. Дослідження методів

програмного доступу до регістрів ПКП та

режиму маскування переривань 142

Питання для самоконтролю знань 144

Резюме 145

Заняття 6. Керування пріоритетами переривань 147

Керування пріоритетами переривань

Автоматична ротація, рівні пріоритети

Ротація в автоматичному режимі ЕОІ

Спеціальна ротація пріоритетів

Команда встановлення пріоритету

Ротація за спеціальною командою ЕОІ

Практикум 152

Лабораторна робота 2. Вивчення та

дослідження методів програмного задання

режимів роботи контролерів переривань 152

Вправи 153

Питання для самоконтролю знань 157

Резюме158 158

Заняття 7. Принципи організації оброблювачів переривань 159

Класифікація програм-оброблювачів переривання 159

Ініціалізація оброблювача переривання 160

Активізація обробки переривання 162

Фаза обробки переривання 163

Вихід із обробки переривання 164

Практикум 165

Лабораторна робота 3. Дослідження

методів розробки резидентних програм,

що перехоплюють апаратні переривання 165

Вправи 166

Питання для самоконтролю знань 173

Резюме 173

Заняття 8. Особливості практичного використання

апаратних та програмних переривань 175

Написання власного оброблювача переривання 175

Зміна таблиці векторів переривання 175

Особливості обробки апаратних переривань 180

Використання свопінгу в резидентних програмах 181

Практикум 186

Лабораторна робота 4. Дослідження методів розробки резидентних програм з фільтрацією оброблювачів апаратних перериван 186

Вправи 186

Питання для самоконтролю знань 187

Резюме 187

Закріплення матеріалу 189

Основні положення 189

Перевірочна робота 192

Прикладні задачі 198

Проблеми в системі переривання 204

Розв'яжіть проблему 204

Розділ 3. Підсистема таймера та годинника реального часу 209

Заняття 1. Архітектура та принципи функціонування таймера 209

Призначення таймера 209

Архітектура та принципи функціонування таймера 209

Вправа 213

Питання для самоконтролю знань 213

Резюме 214

Заняття 2. Методи програмного керування таймером 215

Програмування таймера

Вправа 223

Питання для самоконтролю знань 224

Резюме 224

Заняття 3. Системні засоби програмного доступу

до ресурсів таймера 226

Засоби BIOS для роботи з таймером 226

Засоби MS-DOS для роботи з таймером 229

Практикум 231

Лабораторна робота 1. Формування часових

інтервалів з використанням таймера 231

Вправи 231

Питання для самоконтролю знань 223

Резюме 234

Заняття 4. Приклади використання функціональних можливостей таймера в прикладних

задачах 235

Генерація звукових сигналів та відтворення

музики

Генерація випадкових чисел 235

Практикум 241

Лабораторна робота 2. Використання функціональних можливостей таймера для генерації звукових сигналів, відтворення музики та формування послідовності випадкових чисел 243 Вправи 244

Питання для самоконтролю знань 245

Резюме 246

Заняття 5. Архітектура та принципи функціо нування годинника реального часу 247

Призначення годинника реального часу 247

Архітектура годинника реального

часу МС146818 247

Функціональне призначення вхідних та

вихідних сигналів МС146818 252

Питання для самоконтролю знань 255

Резюме 255

Заняття 6. Застосування функціональних

можливостей годинника реального

часу в прикладних програмах 256

Призначення та формати регістрів КМОН-пам'яті 256

Засоби BIOS для роботи з годинником

реального часу 264

Практикум 265 Лабораторна робота 3. Вивчення та дослідження методів програмного керування

годинником реального часу 265

Вправи 266

Питання для самоконтролю знань 269

Резюме 270

Закріплення матеріалу 271

Основні положення 271

Перевірочна робота 273

Прикладні задачі 277

Проблеми в системі служби часу 278

Розв'яжіть проблему 279

Розділ 4. Підсистема прямого доступу до пам'яті 281

Заняття 1. Апаратне забезпечення прямого доступу до пам'яті ПЕОМ

Загальні відомості про систему прямого доступу до пам'яті

Прямий доступ до пам'яті в ПЕОМ

Архітектура контролера ПДП

Вхідні та вихідні сигнали контролера ПДП

та їх функціональне призначення 292

Питання для самоконтролю знань 295

Резюме 295

Заняття 2. Призначення та формати регістрів КПДП 297

Регістри контролера ПДП 297

Регістр станів (STAT) 297

Регістр команд (CR) 298

Регістр режиму (MOD) 299

Регістр маски (MASK) 299

Регістр запиту (REQ) 300

Регістр поточної адреси (CAR) 301

Регістр поточного лічильника слів (CCR) 301

Базові регістри адреси та лічильника

(BAR та CAR) 302

Часовий регістр (TR) 302

Канали системи ПДП ПЕОМ 304

Вправи 304

Питання для самоконтролю знань 305

Резюме 305

Заняття 3. Режими роботи та принципи

функціонування КПДП 307

Типи передач даних 307

Режими КПДП 308

Формати команд ПДП-контролера 309

Ініціалізація КПДП 313

Питання для самоконтролю знань 314

Резюме 314

Заняття 4. Програмне керування каналами КПДП 316

Приклад програмування підсистеми ПДП 316

Практикум 320

Лабораторна робота 1. Використання

функціональних можливостей КПДП для

організації передачі даних з сектора НГМД

у буферну область ОЗП та на екран дисплея 320

Питання для самоконтролю знань 321

Резюме 322

Закріплення матеріалу 323

Основні положення 323

Перевірочна робота 325

Прикладні задачі 327

Розділ 5. Послідовний та паралельний інтерфейси

вводу/виводу ПЕОМ 349

Заняття 1. Інтерфейси вводу/виводу зовнішніх

пристроїв ПЕОМ 351

Загальні відомості про системи вводу/виводу

та інтерфейс 351

Використання порту RS232C 354

Функціональне призначення сигналів

інтерфейса RS232C 356

Питання для самоконтролю знань 358

Резюме 359

Заняття 2. Принципи побудови універсального асинхронного приймача-передавача

(УАПП) 361

Функції апаратних засобів інтерфейса RS232C 361

Формати портів УАПП 363

Вправа 368

Практикум 369

Питання для самоконтролю знань 369

Резюме 370

Заняття 3. Програмування асинхронного адаптера 371

Ініціалізація УАПП 371

Підтримка асинхронного адаптера в BIOS 372

Підтримка асинхронного адаптера в MS-DOS 374

Програмування асинхронного адаптера 374

Підготовка інтерфейса RS232C до роботи 376 Організація зв'язку між комп'ютерами по

інтерфейсу RS232C 377

Практикум 379

Лабораторна робота 1. Дослідження

режимів послідовних інтерфейсів ПЕОМ

Питання для самоконтролю знань 386

Резюме 386

Заняття 4. Архітектура та програмування

паралельного порту 388

Призначення та характеристики інтерфеиса

Centronics 388

Опис портів інтерфейса Centronics 389

Засоби BIOS для роботи з принтером 398 Принципи функціонування паралельного

інтерфейса . 393

Вправа 397 Практикум 397 Лабораторна робота 2. Дослідження методів програмного керування виводом даних на прин тер з використанням паралельного інтерфеиса 398 Питання для самоконтролю знань 399 Резюме 399

Закріплення матеріалу 401

Основні положення 401

Перевірочна робота 412

Прикладні задачі 417 Проблеми, що виникають при практичному

використанні асинхронних адаптерів 421

Розв'яжіть проблему 423

Розділ 6. Клавіатура ПЕОМ 445

Заняття 1. Поняття про систему вводу даних

із клавіатури ПЕОМ 447

Принципи організації системи вводу даних

з клавіатури ПЕОМ 447

Буфер клавіатури 451

Клавіші 451

Функціонування клавіатури 451

Обмін даними на фізичному рівні 453

Режими роботи клавіатури 456

Практикум 457

Питання для самоконтролю знань

Резюме

Заняття 2. Контролер клавіатури — апаратне

забезпечення системи вводу даних ПЕОМ 460

Призначення контролера клавіатури ПЕОМ 460

Архітектура контролера клавіатури 460

Питання для самоконтролю знань 468

Резюме 468

Заняття 3. Програмна модель контролера клавіатури 470

Програмна модель мікро-ЕОМ І8042 470

Вправа 476

Питання для самоконтролю знань 476

Резюме 477

Заняття 4. Методи програмного керування 478

клавіатурою

Обробка подій при керуванні клавіатурою 478

Програмне керування клавіатурою 479

Команди контролера клавіатури 481

Засоби BIOS та MS-DOS для роботи

з клавіатурою 485

Практикум 493

Лабораторна робота 1. Дослідження методів

програмного керування контролером клавіатури 493

Питання для самоконтролю знань 494

Резюме 494

Закріплення матеріалу 495

Основні положення

Перевірочна роботаПрикладні задачі

Список скорочень та умовних позначень

Література

Передмова

Запропонований Вашій увазі навчальний комплекс присвячений, можливо, найнадзвичайнішому з усіх пристроїв, які коли-небудь створювались людиною,— персональному комп'ютеру. Сьогодні можна сміливо стверджувати, що ні одна з областей діяльності людини не розвивалась і не розвивається так стрімко, як сфера комп'ютерних технологій. Темпи щорічних змін у цій сфері вражають уяву. Можна сказати, що в 1981 році поява першого IBM PC (Perconal Computer) здійснила справжню інформаційну революцію, яка розвивається все більшими і більшими темпами. Зміна поколінь процесорів і ПЕОМ досягла інтервалів часу 1—1,2 роки. До цих пір ні в одній з областей людської діяльності не було таких темпів.

Останнім часом з'явилася велика кількість книг з програмного забезпечення ПЕОМ, але власне обладнанню персонального комп'ютера приділяється, на наш погляд, недостатньо уваги. Незважаючи на широке поширення дружнього графічного інтерфейса додатків, вимоги до знань апаратної частини PC неухильно зростають. Грамотне написання власних ефективних програм мовами високого і низького рівнів інколи неможливе без знань архітектури та принципів роботи апаратних ресурсів PC. Сучасні апаратні і програмні засоби при їх встановленні практично завжди роблять запит на інформацію про такі системні ресурси, як номер каналу переривання, прямого доступу, адреса базового порту вводу/виводу та ін.

Впровадження PC практично в усі сфери людської діяльності призвело до необхідності поєднання комп'ютера з різними зовнішніми пристроями (радіоприймачем, телевізором, відеокамерою, пристроями зв'язку з обладнанням технологічних процесів і об'єктів та ін.), що неможливо без глибоких знань апаратної частини PC.

На сьогодні є небагаточисельна література, в якій предсталена інформація про архітектуру та принципи функціонування апаратних компонентів PC. Проте, всі, хто має справу з персональним комп'ютером — від початківців до фахівців, що займаються професійним складанням PC,— відчувають постійну потребу в систематизованій та узагальнюючій інформації, яка б дозволила максимальною мірою самостійно зрозуміти не тільки основні принципи побудови та функціонування комп'ютера, але й оволодіти «вищим пілотажем» у програмному керуванні його апаратними ресурсами та функціональними можливостями. Тільки усвідомивши це та добросовісно вивчивши даний навчальний комплекс, Ви зможете стати фахівцем високого класу, здібним створити ефективні та конкурентоспроможні програмні продукти.

Ми приклали всіх зусиль, щоб донести до тих, хто відважиться сісти за комп'ютер достовірну інформацію про «внутрішній світ» PC. Сподіваємось, що наш навчальний комплекс допоможе Вам швидше стати справжнім фахівцем у розглядуваних областях комп'ютерних знань.

Будемо вдячні всім, хто надішле конструктивні відгуки та зауваження, та спробуємо врахувати їх у наступних частинах навчального комплексу.

Успіхів Вам та найкращі побажання!

Автори

Концепція навчального комплексу

Перед Вами не звичайний підручник, а навчальний комплекс, в якому ми спробували об'єднати переваги практично всіх форм викладення матеріалу з метою навчання:

- підручника;

- навчального посібника для самостійного вивчення матеріалу;

- конспекту лекцій;

- методичних посібників до практичних занять, лабораторних робіт і курсового проектування;

- довідкової літератури.

Даний навчальний комплекс призначений, перш за все, для тих, хто хоче оволодіти основами побудови апаратних засобів ПЕОМ, зрозуміти принципи їх функціонування та навчитися методам програмного керування при розв'язанні різних прикладних задач.

Матеріали навчального комплексу будуть корисні і для фахівців, які прагнуть до поглибленого вивчення принципів роботи комп'ютерів у цілому та їх окремих компонентів.

Для успішного засвоєння матеріалу необхідно виконати декілька умов.

1. Мати достатньо сильне бажання, терпіння та прагнення стати професіоналом.

Володіти деяким досвідом роботи на персональному комп'ютері, знати основи побудови базової системи вводу/виводу (BIOS) та операціоної системи MS-DOS.

Мати початкове уявлення про мови програмування C++ та Assembler.

Особливість навчального комплексу полягає в тому, що матеріал викладений у простій і доступній формі; має чітку структуру та являє собою не зведення правил або строге керівництво, а є путівником по цікавому «внутрішньому світу» комп'ютера, що значно спрощує його засвоєння.

Структура навчального комплексу

Навчальний комплекс складається з шести розділів, кожний з яких об'єднує кілька занять. У першому занятті розглядаються концептуальні питання побудови функціонального пристрою або підсистеми, що вивчаються, наводяться основні визначення та поняття. В наступному занятті наводиться спільна структурна схема та засоби підключення до системного інтерфейса, а також пояснюється призначення сигналів зв'язку. Далі наводиться архітектура пристрою та призначення його функціональних елементів. Після цього вивчаються режими роботи та методи програмного керування засобами BIOS та MS-DOS; дається аналіз функціональної повноти цих засобів. У заключному занятті розглядаються прикладні задачі, що використовують функціональні можливості даної підсистеми.

Кожне заняття побудоване за визначеною схемою.

Тема заняття. Коротке формулювання тем, що розглядаються у даному занятті.

Мета заняття. Детальний перелік знань, умінь та навичок, які необхідно сформувати у даному занятті.

Вправи. З прикладами розв'язання. Допомагають закріпити пройдений матеріал та набути навичокрозв'язання прикладних задач.

Практикум. Дослідження пристрою, що вивчається, за допомогою діагностуючих програмних засобів. Лабораторні роботи по дослідженню і вдосконаленню програм керування режимами роботи; практичне використання функціональних можливостей апаратних засобів в прикладних задачах.

Питання для самоконтролю знань. Допомагають впевнитися в надійності засвоєння матеріалу.

Резюме. Огляд найважливіших положень, на які треба звернути особливу увагу.

7. Ваш наступний крок. Встановлює зв'язок між вивченим матеріалом і тим, що треба буде взнати і вивчити

У черговому занятті. Дається мотивація до подальшого навчання.

Кожний розділ закінчується заняттям «Закріпленню матеріалу», в якому підводяться підсумки, закріплюється пройдений матеріал. Це заняття складається з кількох частин.

Основні положення. Узагальнення найважливіших положень, що розглядаються в розділі.

Перевірочна робота. Вправи допоможуть визначити, який матеріал Вам необхідно повторити, перш ні» приступити до наступного розділу. В кінці частині наводяться відповіді.

Прикладні задачі. Розв'язання практичних задач Вони вимагають від Вас комплексних знань, отриманих при вивченні матеріалу всього розділу. В кінці частини дано можливі розв'язки професіоналів, які Ви порівняєте зі своїми розв'язками; навчитеся системному підходу і засвоїте технологію розв'язання практичних задач.

Проблеми в .... Методика аналізу та усунення проблем. Зміст цієї частини пов'язаний з темою конкретного розділу та проблемами, які можуть виникнути в процесі експлуатації пристрою чи підсистеми, що вивчаються; дано тестові приклади, які Ви можете розв'язати, тільки спираючись на пройдений матеріал. Пропонуються можливі розв'язки професіоналів, методика аналізу проблем і технологія отримання розв'язків.

Розділ 1. Типова

базова архітектура системних блоків

ПЕОМ

Заняття 1. Архітектура 32-розрядної ПЕОМ.

Заняття 2. Спеціалізовані багатофункціональні НВІС для ПЕОМ-32.

Заняття 3. Апаратні засоби кешування пам'яті 32-роз-рядних ПЕОМ.

Заняття 4. Спеціалізовані багатофункціональні набори НВІС І82430 та І82440.

Закріплення матеріалу

Запрошуємо Вас на наше перше заняття! В розділі 1, «Типова базова архітектура системних блоків ПЕОМ», описуються концептуальні основи побудови системних блоків ПЕОМ. Ви дізнаєтесь про те, як окремі функціональні пристрої об'єднуються в єдине ціле — системний блок і, власне, тільки після цього стають ядром Вашого PC. Ви побачите, що потрібно зробити для забезпечення підвищення швидкодії комп'ютера, які архітектурні розв'язки дозволяють зберегти спадкоємність у поколіннях ПЕОМ.

У цьому розділі розглядається приклад великої інтегральної мікросхеми І82380, яка містить у собі практично всі функціональні пристрої оточення процесора. Ви впевнитесь у тому, що з функціональної точки зору їх властивості зберігаються, і вони забезпечують працездатність програмного забезпечення, розробленого для обчислювальних систем більш ранніх модифікацій.

Далі

Ви приступите до вивчення призначення,

архітектури

та принципів функціонування надвеликих

інтегральних

мікросхем, що являються сполучною ланкою

між усіма

компонентами системної плати комп'ютера.

Ці мікросхеми

є повнофункціональними наборами

(Chipset),

що

розв'язують такі задачі:

Далі

Ви приступите до вивчення призначення,

архітектури

та принципів функціонування надвеликих

інтегральних

мікросхем, що являються сполучною ланкою

між усіма

компонентами системної плати комп'ютера.

Ці мікросхеми

є повнофункціональними наборами

(Chipset),

що

розв'язують такі задачі:

- обслуговування керуючих і конфігураційних сигналів процесора;

- мультиплексування адреси та формування керуючих сигналів динамічної пам'яті, зв'язок шини даних пам'яті з локальною шиною;

- формування керуючих сигналів вторинного кеша, порівняння його тегів поточною адресою звертання на локальній шині;

- забезпечення когерентності (злагодженості) даних в обох рівнях кеш-пам'яті та основної пам'яті при звертанні як зі сторони процесора (процесорів), так і від контролерів шини РСІ;

- зв'язок мультиплексованої шини адреси та даних шини РСІ з локальною шиною процесора та шиною динамічної пам'яті;

- формування керуючих сигналів шини РСІ, арбітраж контролерів шини.

Вдосконалення Chipset здійснювалося в міру вдосконалення процесорів, пам'яті та периферійних пристроїв. Тому Вам буде запропоновано для вивчення кілька поколінь Chipset з різними характеристиками та можливостями по застосуванню в системних блоках ПЕОМ

Заняття 1. Архітектура 32-розрядної ПЕОМ

Тема заняття

- Архітектура та призначення основних функціональних блоків 32-розрядної ПЕОМ.

Мета заняття

- Отримати уявлення про архітектурні особливості

32-розрядної ПЕОМ.

- Вивчити способи підключення функціональних блоків оточення процесора до системної шини.

Отримати уявлення про призначення конвертера узгоджувача шин, його функцій.

Вивчити призначення дешифратора системних адрес.

Зрозуміти і засвоїти призначення вхідних і вихідних сигналів зв'язку системних пристроїв ПЕОМ.

- Засвоїти призначення локальної шини ПЕОМ.

Базова структура 32-розрядної ПЕОМ на прикладі Compaq Deskpro

Незважаючи на різноманітність структур моделей ПЕОМ/386, архітектурно вони практично однакові: програмно сумісні, базуються на архітектурі процесора І386, використовують функціонально подібні ОС - MS DOS, мають у своєму складі практично однакові комплекти ВІС оточення: контролер переривання, контролер ПДП, таймер, задавальний генератор, паралельний і послідовний порти вводу/виводу і т. п. Специфіка визначається типами системних інтерфейсів, конкретними типами мікросхем оточення, типом оперативної пам'яті (швидкодія, способи кешування, об'єм), додатковою до базової периферією і т. п.

Розглянемо особливості структури ПЕОМ-32 на прикладі Compaq Deskpro 386/16. Головною особливістю структури є системна шина, що складається з двох сегментів — центрального та периферійного. Сегменти зв'язані через конвертер-узгоджувач шин (КУШ), що виконує функцію узгодження 8/16-розрядної шини периферійних пристроїв, що працюють на тактовій частоті 8 МГц, з 32-розрядною локальною шиною (ЛШ) ядра ЕОМ, що працює на частоті 16 МГц. КУШ є програмно «прозорим» пристроєм.

Системна

плата ПЕОМ Compaq

Deskpro-386/16

являє

собою

багатошарову друкарську плату з

внутрішніми шарами розводки живлення,

що призначається для встановлення

основних компонентів ПЕОМ.

Системна

плата ПЕОМ Compaq

Deskpro-386/16

являє

собою

багатошарову друкарську плату з

внутрішніми шарами розводки живлення,

що призначається для встановлення

основних компонентів ПЕОМ.

Процесорна підсистема

До

складу цієї підсистеми входять:

До

складу цієї підсистеми входять:

- центральний процесор;

- один із співпроцесорів (І287-4/8 або І387-16);

- допоміжні елементи оточення процесора.

МП І386 синхронізується одним синхросигналом, який виробляється генератором 32 МГц. У процесорі частота вхідного сигналу ділиться на 2.

Математичний співпроцесор призначений для виконання обчислення з числами у формі з плаваючою точкою. В архітектурі, що розглядається, можливе встановлення співпроцесора і287-4/8. Співпроцесор сприймається процесором як зовнішній пристрій, для якого він здійснює вибір команд та даних, а також розміщує результати обчислень в пам'яті. Взаємозв'язок зі співпроцесором забезпечується швидкодіючою 32-розрядною локальною шиною.

Конвертер-узгоджувач шин

До складу КУШ входять:

- конвертер шини даних;

- буферні підсилювачі та регістр адреси;

- блок керування локальною шиною, АТ-шиною та Х-шиною.

КУШ виконує узгодження алгоритмів роботи, частот та форматів даних 32-розрядної ЛШ (робоча частота 16 МГц), 8/16-розрядної АТ-шини (8 МГц) та її 8-розрядного відгалуження (Х-шини), до якого підключена системна периферія.

Функції КУШ:

- виявлення факту звертання до системної периферії та пристрою АТ-шини;

- синхронізація циклів ЛШ та АТ-шини, зокрема, — синхронізація обміну з пристроями, що працюють за принципом «запит-відповідь»;

- ініціювання послідовності циклів АТ-шини для обміну інформацією між 8- та 16-розрядними пристроями, підключеними до АТ-шини та 32-розрядної ЛШ;

- взаємна комутація байтових тактів АТ-шини та ЛШ, запам'ятовування байтів та (або) слів на час перетворення подвійного слова.

За допомогою блока керування КУШ здійснюється доступ мікропроцесора до системної периферії, яка містить елементи, що розширюють інтерфейсні можливості МП та ряд системних периферійних пристроїв, розташованих на системній платі, які входять до складу базової конфігурації:

контролер прямого доступу до пам'яті;

контролер переривань, що програмується;

контролер клавіатури;

контролер регенерації динамічної пам'яті;

таймери;

годинник реального часу (RTS);

системні порти вводу/виводу.

Вказані пристрої підключаються до буферизованого відгалуження АТ-шини (Х-шини). Селекція конкретного пристрою здійснюється дешифратором адреси системної периферії. Для адресації до пристрою вводу/виводу використовується 16 адресних ліній. Адреси пристроїв на системній платі від OOh до FFh, а на платах адаптерів від 100h до FFFh. Лінія адреси А31 містить ознаку адресації до портів вводу/виводу співпроцесора (адреси від 800000F8h до 800000FFh).

Основні технічні характеристики системної плати 32-розрядної ПЕОМ

Основна обчислювальна продуктивність ПЕОМ забезпечується базовим процесором І386 (32-розрядним, з робочою тактовою частотою 16 МГц) та співпроцесором і387. На системній платі є (рис. 1.1):

- розетка для підключення співпроцесора І287 (16-роз-рядний, тактова частота 4/8 МГц — настройка апаратна); - розетка для підключення співпроцесора І387 (32-роз-рядний, тактова частота 16 МГц).

Характеристики високошвидкісної локальної шини визначають час вибірки кодів з пам'яті та включають:

- тип протоколу — синхронний;

- робоча частота — 16 МГц;

- режим використання ЛШ процесором — монополь

ний;

- адресний простір оперативної пам'яті — 16 Мбайт (використовується 24-розрядна адресна шина);

- підтримує конвеєрний режим процесора та поза процесорне звертання зі сторони АТ-шини;

- забезпечує узгодження роботи модулів основно пам'яті різної швидкодії за рахунок введення допоміжних станів очікування мікропроцесора;

- забезпечує можливість підключення одного модулі пам'яті з розмірами АТ-адаптера.

Потужність, що споживається системною платою складає 10 Вт (+5В; 2 А). Для підвищення ступеня ремонтнопридатності та можливості модернізації найбільш відповідальні мікросхеми встановлюються в перехідні колодки. Обладнання СП забезпечує: 7 каналів ПДП; 1! каналів маскованих переривань; 3 канали таймера; годин ник реального часу з автономним джерелом живлення підключення IBM-сумісної клавіатури.

Питання для самоконтролю знань

1. Які фактори визначають архітектурну одноманітність ПЕОМ-32?

2. Які функціональні блоки входять до складу процесорної підсистеми?

3. Призначення математичного співпроцесора і

структурі ПЕОМ?

З якою метою в структурі ПЕОМ використовується конвертер-узгоджувач шин?

Перелічіть основні характеристики системної платі

ПЕОМ.

6. За структурною схемою визначте кількість каналії

ПДП, переривань, таймера.

Резюме

Незважаючи на різноманітність структур моделеі ПЕОМ/386, архітектурно вони практично однакові: програмні сумісні, базуються на архітектурі процесора і386, використовують функціонально подібні ОС — MS-DOS, мають у своєму складі практично однакові комплекти ВІС-оточення: контролер переривання, контролер ПДП, таймер, задавальний генератор, паралельний і послідовний порти вводу/виводу і т. п. Специфіка визначається типами системних інтерфейсів, конкретними типами мікросхем оточення, типом оперативної пам'яті (швидкодія, способи кешування, об'єм), периферією додатковою до базової і т. п.

Ознаки, за якими розрізняють ПЕОМ, побудовані на базі МП І386:

- тип виконання мікропроцесора: І386; i386(DX); i386(SX); i386(SL);

- частотний варіант процесора, що використовується: 16, 20, 25, ЗО, 33, 40 МГц;

- вид та частотний варіант системної шини: XT (4.77 МГц), AT (6, 8, 10, 12, 14 МГц), EISA (8, 25; 8, 33 МГц), МСА (10, 14.5 МГц);

- апаратна підтримка (оточення) МП: на основі дискретної логіки; на основі набору ВІС; спеціально розроблених комплектів ВІС для конкретних мікропроцесорів;

- різні варіанти кешових структур: використання кеш-контролера з дискретних елементів, на базі однокристальних кеш-контролерів, з використанням спеціального комплекту кеш-ВІС;

- різні варіанти портативних ПЕОМ-32 на базі спеціально розроблених комплектів ВІС з низьким енергоспоживанням.

Ваш наступний крок

Після вивчення архітектурних особливостей побудови ядра обчислювальної системи на базі інтегральних схем середнього ступеня інтеграції, Вам корисно буде вивчити принципи організації функціональних блоків оточення процесора в структурі чипів більшого ступеня інтеграції. Такі багатофункціональні чипи забезпечують значне підвищення швидкодії обчислювальної системи і зменшують складність та трудомісткість її виробництва. У наступному занятті Ви ознайомитесь з одним із численних типів таких мікросхем.

Заняття 2. Спеціалізовані багатофункціональні НВІС для ПЕОМ-32

Тема заняття

- Архітектура та призначення основних функіональних блоків багатофункціонального контролера і823

Мета заняття

- Отримати уявлення про архітектурні особливості багатофункціонального контролера І82380.

- Вивчити склад, способи підключення функіональних блоків контролера І82380.

- Отримати уявлення про характеристику функціональних вузлів контролера.

Архітектурні особливості контролера І82380

Продуктивність обчислювальної системи на ' високошвидкісних процесорів значною мірою залежить швидкісних характеристик оточення процесора. Підвищення продуктивності мікросхем оточення за рахунок підвищення тактової частоти обмежується значною тереторіальною розподільністю на системній платі. Значним кроком у розв'язанні цієї проблеми було розроблення багатофункціональних ВІС, на одному кристалі я: розміщують практично всі основні елементи оточення процесора. Такою мікросхемою є багатофункціональний контролер І82380. До складу цього пристрою входять

- восьмиканальний контролер ПДП;

- логічні схеми системного скидання;

- 20-ти рівневий програмований контролер переривання (функціональне розширення каскадно ввімкне І82С59А);

- чотириканальний 16-розрядний таймер;

- програмований генератор зі станом очікування

- контролер регенерації динамічного ОЗП;

- схеми арбітражу внутрішньої шини.

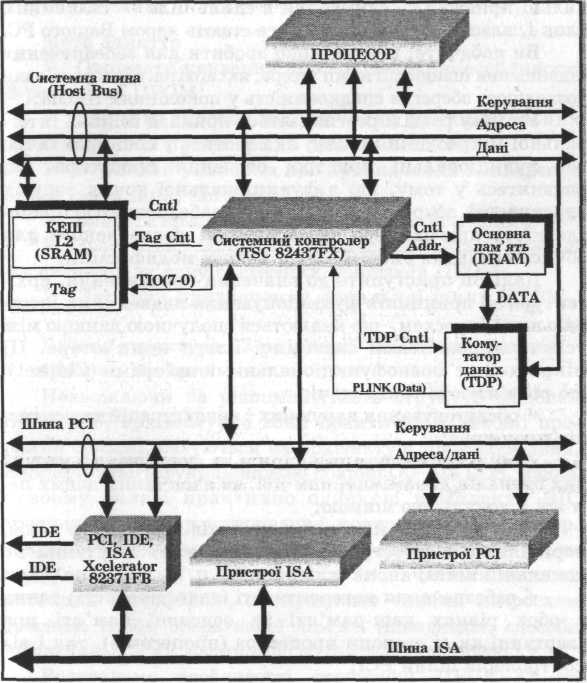

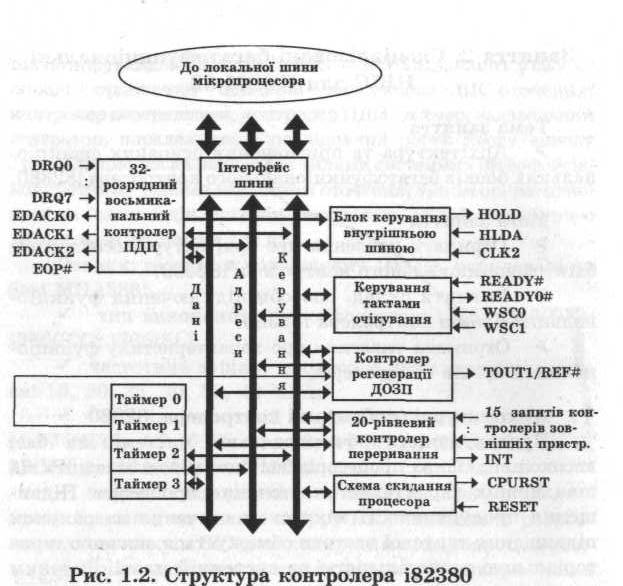

Структурна схема багатофункціонального контролера наведена на рис. 1.2.

Для забезпечення сумісності з існуючими програми продуктами в структурі контролера є побайтно доступні

регістри. Якщо внутрішнім логічним схемам необхідна деяка затримка, контролер автоматично вставить до циклу звертання до процесора необхідні такти очікування. У структурі контролера передбачені елементи, що забезпечують як програмне, так і апаратне скидання МП І386.

Контролер І82380 може працювати як у режимі ведучого пристрою, так і в підпорядкованому режимі. Оскільки після системного скидання контролер ПДП переходить у підпорядкований режим, то для системи він уявляється як пристрій вводу/виводу. У підпорядкованому режимі контролер відстежує стан мікропроцесора і відпрацьовує кожну команду у встановленому порядку. Виконуючи функцію керування ПДП І, контролер слідкує за станом потоку адрес для пристрою, до якого здійснюється звертання, та добавляє необхідне число тактів очікування до циклу звертання. При виконанні операцій передачі з ПДП контролер працює в привілейованому режимі як ведучий пристрій на шині.

Контролер І82380 підключається безпосередньо до локальної шини процесора І386, тому призначення йога керуючих сигналів таке саме, як у МП. Контролер відстежує поточний стан МП як за його сигналами стану, так і за сигналами на своїх виводах. Для організації внутрішньої синхронізації елементів І82380 та циклів МП частота вхідного сигналу CLK2 як і в процесора ділиться на два.

Контролер І82380 може керувати доступом до 8-розрядних периферійних пристроїв, що забезпечують сумісність з існуючими архітектурами систем та програмними продуктами. У підпорядкованому режимі І82380 контролює лінії стану та керування процесора, обробляючи логіку шини мікропроцесора та добавляючи необхідне числі тактів очікування.

У режимі ведучого робота контролера І82380 узгоджується з роботою процесора PC. Це значить, що для іншої частини системи та будь-якого підключеного периферійного пристрою механізм звертання залишається таким самим, як і в процесора.

Функції та характеристика контролера ПДП

За допомогою контролера ПДП можна адресувати повний простір, що покривається 32-розрядними фізнчними адресами, а також збільшувати та зменшувати адрес як операндів-джерел, так і операндів призначення. За допомогою внутрішнього допоміжного 32-розрядного регістр можна виконати складання та розбирання даних різної розрядності, а також організовувати обмін даними мі: пристроями, що мають різну ширину тракту даних. Пі час роботи контролера І82380 на частоті 20 МГц і при передачі даних однакової розрядності може бути досягнута швидкість обміну між пам'яттю та пристроями вводу/виводу 25.6 Мбайт/с.

У порядку обслуговування як програмних, так апаратних запитів ПДП контролер може підтримувати обмін даними таких типів:

- порт вводу/виводу — порт вводу/виводу;

- пам'ять — пам'ять;

- порт вводу/виводу — пам'ять;

- пам'ять — порт вводу/виводу.

Кожний

з восьми каналів контролера ПДП

функціонує

незалежно та може бути запрограмований

для роботи в будь-якому з допустимих

режимів. Для кожного каналу програміст

може вибирати дисципліну обслуговування

з циклічними

або фіксованими пріоритетами. Циклічний

пріоритет

передбачає розділення шини серед кількох

периферійних

пристроїв, тоді як дисципліна з фіксованими

пріоритетами

базується на визначених фіксованих

параметрах,

пов'язаних з апаратними та іншими

особливостями.

Кожний

з восьми каналів контролера ПДП

функціонує

незалежно та може бути запрограмований

для роботи в будь-якому з допустимих

режимів. Для кожного каналу програміст

може вибирати дисципліну обслуговування

з циклічними

або фіксованими пріоритетами. Циклічний

пріоритет

передбачає розділення шини серед кількох

периферійних

пристроїв, тоді як дисципліна з фіксованими

пріоритетами

базується на визначених фіксованих

параметрах,

пов'язаних з апаратними та іншими

особливостями.

Канали контролера розділені на дві групи по чотири канали. Канали від нульового до третього і від четвертого до сьомого працюють так, ніби два окремі контролери ввімкнені за каскадною схемою. Така організація роботи дозволяє одній групі присвоювати фіксовані пріоритети, а іншій — циклічні, причому в різних комбінаціях. За замовчанням канали контролера мають фіксовані пріоритети.

Програмований контролер переривань

Функціонально

контролер переривань у складі І82380

ідентичний

до своїх попередніх моделей І8259А та

І82С59А, за

винятком програмування векторів

переривань. У контролері І82380 об'єднані

ресурси трьох контролерів типу І82С59А.

Каскадуючи п'ятнадцать входів запитів

переривань

контролерів І82С59А, що є в розпорядженні

програміста,

можна організувати до 120 каналів запитів

зовнішніх переривань.

Функціонально

контролер переривань у складі І82380

ідентичний

до своїх попередніх моделей І8259А та

І82С59А, за

винятком програмування векторів

переривань. У контролері І82380 об'єднані

ресурси трьох контролерів типу І82С59А.

Каскадуючи п'ятнадцать входів запитів

переривань

контролерів І82С59А, що є в розпорядженні

програміста,

можна організувати до 120 каналів запитів

зовнішніх переривань.

У контролері переривань І82380 є більш широкі можливості з використання механізму векторів переривань, оскільки кожний вхід запиту може окремо програмуватися, це значить, що кожному запиту переривань може бути приписаний свій власний вектор переривання; крім того, системні програми за замовчанням можуть присвоїти контролеру переривань певний вектор. Цей вектор використовується в циклі підтвердження переривань, про які немає запиту, або переривань, викликаних помилковим запитом, з метою попередження системи про хибні переривання. За допомогою переривання система також інформується про те, що була здійснена спроба запрограмувати вектори контролера І82380 за методом контролера І82С59А.

Ця особливість гарантує сумісність існуючих програмних продуктів з програмним забезпеченням, написаним для І82380. До інших вдосконалень контролера переривань І82380 відноситься - можливість каскадного підключення зовнішніх контролерів переривань, а також те, що квітирування встановлення зв'язку між ведучим та веденим пристроями винесено зі спеціалізованих каскадних ліній на шину даних.

Програмовані інтервальні таймери

За принципом функціонування всі таймери ідентичні своєму попереднику І82С54. Кожний з чотирьох таймерів може працювати в одному з шести режимів. Процесор обчислювальної системи може встановлювати та зчитувати поточний вміст лічильників таймера в будь-який момент часу незалежно від режиму роботи. У зв'язку з тим, що нульовий канал таймера використовується контролером переривань, цей канал не має виходу з контролера І82380. Канал 1 таймера використовується для задання періоду регенерації динамічного ОЗП. Канали 2 та 3 використовуються для різних системних цілей конкретної ПЕОМ.

Контролер регенерації динамічного ОЗП

У складі контролера І82380 передбачено контролер регенерації динамічного ОЗП. Задатчиком циклу регенерації служить перший канал таймера. За сигналом запиту контролер регенерації виставляє запит доступу до системної шини за допомогою сигналу HOLD. Цей запит має вищий пріоритет, а отже, він може переривати будь-який активний процес, що відбувається з використанням контролера ПДП. Така організація роботи дозволяє контролеру ПДП передавати великі блоки даних, не впливаючи на функції з регенерації пам'яті. Це досягається тим, що контролер регенерації динамічного ОЗП не цілком захоплює керування шиною, а ніби «вклинюється» в цикли шини процесу ПДП.

Призначення та принципи функціонування інших блоків контролера І82380 зрозумілі з їх назви (див. рис. 1.2 та наступні розділи).

Питання для самоконтролю знань

Які функціональні елементи оточення процесора входять до складу контролера І82380?

В яких режимах може працювати контролер І82380?

Чому призначення керуючих сигналів контролера таке саме, як у мікропроцесора обчислювальної системи?

Назвіть функції та характеристики контролера ПДП у складі контролера І82380.

Назвіть функції та характеристики контролера переривань у складі контролера І82380.

Чим відрізняється таймер контролера І82380 від таймера І82С54?

Резюме

Для підвищення продуктивності обчислювальної системи на базі високошвидкісних процесорів у архітектурі ПЕОМ використовуються багатофункціональні ВІС, на одному кристалі яких розміщують практично всі основні елементи оточення процесора. Такою мікросхемою є багатофункціональний контролер І82380. У складі цього пристрою реалізовані:

- восьмиканальний контролер ПДП;

- логічні схеми системного скидання;

- 20-ти рівневий програмований контролер переривання (функціональне розширення каскадно ввімкнених І82С59А);

- чотириканальний 16-розрядний таймер;

- програмований генератор зі станом очікування;

- контролер регенерації динамічного ОЗП;

- схеми арбітражу внутрішньої шини.

Ваш наступний крок

Багатофункціональні

контролери виконують практично всі

основні системотвірні функції ядра

комп'ютера. Але в сучасних

системних блоках використовуються й

інші функціональні

пристрої, які дозволяють поліпшити

експлуатаційні

характеристики ПЕОМ. До таких пристроїв

відносяться

кеш-пам'ять та котролери кеш-пам'яті. В

наступному

занятті Вам пропонується ознайомитися

з цими пристроями,

їх призначенням, архітектурою та

принципами функціонування.

Багатофункціональні

контролери виконують практично всі

основні системотвірні функції ядра

комп'ютера. Але в сучасних

системних блоках використовуються й

інші функціональні

пристрої, які дозволяють поліпшити

експлуатаційні

характеристики ПЕОМ. До таких пристроїв

відносяться

кеш-пам'ять та котролери кеш-пам'яті. В

наступному

занятті Вам пропонується ознайомитися

з цими пристроями,

їх призначенням, архітектурою та

принципами функціонування.

Заняття 3. Апаратні засоби кешування пам'яті 32-розрядних ПЕОМ

Тема заняття

- Кешування оперативної пам'яті комп'ютера.

- Архітектура та принципи функціонування контро лера кеш-пам'яті.

Мета заняття

- Зрозуміти причини появи в складі процесорів та системних плат блоків статичних запам'ятовуючих пристроїв.

- Вивчити вірогідні характеристики кешів.

- Зрозуміти та засвоїти відмінності в організації методів запису та вибірки кодів з кеш-пам'яті.

- Навчитися оцінювати ефективність кешування залежно від розміру та способу організації кеш-пам'яті.

- Вивчити призначення, функції та характеристики контролера кеш-пам'яті І82385.

- Зрозуміти особливості інтерфейса зв'язку контролера з процесором.

- Вивчити методи відображення фізичного простору адрес комп'ютера на простір кеша.

- Засвоїти терміни, що відносяться до проблеми керування кешуванням пам'яті ПЕОМ.

- Вивчити всі аспекти роботи контролера кеш-пам'яті в складі обчислювальної системи на базі процесора i80386.

Переваги обчислювальних систем з кеш-пам'яттю

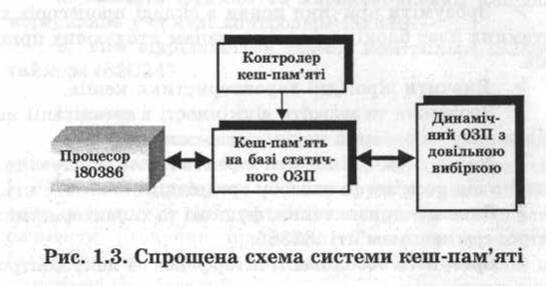

Системам кеш-пам'яті властиві переваги як статичних, так і динамічних запам'ятовуючих пристроїв. Однією з властивостей запам'ятовуючих пристроїв статичного типу є висока швидкодія, що дозволяє в повній мірі реалізувати швидкісні можливості системної шини, але вартість цих мікросхем достатньо висока. Схеми динамічної пам'яті дешевші, але менш швидкодіючі. І хоча час вибірки для запам'ятовуючих пристроїв динамічного типу досягає 50 -60 не, цього недостатньо, щоб перевершити статичні ОЗП. У системах кеш-пам'яті використовуються статичні запамятовуючі пристрої звичайно невеликого об'єму в якості пам'яті з безпосередньою вибіркою; основний об'єм пам'яті відводиться під динамічні ОЗП як вторинна пам'ять. Такий підхід дозволяє імітувати всю систему пам'яті як швидкодіючий запам'ятовуючий пристрій. У результаті отримуємо систему пам'яті, що характеризується швидкодією статичних ОЗП та вартістю ОЗП динамічного типу. На рис. 1.3 наведена спрощена схема системи кеш-пам'яті.

Кеш-блок побудований на основі статичних ОЗП, блок основної пам'яті містить динамічні запам'ятовуючі пристрої. Контролер кеш-пам'яті відстежує, який блок даних повинен спрямовуватися у кеш-блок, а який — в головну пам'ять.

Кеш-пам'ять може бути вмонтована всередину кристалу мікропроцесора або виконана у вигляді окремих вузлів мікропроцесорної системи.

Зовнішні кеші є автономними вузлами, які розташовують на системній платі комп'ютера. Робота системи кеш-пам'яті складніша від системи зі звичайною динамічною пам'яттю. Всі дані зберігаються в головній пам'яті, побудованій на основі динамічних ОЗП. Але найчастіше використовувані дані, крім того, запам'ятовуються в кеш-блоці, виконаному на базі статичних ОЗП. При звертанні мікропроцесора до пам'яті спочатку перевіряється наявність необхідних даних у кеш-блоці. Якщо в кеші інформація не знайдена, то відбувається звертання до головної пам'яті.

У залежності від організації роботи кеш-блока час доступу до пам'яті може бути істотно скорочений. Дисципліну роботи кеша можна вважати вірною, якщо в ньому містяться дані та коди команд, за якими безпосередньо звертається мікропроцесор. Очевидно, що чим більша ємність кеш-блока, тим вірогідніше, що в ньому будуть знаходитись необхідні дані. Виявлення шуканої інформації у кеші кваліфікується як вдале звертання до кеша. Коефіцієнт вдалих звертань залежить від розміру кеша, виконуваної програми, алгоритму керування кешем та дисципліни організації кеша. Якщо кеш-пам'ять вмонтована в кристал та має об'єм приблизно 256 Кбайт, то коефіцієнт вдалих звертань дорівнює 0,25. У сучасних обчислювальних системах, побудованих на базі 32-роз-рядних процесорів, робота кеш-пам'яті організована так, що коефіцієнт вдалих звертань досягає 0,95. По мірі збільшення коефіцієнта вдалих звертань підвищується ефективність системи та швидкість її роботи; за швидкодією системи кеш-пам'яті з високим коефіцієнтом вдалих звертань можуть наближатися до систем на базі статичних ОЗП. Звертання до пам'яті в комп'ютерних системах, як правило, виконується не випадковим чином. Тому в системах кеш-пам'яті робота базується за принципом передбачення з визначеною точністю наступної адреси звертання. Це зробити не так складно, оскільки програми найчастіше звертаються до послідовних чарунок пам'яті. Таким чином, за поточною адресою визначається можлива наступна адреса звертання до пам'яті. В основі описаного методу лежить поняття локальності програми.

Виходячи із властивості локальності програм, контролер кеш-пам'яті спроектований так, щоб була можливість вибирати з пам'яті блок даних (блочна вибірка) замість одиничних вибірок за вказаною адресою. Припустимо, що головна пам'ять розділена на блоки розміром від 2 до 16 байт. Тоді контролер кеш-пам'яті може виконати пересилання таких блоків з головної пам'яті в кеш та навпаки. Якщо шуканої інформації немає в кеші, то контролер кеш-пам'яті поновлює вміст кеша цілим блоком. Згідно з принципом локальності програми в наступному звертанні до пам'яті буде посилання на той самий блок, який на поточний момент знаходиться в кеші; все це призводить до збільшення коефіцієнта вдалих звертань до системи.

Розмір

блока є дуже важливим параметром. В

32-розрядних

системах контролер в якості блока

пересилає сукупність

даних розміром 2-4 слова. Навіть якщо

потрібно

знайти одне слово, то всерівно здійснюється

блочне пересилання.

Блоки, як правило, вирівнюються на межу

подвійного

слова, тому при блочному пересиланні

передаються

і деякі найближчі до необхідних даних

байти. У цілому

існує така залежність, згідно з якою,

чим більший розмір

блока, тим вищий коефіцієнт вдалих

звертань. Правда,

для більших блоків характерні деякі

недоліки. Наприклад,

чим більший розмір блока, тим менше

блоків розміщуються

в кеші. Зі зменшенням кількості блоків

росте ймовірність

появи операцій пересилання блоків з

головної пам'яті.

Крім того, збільшення розміру блока

призводить до

того, що відстань між кожним словом

блока та необхідним

словом у середньому стає більшою, що

послаблює умови

локальності програм. Нарешті, для

збільшення швидкості

блочних обмінів між головною пам'яттю

та кешем

бажано, щоб розрядність шини росла зі

збільшенням

розміру блока.

Розмір

блока є дуже важливим параметром. В

32-розрядних

системах контролер в якості блока

пересилає сукупність

даних розміром 2-4 слова. Навіть якщо

потрібно

знайти одне слово, то всерівно здійснюється

блочне пересилання.

Блоки, як правило, вирівнюються на межу

подвійного

слова, тому при блочному пересиланні

передаються

і деякі найближчі до необхідних даних

байти. У цілому

існує така залежність, згідно з якою,

чим більший розмір

блока, тим вищий коефіцієнт вдалих

звертань. Правда,

для більших блоків характерні деякі

недоліки. Наприклад,

чим більший розмір блока, тим менше

блоків розміщуються

в кеші. Зі зменшенням кількості блоків

росте ймовірність

появи операцій пересилання блоків з

головної пам'яті.

Крім того, збільшення розміру блока

призводить до

того, що відстань між кожним словом

блока та необхідним

словом у середньому стає більшою, що

послаблює умови

локальності програм. Нарешті, для

збільшення швидкості

блочних обмінів між головною пам'яттю

та кешем

бажано, щоб розрядність шини росла зі

збільшенням

розміру блока.

У сучасних комп'ютерах кеш звичайно будується за дворівневою схемою. Первинний кеш (LI Cache) вмонтований в усі процесори класу i486 та старші, він є і в деяких моделях І386. Об'єм його невеликий (8-32 Кбайт), тому для підвищення продуктивності часто використовується роздільне кешування команд та даних. Швидкодія внутрішніх кешів порівнюється зі швидкодією регістрів процесора. Вторинний кеш (L2 Cache), як правило, встановлюється на системній платі. Типовим для комп'ютерів на процесорах класу i486 вважається об'єм кеша 64-256 Кбайт, для Pentium — 256-512 Кбайт. У процесорах Pentium Pro синхронний L2 Cache розміщується в одному корпусі з процесором та працює на його внутрішній частоті. Найбільш суттєвою відмінністю організації роботи кеш-пам'яті є спосіб запису та вибірки кодів. У сучасних комп'ютерах найчастіше використовуються три способи організації кеш-пам'яті: асоціативний, з прямим відображенням та комбінований або багатоасоціативний.

Способи організації кеш-пам'яті

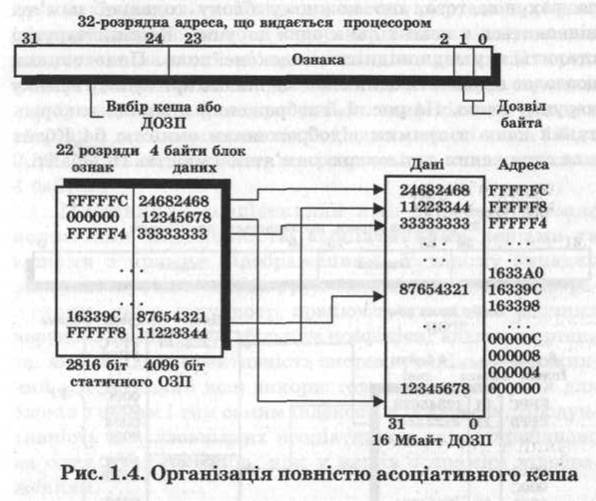

Для повністю асоціативного кеша (рис. 1.4) не існує взаємозв'язків між розбиттям пам'яті на блоки, їх розмірами та адресами.

На відміну від повністю асоціативного кеша в кеші з прямим відображенням порівняння адрес виконується один раз. Одноразове виконання порівняння адрес отримується за рахунок того, що кожному блоку головної пам'яті відводиться в кеші тільки одна чарунка. Кожній чарунці ставиться у відповідність індексне поле. Поле ознаки дозволяє відрізняти один блок від іншого при запису в деяку чарунку кеша. На рис. 1.5 зображений приклад використання кеша з прямим відображенням ємністю 64 Кбайт для спряження з головною пам'яттю ємністю 16 Мбайт.

Поле індексу кеша займає 16 розрядів. З них 14 розрядів використовуються для вибору одного з ібК-блоків кеша, а два розряди визначають один з чотирьох байтів блока. Поле ознаки, розмір якого дорівнює восьми розрядам, визначає один з 256 блоків, дані якого повинні бути поміщені у вибране місце кеша. Незважаючи на те, що кеші з прямим відображенням мають вже перелічені переваги в порівнянні з повністю асоціативними, вони все-таки мають недоліки. У випадку частих звертань до різних областей головної пам'яті контролер кеш-пам'яті повинен виконувати великий об'єм пересилання даних. У середньому продуктивність систем на базі кеша з прямим відображенням характеризується коефіцієнтом вдалих звертань, що змінюється від 0,41 для ємності кеша 1К до 0,89 для 128К за умови, що розрядність кеша дорівнює 4 байтам.

Цілісність даних у системах кеш-пам'яті

Припускається, що статичні ОЗП у системах кеш-пам'яті містять окремі копії інформації, що зберігається в запам'ятовуючих пристроях динамічного типу. У випадках, коли з'являються операції запису в кеш, дані в динамічних ОЗП не коригуються при зміні вмісту статичного ОЗП. Якщо не застосовувати спеціальних методів керування, то може порушитись цілісність даних, що зберігаються. Існують кілька способів оновлення інформації в головній пам'яті, які гарантують, що будь-яке звертання до даних скінчиться поверненням у головну пам'ять нового поточного значення даних. Один зі способів називається наскрізним записом. Згідно з цим способом копія даних записується як у кеш, так і головну пам'ять. Але даний спосіб знижує загальну ефективність системи внаслідок необхідності витрачати час на запис інформації в головну пам'ять.

Спосіб наскрізного запису може бути вдосконалений введенням використання операції запису з буферизацією. У цьому випадку мікропроцесор починає обробляти новий тактовий цикл раніше, ніж завершиться операція запису в головну пам'ять. Даний метод результативний, коли будь-який запит запису, за яким йде запит читання, закінчується вдалим звертанням до кеша, інакше мікропроцесор повинен деякий час чекати.

Можливо, кращим буде другий метод. Згідно з цим методом за допомогою одного з бітів у полі ознаки видно, що вміст блока був зміненим. Біт встановлюється, якщо у відповідний блок були записані нові дані. Таким чином, при звертанні за даними контролер кеш-пам'яті перевіряє біт ознаки. Якщо цей біт встановлений, то дані можуть бути переписані в головну пам'ять. Описаний метод, очевидно, забезпечує більшу швидкодію, ніж перший, оскільки кількість змінених блоків звичайно менша, ніж кількість операцій запису даних.

Високопродуктивний контролер кеш-пам'яті 82385

У даному занятті розглядається одна з популярних ВІС комплекту мікропроцесора i80386, використовуючи яку, можна проектувати високопродуктивні обчислювальні системи.

Продуктивність високошвидкісного мікропроцесора, такого, як i80386, обмежується швидкодією підсистеми пам'яті. Щоб не гальмувати роботу мікропроцесора, підсистема пам'яті повинна вчасно постачати йому коди команд та дані. При цьому в схемі підсистеми пам'яті повинен бути реалізований і компроміс між вимогами швидкодії пам'яті та вартості.

Мікропроцесор i80386 з високошвидкісною двотактною шиною в першому такті може виставити на шину адреси, а в наступному — видати або зчитати дані. Тому робота підсистеми пам'яті та мікропроцесора i80386 повинна бути погоджена за пропускною властивістю. При частоті 20 МГц тривалість тактового циклу дорівнює 50 не. Але, у випадку операцій з нульовим часом очікування час доступу до пам'яті повинен бути меншим 50 не. Подібні характеристики властиві статичним ОЗП, але їх застосування для побудови пам'яті великого об'єму звичайно виявляється надміру дорогим. Правильним у даній задачі є поєднання невеликої, але швидкодіючої статичної кеш-пам'яті та більш повільної динамічної головної пам'яті великої ємності.

Інтерфейс мікропроцесора i80386 з пам'яттю будується з використанням сигналу NA# наступної адреси для організації конвеєрного режиму видачі значень адрес. У конвеєрному режимі мікропроцесор видає наступну адресу перш, ніж завершиться поточний цикл звертань до пам'яті. Ця обставина дозволяє доповнити цикл звертання до головної пам'яті ще одним тактом, що робить можливим застосування схем динамічних ОЗП з часом вибірки 100 нс та менше. Продуктивність мікропроцесора i80386, що працює в конвеєрному режимі з нульовим часом очікування, складає 90 % продуктивності ідеальної системи, що працює без стану очікування. До циклу шини мікропроцесора i80386 можна ввести додаткові стани очікування, щоб забезпечити роботу з повільнодіючими модулями пам'яті, але це знизить пропускну властивість системи. Так, введення одного такту очікування до циклу шини, що не містить конвеєрної видачі адрес, призводить до 10 % -ого зниження продуктивності ідеальної системи пам'яті.

Як показує досвід, навіть застосування конвеєрного способу видачі адрес не дозволяє використовувати тільки динамічні ОЗП в системі пам'яті, що працює спільно з мікропроцесором i80386 на частоті 20 МГц, без введення до циклу шини, по крайній мірі, одного такту очікування. Таким чином, кращим розв'язанням задачі проектування системи пам'яті з пропускною властивістю, близькою до пропускної властивості системи з нульовим часом очікування, є система кеш-пам'яті. При проектуванні систем кеш-пам'яті необхідно враховувати такі показники, як вартість та пропускна властивість, дійсний об'єм апаратних витрат та збалансованість використання кеш-блока. У мультипроцесорних системах та системах з прямим доступом до пам'яті можливі ситуації, коли оновлення даних у головній пам'яті робить вміст кеша вже застарілим. Тому підсистема підтримки кеша повинна бути наділена властивістю контролювати роботу шини (за допомогою спостереження за шиною) з тим, щоб процесор міг вчасно поновлювати кеш після модифікації даних у пам'яті. Крім того, засоби програмної підтримки підсистеми кеша повинні зберігати прозорість основного програмного забезпечення, щоб гарантувалась його сумісність з існуючим програмним продуктом і не з'являлись перешкоди для можливих подальших удосконалень.

Питання взаємозв'язку розміру кеша, організації його обслуговування та продуктивності системи інтенсивно обговорюються спеціалістами. Але зрозуміло, що структура кеша цілком залежить від класу програм, які в основному будуть використовуватися системою, тому кеш слід настроювати за трасами адрес, що найчастіше використовуються прикладними програмами. Як правило, кеш більшого об'єму кращий за кеш меншого об'єму, оскільки дає кращий коефіцієнт вдалих звертань та продуктивність. Тема даного заняття пов'язана з високопродуктивним контролером кеш-пам'яті 82385, спеціально розробленим для функціонування в складі систем на базі мікропроцесора i80386 та ефективного керування кешем.

У попередньому занятті були розглянуті основи побудови систем кеш-пам'яті. Незалежно від типу кеша в системі повинен бути забезпечений швидкий доступ до часто використовуваних даних та кодів програм, як при роботі системи з швидкодіючим статичним ОЗП. Оскільки для ініціалізації контролера 82385 не вимагається спеціального програмного забезпечення, а сам контролер програмно невидимий, тобто прозорий, то він може бути з успіхом застосований в системах із вже існуючим програмним забезпеченням, а розробка нового програмного продукту не буде вимагати специфічних умов, пов'язаних з цим контролером. Пояснюється це тим, що контролер 82385 перехоплює звертання до пам'яті та обробляє їх безпосередньо сам без передачі запитів шині. В результаті знижується трафік шини та прискорюється доступ до пам'яті.

Як відмічалося раніше, продуктивність кеша можна характеризувати тим, як кеш обробляє звертання до пам'яті та як часто запитувані дані знаходяться в кеші (коефіцієнт вдалих звертань). Спеціалісти фірми Intel вважають, що в поняття доброї організації кеша повинні бути включені такі аспекти:

- відображення пам'яті на кеш;

- обробка ситуацій, коли дані відсутні в кеші;

- запис даних у пам'ять;

- когерентність кеша;

- не кешована пам'ять;

- вилучення непотрібної інформації із кеша;

- цілісність захисту програмного забезпечення;

- системний інтерфейс.

На коефіцієнт вдалих звертань впливають розмір кеша, розмір блоків, що передаються, ступінь локальності звертань до даних та кодів програм, рівні багатозадачності, переключень контексту, а також те, як компілятор формує об'єктні коди програм та дані. Тридцятидворозрядний контролер кеш-пам'яті 82385 розв'язує більшість із вказаних задач та забезпечує високу продуктивність систем обробки даних.

Контролер 82385 керує зовнішнім статичним ОЗП ємністю 32 Кбайт через відповідний каталог кеш-пам'яті. Контролер забезпечує прозорість на шині за допомогою спостереження за шиною, або «підслуховування» (snooping) шини. Спостереження за шиною реалізується контролером через інтерфейс, аналогічний інтерфейсу шини мікропроцесора i80386. Застосування контролера кеш-пам'яті 82385 дозволяє досягти максимуму пропускної властивості завдяки роботі з нульовими тактами очікування при всіх вдалих звертаннях до пам'яті по читанню. Нульові такти очікування можуть бути отримані також у випадку операцій запису в не кешовану пам'ять або в простір вводу/ виводу за умови, що попередні цикли запису завершились до цього часу.

Загальні характеристики

Завдяки своїй прозорості контролер кеш-пам'яті 82385 може бути включений до складу мікропроцесорних систем на базі i80386 для роботи в конвеєрному або не конвеєрному режимі та адресації простору пам'яті ємністю 4 Гбайти. Для тактової частоти 20 МГц цикл кеш-пам'яті дорівнює 35 не; ємність кеша складає 32 Кбайти; кеш служить для зберігання як кодів програм, так і даних. Прихованим чином контролер кеш-пам'яті заставляє мікропроцесор i80386 працювати в конвеєрному режимі щоразу, коли утворюється невдале звертання до кеша, або в не конвеєрному — при вдалому звертанні.

Контролер кеш-пам'яті може забезпечувати адресацією і не кешовану пам'ять. Ця додаткова властивість контролера дозволяє виконувати операції наскрізного вводу та виводу.

Поновлення головної пам'яті виконується на кожному циклі запису за допомогою методу відкладення наскрізного запису. При цьому продуктивність підвищується внаслідок видавання запитів на операції запису через деякий буфер, що дозволяє мікропроцесору продовжувати роботу з кешем, поки йде звертання до головної пам'яті.

Якщо контролер кеш-пам'яті перехопить операцію запису, яка буде видозмінювати вміст чарунки головної пам'яті, що має свою копію в кеші, то цю стару копію в кеші він оголосить не дійсною. Вміст оновленої чарунки пам'яті має бути перезавантажений в кеш, щоб вилучити з кеша застарілу інформацію. Кеш перезавантажується за допомогою свого каталогу, що містить перелік адрес головної пам'яті, які вказують на дані, що повинні бути скопійованими в кеш. Кожен запис в каталозі кеша відповідає одному блоку, який складається з восьми ліній. Кожна лінія складається з чотирьох байтів. Якщо при звертанні до кеша, в ньому не виявляється потрібної інформації, то кеш поновлюється за одним посиланням на головну пам'ять та в нього копіюється тільки одна нова лінія. В контролері 82385 передбачений режим самотес-тування, призначений для перевірки всіх чарунок каталогу кеша, а також опція видавання дампа пам'яті.

Контролер 82385 забезпечує властивість когерентності внаслідок відстеження роботи множинних пристроїв, що мають прямий доступ до пам'яті через системну шину. В системах з конфігурацією двопортової пам'яті, де механізм «підслуховування» не застосовується для виявлення змін вмісту головної пам'яті, контролер 82385 може виконувати опцію подавлення непотрібної інформації в кеші. Для виконання діагностичних функцій дана опція в контролері реалізована апаратно.

Деякі визначення та характеристики контролера кеш-пам'яті

Перш ніж описувати роботу контролера кеш-пам'яті та його компонентів, визначимо деякі терміни, специфічні для його архітектури.

Лінія. Поняття лінії відноситься до блока даних, що передаються між головною пам'яттю та кешем. Для контролера 82385 лінія складається з 32 розрядів. Вдале або невдале звертання до кеш-пам'яті фіксується в розряді достовірності лінії (Line Valid). Якщо розряд достовірності лінії встановлений на 1, то це значить, що лінія зазначена як присутня.

Блок. Каталог кеша містить посилання на блоки. Блок визначає фізичну адресу для восьми суміжних ліній або 32 байти.

Ознака. Поняття ознаки відноситься до інформації про адресу в каталозі кеша. Необхідність цього поняття зумовлене тим, що на один блок можуть відображатися багато адрес. За допомогою ознаки визначається точна адреса пам'яті, з якою на поточний момент пов'язаний деякий блок.

Вдале звертання. Вдале звертання до кеша з'являється тоді, коли значення ознаки окремого блока співпадає зі старшою частиною адреси на шині, а обидва розряди достовірності, ознака та лінії, встановлені на 1.

Вхід. Поняття входу характеризує ступінь зв'язності кеша. Кожний вхід зв'язується з деякою ознакою, розрядом достовірності ознаки та розрядами достовірності ліній. Для випадку множинних входів виконується операція множинних одночасних порівнянь адреси на шині та полів ознак, що дозволяє визначити, чи знаходяться дані в кеші. Контролер 82385 може бути настроєний на конфігурацію двовходового множинного асоціативного кеша (BANK А) або одновходового кеша з прямим відображенням (BANK В).

Множина. Множина являє собою групу блоків, що складаються з одного адресного блока на кожному вході. У випадку двовходового множинного асоціативного кеша всі блоки деякої множини вибираються одночасно, якщо частина адреси, що прийшла з шини, кодується в адресі цієї множини. Контролер 82385 підтримує 512 множин (кожній множині відповідають 2 блоки) для даної конфігурації та 1024 множини (кожна множина складається з 1 блока) для конфігурації одновходового кеша з прямим відображенням.

Конфігурації кеш-пам'яті. Кеш-пам'ять ємністю 32 Кбайти може бути розділена або на 8К подвійних слів для організації з прямим відображенням, або на два банки по 4К подвійних слів для конфігурації двовходового множинного асоціативного кеша.

Оновлення кеш-пам'яті. Контролер 82385 оновлює кеш-пам'ять з двовходовою множинною асоціативною конфігурацією за допомогою так званого LRU-алгоритму (least recently used), згідно з яким переписуються дані блока з найбільш давнім використанням у межах адресної множини. В конфігурації одновходового кеша з прямим відображенням проблем вибору не існує.

Каталог кеш-пам'яті. Контролер 82385 підтримує роботу двовходового множинного асоціативного кеша та одновходового кеша з прямим відображенням, причому каталог кешів в обох випадках однаковий. Як відмічалося раніше, якщо контролер 82385 настроєний на двовходову множинну асоціативну конфігурацію, то каталог кеш-пам'яті містить 512 множин на кожному вході (вхід 0 для банку А та вхід 1 для банку В).

Каталог кеш-пам'яті поновлюється за недостачею ознаки або лінії. Недостача ознаки виникає, якщо ознака не пройшла порівняння, або розряд достовірності ознаки скинутий. Недостача лінії виникає, якщо ознака пройшла порівняння, розряд достовірності ознаки дорівнює 1, а розряд достовірності лінії дорівнює 0.

Операції читання та запису в кеш-пам'ять

Контролер кеш-пам'яті керує трьома типами доступу за допомогою прозорого інтерфейса з системою на базі мікропроцесора i80386 та локальною шиною. Запити на виконання операцій читання та запису можуть виникати для випадків кешованої та не кешованої пам'яті, а також зі сторони локальної шини. Крім того, контролер 82385 підслуховує системну шину з метою виявлення будь-яких циклів запису в головну пам'ять.

Доступ до локальної шини. Контролер 82385 не реагує на декодовані ним запити доступу до локальної шини. Звертання до локальної шини не змінюють вмісту кеш-пам'яті та не направляються до системної шини.

Доступ до системної шини з не кешованою пам'яттю. Якщо контролер 82385 виявляє звертання до не кешованої пам'яті з операціями читання або запису, то він передає запит цього звертання до системної шини. Операція читання із не кешованої пам'яті виконується аналогічно випадку кешованої пам'яті, за винятком того, що не оновлюються кеш-пам'ять та її каталог. Аналогічно при керуванні зі сторони контролера 82385 операцією запису в не кешовану пам'ять (тобто також не оновлюються кеш-пам'ять та її каталог).

Доступ до системної шини для читання кешованої пам'яті. Контролер 82385 повинен отримати доступ до системної шини для обробки операції читання із кешованої пам'яті. Контролер кеш-пам'яті може бути запрограмований як на режим ведучого пристрою, так і на підпорядкований режим. У першому випадку контролер 82385 чекає, коли поточний ведучий пристрій звільнить шину, і далі починає виконання дій на системній шині. У підпорядкованому режимі контролер 82385 видає запит на захоплення системної шини і тільки після задоволення запиту починає виконувати шинний цикл.

Звертання до кеш-пам'яті за читанням, що виникає в результаті вдалого звертання, активізує відповідний модуль статичної пам'яті кеша, що видає дані на шину даних. Якщо каталог кеш-пам'яті настроєний на двовходову множинну асоціативну конфігурацію, то контролер 82385 за допомогою прапорця LRU визначає, що вибрано — вхід 0 (банк А) або вхід 1 (банк В).

Звертання до кеш-пам'яті за читанням у випадку відсутності необхідних даних примушують її контролер передати відповідний запит на системну шину для читання даних із головної пам'яті. При цьому контролер 82385 переводить мікропроцесор i80386 в конвеєрний режим, так що зовні в циклі перегляду кеша факт відсутності даних буде прихованим. Контролер 82385 керує всіма лініями розділення байтів на системній шині, сигналами керування та адресними лініями. Він перемикає приймач -передавач даних, підключений до системної шини, на приймання даних та готує кеш до операції запису. Якщо каталог кеш-пам'яті настроєний на двовходову множинну асоціативну конфігурацію, то за допомогою LRU-алгоритму контролер 82385 вибирає один з входів для виконання операції запису даних.

Доступ до системної шини для запису в кешовану пам'ять. У контролері 82385 реалізована схема відкладеного наскрізного запису, що дозволяє гарантувати, щоб всі операції запису мікропроцесора i80386 викликали оновлення головної пам'яті. Будь-яке звертання до кеш-пам'яті за записами заставить контролер 82385 оновити вміст самої кеш-пам'яті та її каталогу. Для запису адрес та даних використовуються асинхронно керовані буфери, що дозволяє локальній шині працювати без зупинок. У ті періоди часу, коли системна шина керується зі сторони контролера 82385, будь-які запити на доступ до системної шини від мікропроцесора i80386 переводяться в очікування.

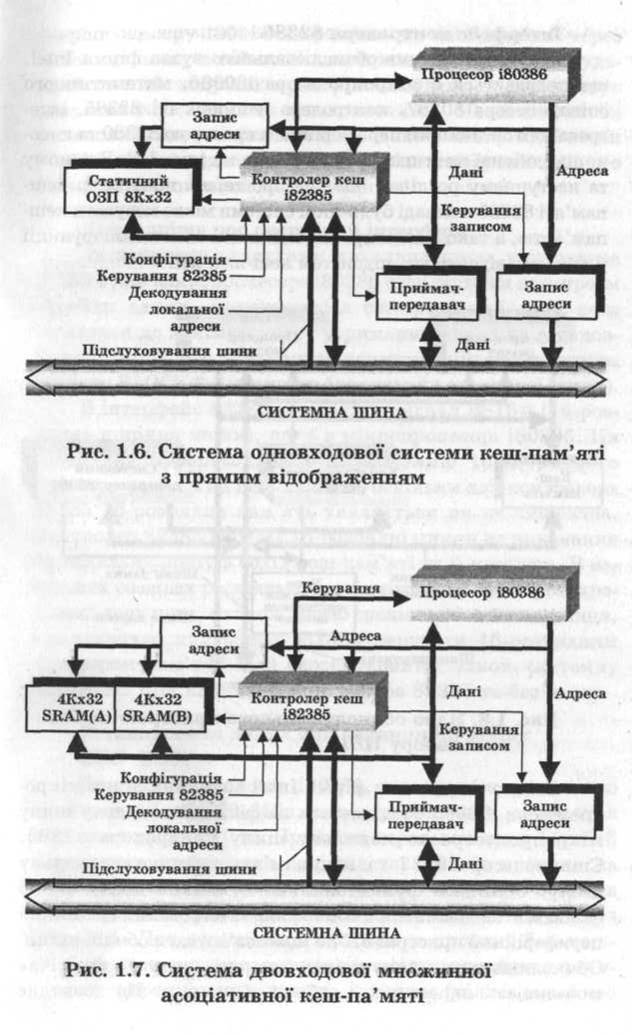

Робота контролера 82385 у складі системи

На рис. 1.6 та 1.7 наведені структурні схеми, в яких контролер 82385 керує роботою систем кеш-пам'яті відповідно одновходової з прямим відображенням та двовходової множинної асоціативної.

Слід відмітити, що способи адресації на базі моделі двовходового множинного асоціативного кеша дозволяють містити в пам'яті адреси та блоки даних.

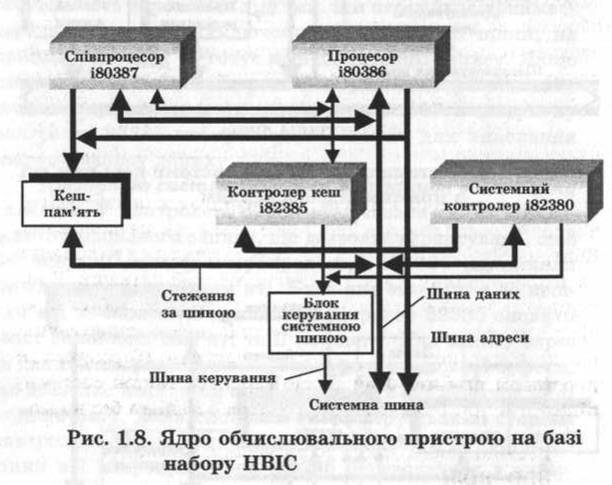

Інтерфейс контролера 82385

Структурна схема обчислювального вузла фірми Intel, що складається з мікропроцесора i80386, математичного співпроцесора 80387, контролера кеш-пам'яті 82385, інтегрованого системного периферійного пристрою 82380 та висо-кошвидкісної кеш-пам'яті, наведена на рис. 1.8. В даному та наступному розділах йдеться про те, як контролер кеш-пам'яті 82385 в складі будь-якої системи може керувати кеш-пам'яттю, а також виконувати визначені самостійні функції у випадку відсутності підсистем кеш-пам'яті.

Згідно з проектом фірми Intel локальна шина мікропроцесора i80386 розділяється на фізичну локальну шину мікропроцесора та локальну шину контролера 82385. Співпроцесор 80387 та кеш-пам'ять займають локальну шину. Оскільки функціонально локальна шина 82385 еквівалентна локальній шині i80386, інтегрований системний периферійний пристрій 82380 може зв'язувати обидві шини. Обчислювальну потужність даного вузла визначає можливість паралельної роботи обох шин. Це дозволяє мікропроцесору i80386 звертатися до кеш-пам'яті через локальну шину в той час, коли пристрій 82380 (або будь-який інший ведучий пристрій на шині) відпрацьовує керування системними компонентами. Незважаючи на функціональну еквівалентність даних шин, між ними існують деякі відмінності в способах синхронізації, що повинно враховуватись при розробці

Докладніше про системний інтерфейс

За деякими винятками локальна шина контролера 82385 є для мікропроцесора i80386 стандартним пристроєм обробки даних. Відмінності в синхронізації двох шин зводяться до мінімуму часу утримання даних та встановлення готовності, а також максимуму дійсної затримки сигналу BLOCK* (індикатор блокування системної шини).