Лабораторная работа # 12 (4 часа) исследование разных логических вентилей (cml gates)

1. Цель работы

Исследование характеристик и параметров логических элементов CML И-НЕ и ИЛИ-НЕ с помощью программного средства схемотехнического моделирования HSpice и оценка значений последних вычислительными способами.

2. Лабораторные задания

2.1. (NAND02 gate) схема и входные файлы логических элементов CML И-НЕ.

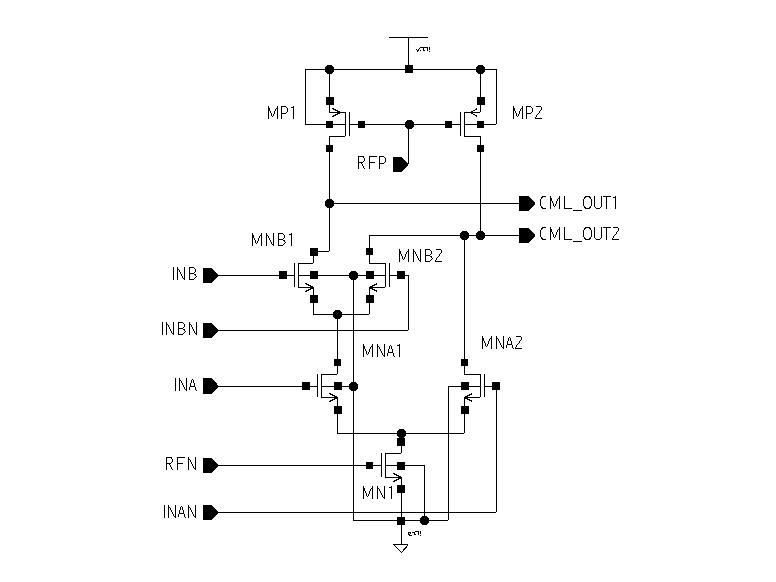

2.1.1. Составить схему логического элемента И-НЕ с тремя входами, используя данные из таблицы 2 в размерах, приведенных в таблице 1 (Рис.1):

|

|

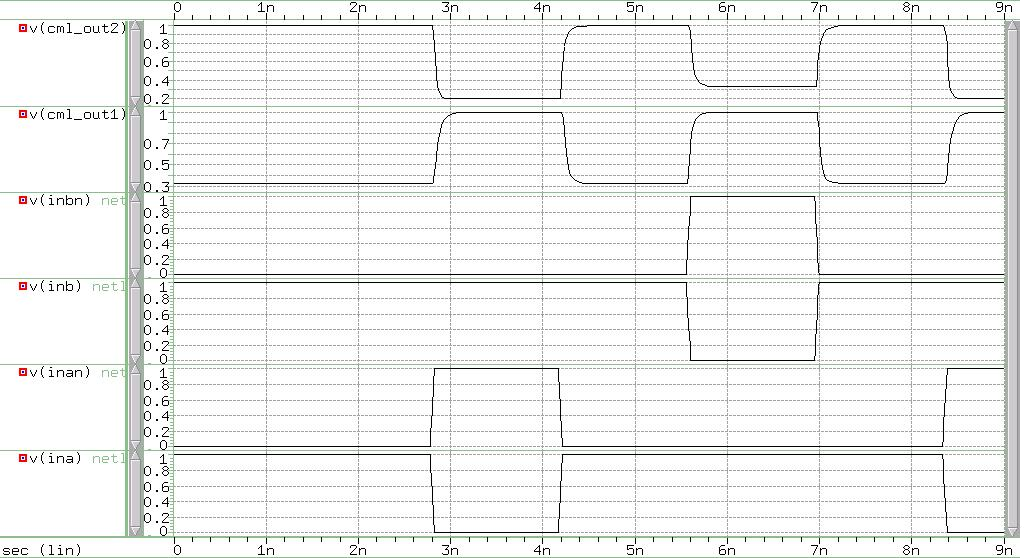

Рис. 7.1. Условный знак, электрическая схема и виды входного и выходного сигналов логического элемента

Таблица 7.1. Размеры транзисторов

-

Транзистор

W

L

мкм

мкм

MP1

5

0.40

MP2

5

0.40

MN1

5

0.38

MNA1

1.9

0.38

MNA2

1

0.38

MNB1

1.2

0.38

MNB2

1.2

0.38

2.1.2. Получить описание схемы (nand02_cml.netl файл) и расположить его по следующему адресу:

/student_lab/digital_ic/variant_val/...

2.1.3. Необходимые входные файлы для моделирования.

Для входных файлов принять:

Продолжительность входного фронта: 50 псек

Значение выходной емкостной нагрузки: Cload=5 фФ

2.1.3.1. Необходимый входной файл для логического элемента CML И-НЕ, используемый для измерения задержек и времени переключения при статическом режиме с применением программного средства схемотехнического моделирования HSpice, следующий:

*CML NAND02 Gate

*Propagation Delay, Transition Time

* HSPICE Netlist

.options POST=1 parhier=local

* Models section

* Include models

.include '/student_lab/digital_ic/all_models/model_val'

* Design variables section

* Define parameters

.param vdd = VDD_val

.param tr=TR_val

.param freq=FREQ_val

.param per=’1/freq’

.param tst=’0.5*per’

.temp Temp_val

* Structural netlist section

.include '/student_lab/digital_ic/variant_val/nand02_cml.netl'

vvss vss gnd dc=0

vvdd vdd gnd dc='vdd'

***Input Signals

va ina 0 pulse (vdd 0 'tst+1.0*per' tr tr '0.5*per-tr' '2.0*per')

va2 inan 0 pulse ( 0 vdd 'tst+1.0*per' tr tr '0.5*per-tr' '2.0*per')

vb inb 0 pulse (vdd 0 'tst+2.0*per' tr tr '0.5*per-tr' '2.0*per')

vb2 inbn 0 pulse ( 0 vdd 'tst+2.0*per' tr tr '0.5*per-tr' '2.0*per')

vrfp rfp 0 rfp

vrfn rfn 0 rfn

cloadcml_out1 cml_out1 0 LOAD_val

cloadcml_out2 cml_out2 0 LOAD_val

* Analysis section

* Transient Analyses

.tran ‘0.01*tr’ ‘5*per’

.probe v(*)

*Options

.option post probe

.option autostop

***Measures

***Propagation Delay

.meas tran tplh_ina_cml_out1 trig v(ina) val='0.5*vdd' fall=1 targ v(cml_out1) val='0.5*vdd' rise=1

.meas tran tphl_ina_cml_out1 trig v(ina) val='0.5*vdd' rise=1 targ v(cml_out1) val='0.5*vdd' fall=1

.meas tran tplh_inb_cml_out1 trig v(inb) val='0.5*vdd' fall=1 targ v(cml_out1) val='0.5*vdd' rise=2

.meas tran tphl_inb_cml_out1 trig v(inb) val='0.5*vdd' rise=1 targ v(cml_out1) val='0.5*vdd' fall=2

.meas tran tplh_ina_cml_out2 trig v(ina) val='0.5*vdd' rise=1 targ v(cml_out2) val='0.5*vdd' rise=1

.meas tran tphl_ina_cml_out2 trig v(ina) val='0.5*vdd' fall=1 targ v(cml_out2) val='0.5*vdd' fall=1

.meas tran tplh_inb_cml_out2 trig v(inb) val='0.5*vdd' rise=1 targ v(cml_out2) val='0.5*vdd' rise=2

.meas tran tphl_inb_cml_out2 trig v(inb) val='0.5*vdd' fall=1 targ v(cml_out2) val='0.5*vdd' fall=2

***Transition Time

.meas tran ttlh_ina_cml_out1 trig v(cml_out1) val='0.3*vdd' rise=1 targ v(cml_out1) val='0.7*vdd' rise=1

.meas tran tthl_ina_cml_out1 trig v(cml_out1) val='0.7*vdd' fall=1 targ v(cml_out1) val='0.3*vdd' fall=1

.meas tran ttlh_inb_cml_out1 trig v(cml_out1) val='0.3*vdd' rise=2 targ v(cml_out1) val='0.7*vdd' rise=2

.meas tran tthl_inb_cml_out1 trig v(cml_out1) val='0.7*vdd' fall=2 targ v(cml_out1) val='0.3*vdd' fall=2

.meas tran ttlh_ina_cml_out2 trig v(cml_out2) val='0.3*vdd' rise=1 targ v(cml_out2) val='0.7*vdd' rise=1

.meas tran tthl_ina_cml_out2 trig v(cml_out2) val='0.7*vdd' fall=1 targ v(cml_out2) val='0.3*vdd' fall=1

.meas tran ttlh_inb_cml_out2 trig v(cml_out2) val='0.3*vdd' rise=2 targ v(cml_out2) val='0.7*vdd' rise=2

.meas tran tthl_inb_cml_out2 trig v(cml_out2) val='0.7*vdd' fall=2 targ v(cml_out2) val='0.3*vdd' fall=2

.end

2.2. (CML MUX21) схема и входные файлы мультиплексора 2-1.

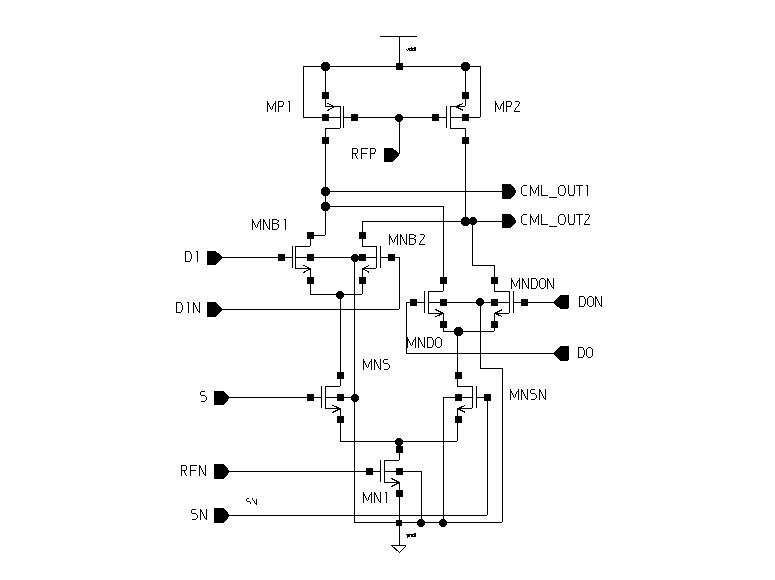

2.2.1. Составить схему CML мультиплексора 2-1 с тремя входами, используя данные из таблицы 3 в размерах, приведенных в таблице 2. (Рис.2):

|

|

Рис. 7.2. Условный знак, электрическая схема и виды входного и выходного сигналов CML мультиплексора 2-1

Таблица 7.2. Размеры транзисторов

-

Транзистор

W

L

мкм

мкм

MP1

5

0.40

MP2

5

0.40

MN1

5

0.38

MND0

1.5

0.38

MND0N

1.5

0.38

MND1

1.5

0.38

MND1N

1.5

0.38

MNS

2.0

0.38

MNSN

2.0

0.38

2.2.2. Получить описание схемы (nor02_cml.netl файл) и расположить его по следующему адресу:

/student_lab/digital_ic/variant_val/...