- •Часть I

- •Тема 1. Физические основы электроники 4

- •Тема 2. Источники вторичного электропитания 69

- •Тема 3. Усилители электрических сигналов 95

- •Тема 4. Импульсные и автогенерирующие устройства 137

- •Тема 5. Цифровая электроника и микропроцессорная техника 163

- •Тема 1. Физические основы электроники

- •1.1. Основные понятия электроники. Электропроводность полупроводников

- •1.2. Электрические переходы

- •1.3. Электронно-дырочный переход

- •1.4. Вольт-амперная характеристика электронно-дырочного перехода

- •1.5. Типы полупроводниковых диодов

- •1.6. Система обозначений полупроводниковых диодов

- •1.7. Транзисторы. Полевые и биполярные транзисторы

- •1.7.1. Устройство полевых транзисторов

- •1.7.2. Принцип действия полевого транзистора с управляющим p-n-переходом

- •1.7.3. Выходные статические характеристики полевого транзистора. Статические характеристики передачи полевого транзистора

- •1.7.4. Полевые транзисторы со встроенным каналом

- •1.7.5. Полевые транзисторы с индуцированным каналом

- •1.7.6. Малосигнальные параметры и система обозначений полевых транзисторов

- •1.7.7. Устройство и схемы включения биполярного транзистора

- •1.7.8. Режимы работы биполярного транзистора

- •1.7.9. Принцип работы биполярного транзистора в активном режиме

- •1.7.10. Параметры биполярного транзистора

- •Система z - параметров

- •Система y - параметров

- •Система h - параметров

- •1.7.11. Статические характеристики биполярных транзисторов

- •1.7.12. Система обозначения биполярных транзисторов

- •Тема 2. Источники вторичного электропитания

- •2.1. Принципы построения и классификация средств электропитания электронных устройств

- •2.2. Основные характеристики ивэп

- •2.3. Структурные схемы ивэп

- •2.4. Электрические фильтры

- •2.4.3. Полосовой lc-фильтр

- •2.4.4. Режекторный lc-фильтр

- •2.5. Выпрямители источников электропитания. Виды выпрямителей и их характеристики

- •2.5.1. Классификация выпрямителей

- •2.5.2. Однополупериодный выпрямитель

- •2.5.3. Двухполупериодный выпрямитель с нулевой точкой

- •2.5.4. Мостовая схема выпрямителя

- •2.5.5. Схема удвоения напряжения

- •2.5.6. Трехфазный выпрямитель

- •Тема 3. Усилители электрических сигналов

- •3.1. Основные понятия об усилителях и классификация усилителей

- •3.2.Основные характеристики и параметры усилителей

- •3.3. Характеристики и параметры усилителей, связанные с искажением сигналов в усилителе

- •3.4.Обратная связь в усилителях. Влияние ос на параметры усилителей

- •Влияние ос на параметры усилителей

- •3.5.Классы усиления транзисторных усилительных каскадов

- •3.6. Методы задания начального режима работы транзистора

- •3.7. Усилитель на биполярном транзисторе с общим эмиттером

- •3.8. Дифференциальный усилитель. Дрейф нуля в ду

- •3.8.1. Операционные усилители. Инвертирующие усилители. Неивертирующие усилители. Суммирующие и вычитающие усилители. Интеграторы

- •Инвертирующий усилитель

- •Неивертирующий усилитель

- •Суммирующий и вычитающий усилители

- •Интеграторы

- •3.9. Выходные усилители мощности

- •Тема 4. Импульсные и автогенерирующие устройства

- •4.1. Генерирующие и импульсные устройства. Передачи информации в импульсном режиме

- •4.2. Электронные ключи. Простейшие формирователи импульсных сигналов

- •4.2.1. Ключевой режим работы транзистора

- •Режим насыщения

- •4.2.2. Компараторы (схемы сравнения)

- •4.2.3. Триггер Шмитта

- •4.2.4. Мультивибраторы

- •4.2.5. Дифференцирующие rc цепи

- •4.2.6. Интегрирующие rc-цепи

- •4.2.7. Симметричный мультивибратор на оу

- •4.2.8. Одновибратор на оу

- •4.3. Генераторы линейно-изменяющегося напряжения (глин) на оу

- •4.3.1. Глин на оу с внешним запуском

- •4.3.2. Глин на оу в автогенераторном режиме.

- •4.4. Генераторы гармонических колебаний. Условия возникновения колебаний

- •4.4.1. Условия возникновения колебаний

- •4.4.2. Генераторы с rc-фазосдвигающими цепочками

- •4.4.3. Генераторы с мостом Вина

- •Тема 5. Цифровая электроника и микропроцессорная техника

- •5.1. Основные логические операции и их практическая реализация

- •5.1.1. Операция "не" (логическое отрицание или "инверсия")

- •5.1.2. Операция "или" (логическое сложение или дизъюнкция)

- •5.1.3. Операция "и" (логическое умножение или конъюнкция)

- •5.2. Типы логических микросхем

- •5.3. Элементы алгебры логики и синтеза комбинационных схем. Формы записи логических уравнений

- •5.3.1. Формы записи логических уравнений

- •5.3.2. Синтез комбинационных логических устройств

- •5.3.3. Реализация логических функций на элементах "и-не" и "или-не"

- •5.4. Интегральные комбинационные схемы

- •5.5. Логические устройства последовательного типа

- •5.5.1. Триггеры

- •5.5.2. Счётчики

- •5.5.3. Регистры

- •5.6. Цифровые запоминающие устройства

- •5.6.1. Структуры запоминающих устройств

- •5.7. Аналого-цифровые и цифро-аналоговые преобразователи

- •5.7.1. Аналого-цифровые преобразователи

5.6.1. Структуры запоминающих устройств

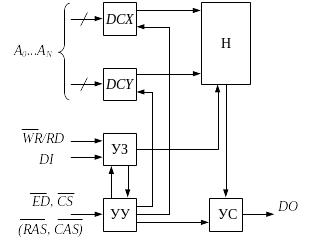

Обобщенная структура ЗУ представлена на рис. 5.6.1.

Рис. 5.6.1. Обобщенная структурная схема большой интегральной схемы ЗУ

В ее состав входят: дешифратор строк DCX и столбцов DCY, накопитель H, устройство записи УЗ и устройство управления. В зависимости от типа ЗУ те или иные узлы могут отсутствовать или меняться их схемотехника.

Основной составной частью ЗУ является матрица накопителя, которая представляет собой массив запоминающих элементов, объединенных в матрицу. ЗЭ может хранить один бит информации. ЗЭ могут быть объединены в ЗЯ, которая хранит слово, состоящее из 8, 16 бит. Для обращения к ЗЭ или ЗЯ необходимо выбрать ее с помощью кода адреса (каждая ячейка имеет свой уникальный адрес).

Статические ОЗУ и ПЗУ имеют аналогичные структуры, динамические ОЗУ имеют свои особенности структуры. Наиболее характерные структуры ЗУ подразделяют на структуры с одномерной (словарной) адресацией – 2D, 2DM и структуры с двумерной (матричной) адресацией – 3D.

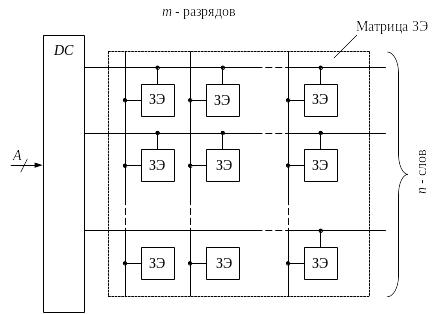

Структура 2D представляет собой матрицу размерностью M = m × n, где n – число хранимых слов, m – их разрядность (рис. 5.6.2.).

Рис. 5.6.2. Структура ЗУ типа 2D

Дешифратор DC служит для выбора заданного слова, разрешая доступ ко всем элементам выбранной строки, хранящей слово, адрес которого соответствует номеру строки. Выбор режима чтения или записи осуществляется воздействием сигнала чтение/запись.

ЗУ типа 2D применяется лишь для памяти малого объема, основным недостатком этой структуры является чрезмерное усложнение дешифратора при наращивании объема памяти. Число выводов дешифратора равно числу хранимых слов. Так, для ЗУ с организацией 256 × 4 необходим дешифратор с 256 выходами, что чрезмерно усложняет аппаратную реализации схемы.

Структура 3D применяется для упрощения дешифрации адреса с помощью двухкоординатной выборки ЗЭ. Структура ЗУ с двухкоординатной выборкой показана на рис. 5.6.3.

Код адреса разрядностью n делится на две половины (А n-1…Ak, Ak1…A0), одна служит для определения строки, вторая – для определения столбца. Таким образом, выбирается один бит нужного слова, который находится в ЗЭ на пересечении активных выходов обоих дешифраторов. Суммарное число необходимых дешифраторов гораздо меньше, чем в структуре 2D. Например, для структуры 2D при хранении 1К слов потребовался дешифратор с 1024 выходами, для структуры 3D нужны два дешифратора с 32 выходами у каждого.

При построении ЗУ для многоразрядных слов к дешифраторам строки и столбца могут подключаться параллельно несколько матриц, число которых равно разрядности хранимых слов. Каждая матрица выдает один бит адресованного слова. Недостатком структуры 3D является усложнение элементов памяти, имеющих двухкоординатную выборку. В связи с этим структуры 3D применяются редко.

Структура 2DM содержит дешифратор для выбора строки матрицы и мультиплексоры для выбора разрядов слова. Эта структура похожа на структуру 2D – активный выход дешифратора выбирает целую строку. Отличие в том, что длина строки не равна разрядности хранимых слов, гораздо длиннее ее. Вследствие этого уменьшается количество строк матрицы и, соответственно, уменьшается количество необходимых выходов дешифратора (рис. 5.6.4).

Рис.5.6.3. Структура ЗУ 3D

Для выбора строки используется только часть разрядов адресного кода А n-1…Ak. Остальные разряды адресного кода Ak-1…A0 используются для выборки необходимого слова из всего объема слов, содержащихся в строке. Для этого используются мультиплексоры, адресные входы которых соединены с шинами Ak-1…A0. На выходах мультиплексоров формируется выходное слово, каждый разряд которого выбирается из отрезка строки длиной m2k, где m – разрядность хранимых слов. На выходах m мультиплексоров формируется выходное слово, каждый разряд которого выбирается из отрезка строки длиной 2к.

Рис. 5.6.4. Структура типа 2DM

Для примера, в ЗУ типа 2DM 256 × 4 используется матрица 32 × 32, для обращения к каждому ЗЭ необходимо восьмиразрядное адресное слово. Пять разрядов этого слова поступают на дешифратор и выбирают одну из 32 строк матрицы ЗЭ. Три оставшихся разряда адресного слова поступают на адресные входы четырех мультиплексоров и выбирают из отрезков 23 = 8 разрядов один бит каждого слова.