- •Часть I

- •Тема 1. Физические основы электроники 4

- •Тема 2. Источники вторичного электропитания 69

- •Тема 3. Усилители электрических сигналов 95

- •Тема 4. Импульсные и автогенерирующие устройства 137

- •Тема 5. Цифровая электроника и микропроцессорная техника 163

- •Тема 1. Физические основы электроники

- •1.1. Основные понятия электроники. Электропроводность полупроводников

- •1.2. Электрические переходы

- •1.3. Электронно-дырочный переход

- •1.4. Вольт-амперная характеристика электронно-дырочного перехода

- •1.5. Типы полупроводниковых диодов

- •1.6. Система обозначений полупроводниковых диодов

- •1.7. Транзисторы. Полевые и биполярные транзисторы

- •1.7.1. Устройство полевых транзисторов

- •1.7.2. Принцип действия полевого транзистора с управляющим p-n-переходом

- •1.7.3. Выходные статические характеристики полевого транзистора. Статические характеристики передачи полевого транзистора

- •1.7.4. Полевые транзисторы со встроенным каналом

- •1.7.5. Полевые транзисторы с индуцированным каналом

- •1.7.6. Малосигнальные параметры и система обозначений полевых транзисторов

- •1.7.7. Устройство и схемы включения биполярного транзистора

- •1.7.8. Режимы работы биполярного транзистора

- •1.7.9. Принцип работы биполярного транзистора в активном режиме

- •1.7.10. Параметры биполярного транзистора

- •Система z - параметров

- •Система y - параметров

- •Система h - параметров

- •1.7.11. Статические характеристики биполярных транзисторов

- •1.7.12. Система обозначения биполярных транзисторов

- •Тема 2. Источники вторичного электропитания

- •2.1. Принципы построения и классификация средств электропитания электронных устройств

- •2.2. Основные характеристики ивэп

- •2.3. Структурные схемы ивэп

- •2.4. Электрические фильтры

- •2.4.3. Полосовой lc-фильтр

- •2.4.4. Режекторный lc-фильтр

- •2.5. Выпрямители источников электропитания. Виды выпрямителей и их характеристики

- •2.5.1. Классификация выпрямителей

- •2.5.2. Однополупериодный выпрямитель

- •2.5.3. Двухполупериодный выпрямитель с нулевой точкой

- •2.5.4. Мостовая схема выпрямителя

- •2.5.5. Схема удвоения напряжения

- •2.5.6. Трехфазный выпрямитель

- •Тема 3. Усилители электрических сигналов

- •3.1. Основные понятия об усилителях и классификация усилителей

- •3.2.Основные характеристики и параметры усилителей

- •3.3. Характеристики и параметры усилителей, связанные с искажением сигналов в усилителе

- •3.4.Обратная связь в усилителях. Влияние ос на параметры усилителей

- •Влияние ос на параметры усилителей

- •3.5.Классы усиления транзисторных усилительных каскадов

- •3.6. Методы задания начального режима работы транзистора

- •3.7. Усилитель на биполярном транзисторе с общим эмиттером

- •3.8. Дифференциальный усилитель. Дрейф нуля в ду

- •3.8.1. Операционные усилители. Инвертирующие усилители. Неивертирующие усилители. Суммирующие и вычитающие усилители. Интеграторы

- •Инвертирующий усилитель

- •Неивертирующий усилитель

- •Суммирующий и вычитающий усилители

- •Интеграторы

- •3.9. Выходные усилители мощности

- •Тема 4. Импульсные и автогенерирующие устройства

- •4.1. Генерирующие и импульсные устройства. Передачи информации в импульсном режиме

- •4.2. Электронные ключи. Простейшие формирователи импульсных сигналов

- •4.2.1. Ключевой режим работы транзистора

- •Режим насыщения

- •4.2.2. Компараторы (схемы сравнения)

- •4.2.3. Триггер Шмитта

- •4.2.4. Мультивибраторы

- •4.2.5. Дифференцирующие rc цепи

- •4.2.6. Интегрирующие rc-цепи

- •4.2.7. Симметричный мультивибратор на оу

- •4.2.8. Одновибратор на оу

- •4.3. Генераторы линейно-изменяющегося напряжения (глин) на оу

- •4.3.1. Глин на оу с внешним запуском

- •4.3.2. Глин на оу в автогенераторном режиме.

- •4.4. Генераторы гармонических колебаний. Условия возникновения колебаний

- •4.4.1. Условия возникновения колебаний

- •4.4.2. Генераторы с rc-фазосдвигающими цепочками

- •4.4.3. Генераторы с мостом Вина

- •Тема 5. Цифровая электроника и микропроцессорная техника

- •5.1. Основные логические операции и их практическая реализация

- •5.1.1. Операция "не" (логическое отрицание или "инверсия")

- •5.1.2. Операция "или" (логическое сложение или дизъюнкция)

- •5.1.3. Операция "и" (логическое умножение или конъюнкция)

- •5.2. Типы логических микросхем

- •5.3. Элементы алгебры логики и синтеза комбинационных схем. Формы записи логических уравнений

- •5.3.1. Формы записи логических уравнений

- •5.3.2. Синтез комбинационных логических устройств

- •5.3.3. Реализация логических функций на элементах "и-не" и "или-не"

- •5.4. Интегральные комбинационные схемы

- •5.5. Логические устройства последовательного типа

- •5.5.1. Триггеры

- •5.5.2. Счётчики

- •5.5.3. Регистры

- •5.6. Цифровые запоминающие устройства

- •5.6.1. Структуры запоминающих устройств

- •5.7. Аналого-цифровые и цифро-аналоговые преобразователи

- •5.7.1. Аналого-цифровые преобразователи

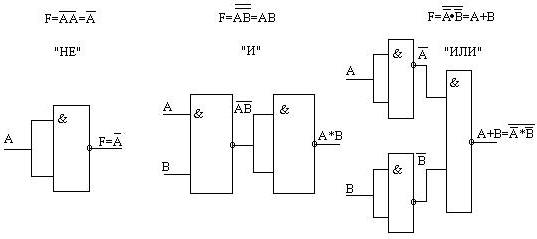

5.3.3. Реализация логических функций на элементах "и-не" и "или-не"

1. Выполнение функций на элементах "И-НЕ" можно проследить на рис. 5.3.5., а, б, в.

а) б) в)

Рис. 5.3.5. Выполнение функций F на элементах "И-НЕ"

2. Выполнение функций на элементах "ИЛИ-НЕ" на рис. 5.3.6, а, б, в.

а) б) в)

Рис. 5.3.6. Выполнение функций F на элементах "ИЛИ-НЕ"

Вышеприведенные упрощения производились на основе тождеств преимущественно интуитивно, что достаточно сложно. На практике для функций с числом переменных до пяти, шести наиболее удобным методом минимизации является применение диаграмм Вейча (или карт Карно).

5.4. Интегральные комбинационные схемы

Цифровые логические устройства подразделяются на два класса: комбинационные и последовательностные (или последовательные).

Комбинационные цифровые устройства реализуют различные преобразования двоичных цифровых сигналов на основе комбинационных логических функций. Выходные сигналы комбинационных устройств в любой момент времени однозначно определяются входными сигналами, имеющими место в этот момент времени.

К основным типам таких устройств относятся сумматоры, дешифраторы и шифраторы, преобразователи кодов, мультиплексоры и демультиплексоры, схемы сравнения двоичных чисел и др.

Ранее рассматривалось построение комбинационных логических устройств на основе элементов "И-НЕ" либо "ИЛИ-НЕ". В настоящее время благодаря развитию СИС и БИС широко применяются готовые комбинационные узлы, выполненные в одном корпусе. Это не только упрощает разработку схем, но и снижает стоимость оборудования, поэтому разработчик должен стремиться к наиболее широкому использованию имеющейся номенклатуры комбинационных ИМС для построения устройств.

Ниже будут рассмотрены наиболее распространенные комбинационные ИМС.

Дешифраторы (декодеры) – это такие комбинационные устройства, в которых каждой комбинации входных переменных соответствует логическая единица только на одном соответствующем входе

Таблица 5.4.1.

|

|

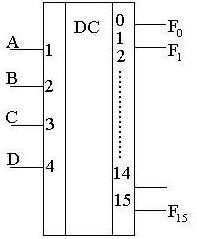

Рис. 5.4.1. Обозначение дешифратора

Таблица истинности дешифратора с четырьмя входами А, В, С, D приведена в таблице 5.4.1. Число выходов N=2n=16 – это максимальное значение при n=4, бывает, что N=10, 12. Сам дешифратор показан на рис.5. 4.1.

Дешифратор реализует следующие логические функции:

![]() .

.

Дешифраторы широко применяются, как преобразователи двоичного кода в десятичный (к примеру для управления индикаторными приборами).

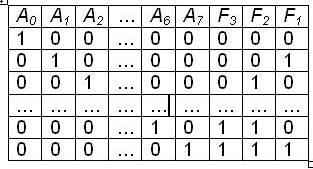

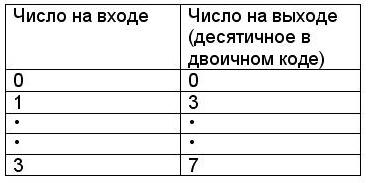

Шифраторы (кодеры) – устройства, выполняющие функции обратные тем, что выполняет дешифратор. Соответственно он имеет малое число выходов и большое входов. Обозначается он, как показано на рис. 5.4.2. на 3 выхода. При подаче сигнала на один из входов на его выходах появляется соответствующая комбинация логических единиц. Так, если Ао=1, а все остальные Аi, (где i от 0 до 7), равны нулю, то на выходе получаем код 000; если А6=1, то код на выходе 110; если А7=1, то 111. Таблица 5.4.2. даёт представление о всех возможных комбинациях на выходе при наличии логической единицы на каждом из входов.

Таблица 5.4.2.

|

|

Рис. 5.4.2. Обозначение шифратора.

Совокупность дешифратора с шифратором позволяет строить преобразователи кодов, как показано на рис. 5.4.3. Соединение дешифратора DС и шифратора СD (декодер и кодер) может быть самым различным. Работа определяется таблицей соответствий, пример которой приведен в таблице 5.4.3.

Рис. 5.4.3. Преобразователь кодов

Таблица 5.4.3.

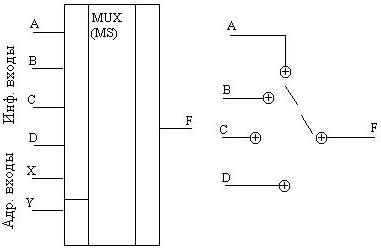

Мультиплексоры – это комбинационные устройства, в которых выход соединяется с одним из входов в зависимости от кода адреса, как показано на рис. 5.4.4., а) и б).

Таблица 5.4.5.

|

|

a) б)

Рис. 5.4.4. Обозначение мультиплексора

В соответствии с таблицей 5.4.5., если:

X, Y=00, тоF=A;

X,Y=01,F=B;

X, Y=10,F=C;

X, Y=11,F=D

Описывается работа приведенного мультиплексора следующим логическим уравнением:

![]() ;

;

Мультиплексоры применяются в устройствах отображения информации, в ЭВМ в микропроцессорных устройствах управления.

Кроме того,

мультиплексоры могут работать и как

логические устройства. К примеру, если

надо реализовать функцию: F=![]() Y+X

Y+X![]() ,

то можно поступить так (см. таб. 5.4.5.):

возьмем А=0,

D=0, а В=С=1,

тогда используя уравнение мультиплексора

получаем желаемый результат.

,

то можно поступить так (см. таб. 5.4.5.):

возьмем А=0,

D=0, а В=С=1,

тогда используя уравнение мультиплексора

получаем желаемый результат.

Демультиплексоры – это устройства, в которых значение функции F на входе подается на тот выход (А, В, С или D), адрес которого указан на адресных входах X, Y. Обозначение показано на рис. 5.4.5. Это устройство равнозначно дешифратору с дополнительным входом V=F, значение сигнала, на котором определяет значение сигнала на соответствующем выходе дешифратора, как это показано в таблице 5.4.6.

Таблица 5.4.6.

|

|

Рис. 5.4.5. Обозначение демультиплексора

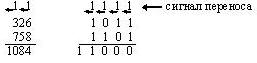

Сумматоры – это устройства, предназначенные для выполнения операции сложения чисел, заданных в двоичном коде. Для установления правил сложения сравним сложение десятичных и двоичных чисел.

Правила сложения:

1) сложение выполняется поразрядно от младшего к старшему;

2) в младшем разряде

вычисляется сумма младших разрядов

слагаемых

![]() и

и

![]() ,

которая записывается либо однозначным

числом

,

которая записывается либо однозначным

числом

![]() (0+1=1),

либо двузначным

(0+1=1),

либо двузначным

![]() (1+1=10),

где функция P

называется переносом;

(1+1=10),

где функция P

называется переносом;

3) во всех последующих

разрядах находится сумма разрядов

слагаемых

![]() и

и

![]() ,

причем при

,

причем при

![]() к

этой сумме добавляется единица переноса.

к

этой сумме добавляется единица переноса.

Результат сложения

записывается в i-ом

разряде в виде однозначного числа

![]() или

двузначного

или

двузначного

![]() .

Вывод: в каждом i-ом

разряде находится сумма чисел

,

и

.

Вывод: в каждом i-ом

разряде находится сумма чисел

,

и

![]() (если

),

т.е. определяется

и

(если

),

т.е. определяется

и

![]() .

.

Одноразрядный сумматор показан на рис. 5.4.6., его таблица истинности приведена в табл. 5.4.7.

Таблица 5.4.7.

|

|

Рис. 5.4.6. Обозначение одноразрядного сумматора

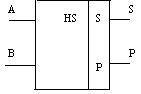

Полусумматоры – устройства, отличающиеся от одноразрядного сумматора отсутствием входа сигнала переноса . Его обозначение показано на рис. 5.4.7, а работа отражена в табл. 5.4.8.

Таблица 5.4.8.

|

|

Рис. 5.4.7. Обозначение полусумматора

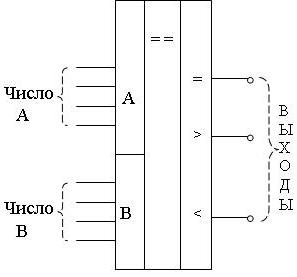

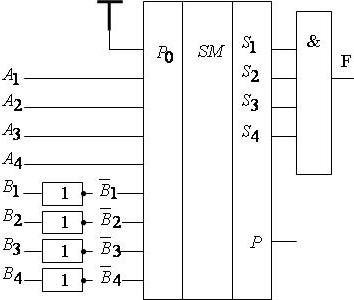

Цифровые схемы сравнения – устройства, которые формируют на соответствующих выходах "1" в зависимости от результатов сравнения двух чисел. Обозначение показано на рис. 5.4.8. На рис. 5.4.9. приведена схема сравнения, выполненная на базе многоразрядного сумматора и схемы "И".

|

|

Рис. 5.4.8. Обозначение устройства сравнения |

Рис. 5.4.9. Схема сравнения, выполненная на базе многоразрядного сумматора и схемы "И" |

Действительно,

если А=В,

то сумма

![]() =1

=1

А0 1 0 1

1 0 1 0

S 1 1 1 1

![]()

Тогда:

![]()

Схема на рис. 5.4.9. может фиксировать и неравенство чисел А и В. Так, если А<В, то F=0 и P=0; если А=В, то F=1, P=0, а если А>В, то F=0, P=1, т.е. выдается сигнал переполнения.

Цифровая схема сравнения может рассматриваться, как цифровой аналог компаратора.