- •Лекция 4. Элементы последовательной логики, триггеры.

- •Лекция 5. Генераторы и формирователи импульсов

- •Лекция 7. Счетчики.

- •Лекция 8. Цифровые устройства – дешифратор, мультиплексор.

- •7Как следует из таблицы состояния, каждой функции соответствует только один минтерм, следовательно, не требуется минимизировать эти функции (рис. 2.9).

- •Лекция 9 Схемы большой степени интеграции Сумматор основа алу

7Как следует из таблицы состояния, каждой функции соответствует только один минтерм, следовательно, не требуется минимизировать эти функции (рис. 2.9).

Из полученных уравнений и схемы дешифратора следует, что для реализации полного дешифратора на m входов (переменных) потребуются n = 2m элементов конъюнкции (количество входов каждого элемента “И” равно m)и m элементов отрицания.

Дешифратор

Рис 7.12

Мультиплексор – это цифровой коммутатор. Он выполняет операцию передачи сигнала с каждой из заданных ее входным адресом линии в выходную линию.

Рис 7.13

Мультиплексор на логических элементах.

У мультиплексора один выход (y), а число (m) входных информационных линий (x) определяется количеством (n) входов адреса (a) формулой m = 2n. Ниже рассмотрен мультиплексор с n=2. При а1=0 и а0=0 на выход у проходит сигнал со входа х0, т.е. в этом случае у=х0. При а1=0 и а0=1 на выход проходит сигнал со входа х1, т.е. у=х1 и т.д.

Таблица истинности мультиплексора:

-

a1

a0

y

0

0

x0

0

1

x1

1

0

x2

1

1

x3

Уравнение запишем в первой стандартной форме:

![]() (9)

(9)

Сравнивая это уравнение с уравнениями дешифратора (8), можем заметить, что дешифратор является составной частью мультиплексора, поэтому схему мультиплексора (рис. 24) будем строить с использованием дешифратора.

Рис. 7.14. 24. Схема мультиплексора (а) и его условное обозначение (b)

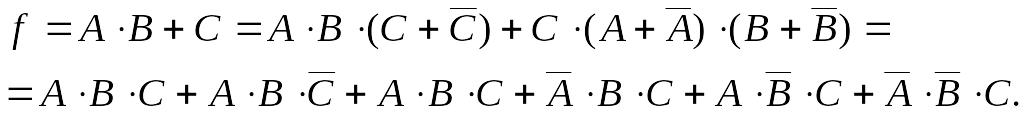

Особое

значение имеет мультиплексор как

средство для реализации булевых функций.

На одном мультиплексоре с m адресными

входами можно построить любую булеву

функцию от m+1 аргументов. Для этого

заданную булеву функцию необходимо

преобразовать к уравнению мультиплексора

(9), т.е. дополнить до первой стандартной

формы. Например, в функции f=AB+C

необходимо AB

домножить на скобку

![]() ,

а C домножить на

,

а C домножить на

![]() .

.

При подаче на адресные входы (а1, а0) сигналов A и B получим уравнение, приведенное к виду уравнения мультиплексора:

![]() (10)

(10)

На входы х0, х1, х2 мультиплексора подается сигнал С, на вход х3 – сигнал уровня логической 1. Если на адресные входы подать сигналы B и С, то получим:

![]() (11)

(11)

На вход х0 подаем сигнал уровня логического 0, на входы х1 и х3 сигналы уровня логической 1, на вход х2 – сигнал А. Третий вариант – на адресные входы подаем сигналы А и С. Уравнение имеет вид:

![]() (12)

(12)

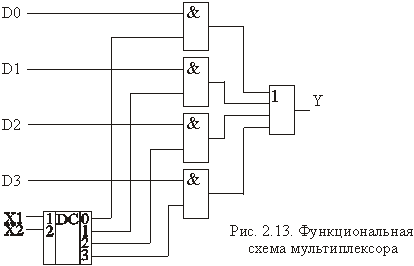

На вход х0 подаем нулевой сигнал, на входы х1 и х3 – сигнал единичный, на вход х2 – сигнал В (рис. 25).

Рис.7.15 25. Схемы с применением мультиплексора по уравнениям 10 (а), 11 (b) и 12 (с)

Демультиплксор

Рис 7.16

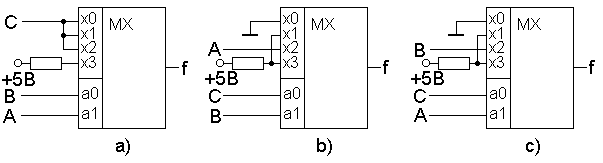

Мультиплексор - коммутатор цифровых сигналов. Мультиплексор представляет собой комбинационное устройство с m информационными, n управляющими входами и одним выходом. Функционально мультиплексор состоит из m элементов конъюнкции, выходы которых объединены дизъюнктивно с помощью элемента ИЛИ с m входами. На одни входы всех элементов конъюнкции подаются информационные сигналы, а другие входы этих элементов соединены с соответствующими выходами дешифратора с n входами.

Функциональная схема мультиплексора приведена на рис.2.13.

Из рис. 2.13. следует, что мультиплексор содержит дешифратор на соответствующее число выходов (число выходов дешифратора определяется числом информационных входов мультиплексора), элементы конъюнкции на два или на три входа каждый и элемент дизъюнкции с числом входов, равным количеству информационных линий D0 . . . Dm. Число входов элементов И может быть равным только двум, однако, во многих случаях возникает необходимость стробирования выходного сигнала мультиплексора импульсами независимого источника. В таких случаях в структуре мультиплексора используются элементы И с тремя входами. Одни из входов всех элементов конъюнкции, в последнем случае, объединяются, и по этой линии подается сигнал разрешения работы мультиплексора (стробирующий сигнал). Наличие дополнительного управляющего входа расширяет функциональные возможности мультиплексора и позволяет проще реализовать методы борьбы с гонками.

На рис. 2.14 показано обозначение мультиплексора на принципиальных и функциональных электрических схемах.

Из уравнения мультиплексора видно, что на его выход будет передаваться сигнал только с одного входа, номер которого совпадает с числом, соответствующим кодовой комбинации Х1 и Х2. Если Х1=Х2=0, на выход мультиплексора будет передаваться сигнал с входа D0. Когда на адресных (управляющих) входах Х1=1 и Х2=0, то на выход будет передаваться сигнал с входа D1 и т.д.

Мультиплексоры нашли широкое применение в вычислительной технике в качестве коммутаторов цифровых сигналов. Они используются в компьютерах и микропроцессорных контроллерах для коммутации адресных входов динамических оперативных запоминающих устройств, в узлах объединения или разветвления шин и т.д. На базе мультиплексоров можно построить различные комбинационные устройства с минимальным числом дополнительных элементов логики. Следует отметить, что мультиплексоры хотя, и предназначены для коммутации цифровых сигналов, но с помощью мультиплексоров, изготовленных по КМОП технологии, можно коммутировать и аналоговые сигналы.

Универсальные логические модули (УЛМ) на МS. Кроме ком-мутационных функций, мультиплексоры позволяют реализовать комбинационные устройства на m (m-количество управляющих входов) входов и на один выход. Если комбинационное устройство, построенное на базе мультиплексора, не требует подключения дополнительных элементов логики, оно называется универсальным логическим модулем. Отметим, что мультиплексор 8 ®1 (3 управляющих и 8 информационных входов) позволяет реализовать любую функцию трёх переменных.

Для получения УЛМ управляющие входы мультиплексора представляют как информационные, а информационные входы - как настроечные (следовательно, у мультиплексора 8 ®1 будут три информационных и 8- настроечных входов).

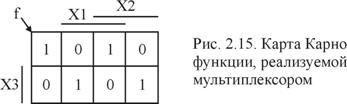

Пусть функция задана в виде карты Карно (рис.2.15).

При построении УЛМ на карте Карно. записывается СHДФ с учетом состояния информационных (настроечных) входов мультиплексора.

![]()

Cопоставляя полученную СHДФ с формулой мультиплексора, определяем номера коэффициентов “а”, т.е.

![]()

Следовательно, эти коэффициенты равны единице, т.е. D0 = D3 = D5= D6 = 1, а на остальных настроечных входах логические нули, т.е. D1 = D2 = D4 = D7 = 0.

Схема комбинационного устройства, построенного на базе мультиплексора 8-1 и реализующего функцию f (x), приведена на рис. 2.16.

Как следует из рис. 2.16, построение комбинационного устройства на базе мультиплексора сводится к объединению настроечных входов так, чтобы получилось две группы. К одной группе входов, в соответствии с заданной функцией, подают логический “0”, а другой - “1”.

На базе мультиплексоров можно синтезировать комбинационные устройства, которые могут реализовать функции на большее число переменных, чем количество управляющих входов мультиплексора. Очевидно, и в этом случае, мультиплексор сохраняет свою универсальность, так как часть переменных реализуемой функции непосредственно подается на входы Х1 . . . Хm мультиплексора (количество переменных, непосредственно подаваемых на управляющие входы мультиплексора равно m).

Синтез комбинационного устройства на мультиплексоре, реализующего функцию с числом переменных больше, чем число управляющих входов мультиплексора. Часто использование мультиплексора при синтезе КУ существенно упрощает этот процесс и схему цифрового автомата.

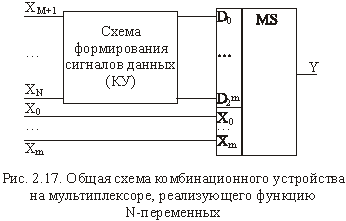

В общем случае, когда требуется синтезировать КУ, реализующее функцию N аргументов на мультиплексоре с M управляющими входами и 2М информационными входами, М младших переменных из набора Х1, Х2, . . . . ХN следует подать на управляющие входы, а информационные сигналы (настроечные) D0, D1, . . . . D2м нужно представить функциями остальных (N - M) переменных, как показано на рис. 2.17. Тогда синтез КУ сводится, по сути дела, к синтезу схемы формирования информационных сигналов, которую можно рассматривать как внутреннее более простое КУ.

Рассмотрим пример синтеза КУ для реализации функции пяти переменных на мультиплексоре с двумя управляющими входами. Тогда “младшие” переменные Х1 и Х2 подаются на управляющие входы Х1и Х2, соответственно. Выходную функцию Y будет определять карта Карно управления информационными входами (рис. 2.18). Каждый информационный сигнал, в свою очередь, является функцией трех переменных: Х3, Х4, Х5. Для каждого информационного сигнала можно составить карту Карно и с её помощью минимизировать логическое выражение функций D0, D1, D2 и D3. По минимизированным логическим выражениям строится схема формирования информационных сигналов (настройки) в любом известном базисе.

На мультиплексорах с двумя управляющими входами легко можно синтезировать КУ при числе переменных N £ 6. На мультиплексорах с тремя и четырьмя управляющими входами можно синтезировать функции и большего количества переменных. Карты управления информационными входами для этих случаев показаны на рис. 2.18.

При синтезе КУ на мультиплексорах можно использовать следующий алгоритм действий:

-составить таблицу истинности КУ;

-подать на управляющие входы мультиплексора младшие переменные;

-представить информационные сигналы функциями остальных переменных и составить карту Карно для каждого информационного сигнала;

- минимизировать логические выражения для сигнала на каждом информационном входе;

- по логическим выражениям составить схему формирования сигналов, подаваемых на информационные входы мультиплексора.

Синтез комбинационного устройства-преобразователя кода

Синтез комбинационного устройства рассмотрим на примере реализации преобразователя кода для семисегментных индикаторов. Будем считать, что светодиодные семисегментные индикаторы выполнены с общим катодом, т.е. сегменты высвечиваются при подаче на них уровня логической единицы. Преобразователь кода представим в виде дешифратора с семью выходами (количество выходов КУ равно количеству реализуемых функций). Схема соединения выводов преобразователя к сегментам индикатора приведена на рис. 2.5. Обозначение сегментов индикатора стандартное и соответствует общепринятым

нормам. В данном случае будем считать, что сегменты будут высвечиваться при подаче на них уровня логической “1”.

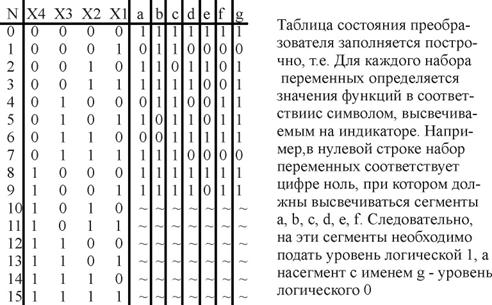

Пусть обозначения функций соответствуют именам сегментов, тогда таблица состояния функций будет выглядеть так

Для зажигания цифры 1 необходимо подать уровни логической “1” на сегменты “b” и “c” и т.д. Преобразователь предназначен для индикации цифр десятичной системы счисления, и поэтому значения функций для наборов переменных, начиная с номера 10, для индикатора безразличны. Безразличные значения функций обозначены знаком ~ (тильда).

После заполнения таблицы состояния устройства составляются аналитические выражения (СНДФ) для каждой функции и строятся карты Карно, предназначенные для минимизации этих функций. Карты Карно можно заполнять и без записи СНДФ, что сократит количество действий разработчика при синтезе устройства. Очевидно, что без минимизации функции преобразователя получились бы весьма громоздкими, т.к. каждая содержала бы по девять минтермов, состоящих из четырех переменных. Порядок составления карт Карно и получения минимальных НДФ роли не играют. Для удобства с точки зрения последовательности изложения алгоритма действий, минимизацию начнем с функции а (рис.2.6), реализующей индикацию цифры 0.

Для функции b карта Карно представлена на рис.2.7. Она содержит три контура, следовательно, МДФ будет содержать всего три простых конъюнкции.

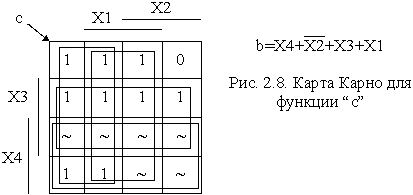

Карта Карно для функции “c” представлена на рис.2.8. Она содержит четыре контура, следовательно, функция будет содержать тоже четыре минтерма.

Аналогично строятся карты Карно и записываются минимальные ДФ и для других функций. После получения всех МДФ производят выбор требуемого базиса логических элементов и составляют принципиальную схему. Многие фрагменты отдельных функций могут быть использованы при реализации общих для этих функций операций. В общем случае, принципиальную схему преобразователя кода можно построить на базе элементов И-ИЛИ-НЕ.

Вопросы по теме

явление гонок в цифровых схемах

шифратор

дешифратор

мультиплексор

демультиплексор

преобразователь кода

Вопросы для самопроверки

8.1. Какое устройство называется дешифратором?

8.2. Спроектируйте дешифратор 2х4 по нулям.

8.3. Начертите схему дешифратора с одним адресным входом.

8.4. Какое устройство называется мультиплексором?

8.5. Спроектируйте мультиплексор с одним адресным входом.

8.6. Начертите схему мультиплексора с одним адресным входом на элементах ИЛИ-НЕ, на элементах И-НЕ.