- •Теми для самостійного опрацювання з предмету “Комп’ютерна схемотехніка” Розділ 1. Основи двійкової арифметики

- •Тема 1.1. Подання чисел з фіксованою комою в розрядній сітці

- •Домашнє завдання

- •Ділення чисел з фіксованою комою

- •Алгоритм ділення модулів чисел без відновлення остач

- •Ділення з відновленням залишку

- •Тема 1.2. Виконання арифметичних операцій над числами з плаваючою комою (пк)

- •Розділ 2. Основи алгебри логіки (ало)

- •Тема 2.1 Основні функції та теореми алгебри логіки.

- •Домашнє завдання

- •Тема 2.2. Мінімізація логічних функцій

- •Розділ 3. Схемотехніка комбінаційних схем

- •Тема 3.1. Дешифратори та шифратори. Селектори та мультиплексори.

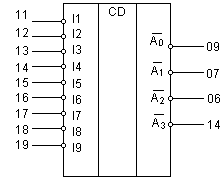

- •11, 12, 13, 14, 15, 16, 17, 18, 19 – Інформаційні входи;

- •09, 07, 06, 14 – Інформаційні виходи. Побудова універсальних логічних модулів (улм) за допомогою ms

- •Тема 3.2. Перетворювачі кодів

- •Перетворювач двійково–десяткових чисел в код семисегментного індикатора.

Розділ 3. Схемотехніка комбінаційних схем

Тема 3.1. Дешифратори та шифратори. Селектори та мультиплексори.

Лекція №8. Лінійні та каскадні дешифратори

Лінійні дешифратори

Функціонування лінійного (прямокутного) дешифратора описується системою n логічних функцій fi , i = 0,1…,2n - 1 (див. табл. 1).

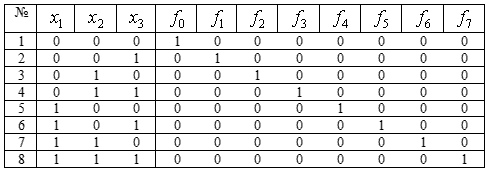

Таблиця 1 – Таблиця істинності лінійного дешифратора с n = 3 входами

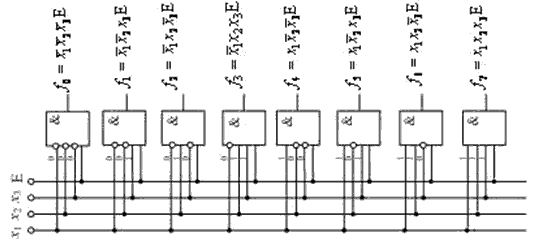

На рис. 1 наведена функціональна схема лінійного дешифратора для трьох вхідних змінних x1, x2, x3, які містять відповідно 2n = 23 = 8 виходів.

Рис. 1. Функціональна схема лінійного дешифратора

Кількість входів, які містяться в лінійному дешифраторі:

N = (n + 1) ∙ 2n (1)

Для n = 3 число N = 4∙23 = 32.

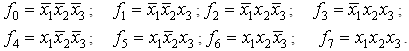

Аналітичне подання функцій виходу дешифратора f0,…f7 має вид:

Каскадні дешифратори

Лінійні дешифратори є найбільш швидкодіючими. Однак їх реалізація з великою розрядністю вхідних слів утруднена, оскільки потрібно виготовити для однієї мікросхеми з n входами, яка виконує функції дешифратора, 2n контактних площадок для реалізації його виходів. А ще потрібні контактні площадки для входів, блока живлення, сигналів управління мікросхемою в цілому. Тому часто ставиться задача виготовлення дешифратора з великим числом контактних площадок на основі мікросхем з обмеженою кількістю контактів. Для цього схема дешифратора складається з декількох каскадів лінійних дешифраторів. Найчастіше ця кількість дорівнює двом. При цьому перший каскад керує мікросхемами - дешифраторами другого каскаду, другий – мікросхемами - дешифраторами третього каскаду і т.д. Якщо це двокаскадний дешифратор, то дешифратор першого каскаду, який один, і кожен з 4 дешифраторів другого каскаду дешифрує 2 вхідних розряди. Одночасно один з 4 виходів дешифратора першого каскаду дає дозвіл на роботу відповідного йому дешифратора другого каскаду. В результаті на одному з виходів цього дешифратора з’явиться сигнал. На виходах інших трьох дешифраторів в цей час поява сигналів буде заборонена. розрядів Оскільки дешифраторів в другому каскаді 4, то сумарно дешифратор має 16 виходів (див. рис. 2). При цьому тільки на одному з цих 16 виходів буде знаходиться одиничний сигнал.

Рис. 2. Функціональна схема двокаскадного дешифратора.

Лекція 9с. Дешифратори на СІС

Дешифратор – функціональний вузол комп’ютера призначений для перетворення кожної комбінації вхідного двійкового коду в керуючий сигнал лише на одному із “m” виходів.

Дешифратори - мікросхеми середньої інтеграції, призначені для перетворення двійкового коду в напругу логічного рівня на виході, який відповідає даному двійковому коду. Наприклад, вхідний код 0101 повинен зробити активним вивід з номером 5. На всіх інших виводах дешифратору сигнали повинні бути нульовими.

В сучасному обладнанні зв'язку дешифратори реалізовані наступними мікросхемами, табл.1.:

Таблиця 1

ТИП ТЕХНОЛОГІЇ |

|

ТТЛ |

КМОН |

КР1533ИДЗ, КР1533ИД4, КР1533ИД7, КР1533ИД14,КР1533ИД17, К514ИД2, КР1531ИД7, КР153ШД14, К514ИД1. |

КР1554ИД14, КР1561ИД6, КР1561ИД7, 564ИД1, 564ИД4, 564ИД5 |

Розглянемо умовне графічне зображення і функціональні можливості деяких реальних мікросхем.

ПРИКЛАД 1: КР1533ИДЗ (Рис.1) - дешифратор-демультиплексор 4х16 (перетворення двійково-десяткового коду в десятковий).

Даний дешифратор дозволяє перетворювати 4-розрядний код на входах 1-2-4-8 в напругу низького рівня на одному з виходів 0...15, табл.2. Дешифратор має два входи дозволу дешифрації С1, С2. Щоб дозволити проходження даних на виходи, необхідно на С1, С2 подати напругу низького рівня (лог. 0).

Даний дешифратор можна використовувати як демультиплексор. При цьому адресами будуть входи 1-2-4-8. Один з входів стробування, наприклад С1, можна використовувати як інформаційний, а на другий, в даному випадку С2 (вхід стробування), потрібно подати напругу лог.0.

Мікросхема КР1533ИДЗ споживає струм 15 мА, tз,р = 30...36 нс.

КР1533ИДЗ

Рис.1. Мікросхема КР1533ИД3 |

Призначення виводів 20...23- інформаційні входи 01-11,13.-17 - виходи 18,19 – входи стробування 24 - напруга живлення 12 - спільний вивід

|

КР1533ИДЗ Таблиця істинності Таблиця 2

Входи |

Виходи |

|||||||||||||||||||||

С1 |

С2 |

D4 |

D3 |

D2 |

D1 |

Y0 |

Y1 |

Y2 |

Y3 |

Y4 |

Y5 |

Y6 |

Y7 |

Y8 |

Y9 |

Y10 |

Y11 |

Y12 |

Y13 |

Y14 |

Y15 |

|

L L L L L L L L L L L L L L L L L H H |

L L L L L L L L L L L L L L L L H L H |

L L L L L L L L H H H H H H H H X X X |

L L L L H H H H L L L L H H H H X X X |

L L H H L L H H L L H H L L H H X X X |

L H L H L H L H L H L H L H L H X X X |

L H H H H H H H H H H H H H H H H H H |

H L H H H H H H H H H H H H H H H H H |

H H L H H H H H H H H H H H H H H H H |

H H H L H H H H H H H H H H H H H H H |

H H H H L H H H H H H H H H H H H H H |

H H H H H L H H H H H H H H H H H H H |

H H H H H H L H H H H H H H H H H H H |

H H H H H H H L H H H H H H H H H H H |

H H H H H H H H L H H H H H H H H H H |

H H H H H H H H H L H H H H H H H H H |

H H H H H H H H H H L H H H H H H H H |

H H H H H H H H H H H L H H H H H H H |

H H H H H H H H H H H H L H H H H H H |

H H H H H H H H H H H H H L H H H H H |

H H H H H H H H H H H H H H L H H H H |

H H H H H H H H H H H H H H H L H H H |

|

L - низький рівень напруги

Н - високий рівень напруги

X – будь-який рівень напруги

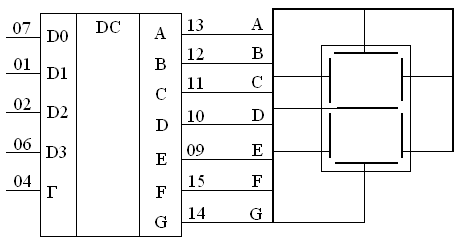

ПРИКЛАД 2: К514ИД1 ,КР514ИД1,514ИД1 (Рис.2) - дешифратори для представлення чотирьох-розрядного двійкового коду в сигнали 7-сегментного коду. Призначені для керування напівпроводніковими цифро-літерними індикаторами на основі світло випромінюючих діодних структур з роз'єднаними анодами.

Рис. 2. Мікросхема К514ИД1

Призначення виводів |

Дешифрування вхідних сигналів виникає при встановленні високого логічного рівня на вході Г. При цьому вхідній інформації (на виводах D3, D2, D1, D0) 0000 буде відповідати вихідна (на виводах A, B, C, D, E, F, G) 1111110, що обумовлює збудження на індикаторі символу 0. |

D0 – D3 - інформаційні входи; Г-вхід гашення; А,В,С,D,Е,F,С – виходи для підключення до ССІ 16-Uжив; 8-спільний. |

|

Сигнал низького логічного рівня на вході Г (вхід гашення) становить всі виводи дешифратора в стан логічних нулів (незалежно від вхідної інформації),при цьому ні один сегмент індикатора не горить. |

|

ПРИКЛАД 3: КР1533ИД4 ( Рис.3 ) - Мікросхема має окремі для кожної частини стробуючі входи С, спільні адресні входи SЕ1,SЕ2, а також відділені інформаційні входи 0,причому для кожної схеми при передачі на вихід інформація інвертуеться.Високий рівень напругі на стробуючіх входах становить високий рівень напругі на виходах незалежно від стану других входів.При низьком рівне напругі на вході С здісьнюеться дешифрування коду ,поданого на входи 8Е1,8Е2.При використанні мікросхеми як демультиплексора входи 8Е1,8Е2 використуються як селектуючі.

Мікросхема може використовуватися як:

|

|

Рис.3. КР1533ИД4 |

Призначення виводів

01, 15 – виходи даних 02, 14 – входи стробування 03, 13 – вибір даних 04…07, 09…12 – виходи 16 – напруга живлення 08 – спільний вивід

|

Лекція №10с. Комбінаційні пристрої на ІМС

Шифратори, які при одночасному натисканні декількох клавіш виробляють код тільки старшої цифри, називаються пріоритетними. Пріоритетні шифратори, які призначені для пошуку старшої (лівої) одиниці в слові та формування на виході двійкового номера шуканого розряду, називаються покажчиками старшої одиниці. Їх застосовують у пристроях нормалізації чисел з плаваючою комою, в системах з пріоритетним обслуговуванням запитів на переривання роботи комп'ютера.