- •28 Зао “контраст” Контроллеры многофункциональные кр-300, кр-300м

- •Окл (02)Оперативный контроль логической программы

- •Огу (03)Оперативный групповой контроль и управление

- •Дик (04)Дискретный контроль

- •Алгоритмы обмена по сети магистр

- •Вин (05)Ввод интерфейсный сетевой

- •Инв (06)Интерфейсный вывод сетевой

- •Инр (07)Интерфейсный вывод радиальный

- •Вип (08)Ввод интерфейсный полевой*

- •Усо (09)усо-1 *

- •Алгоритмы ввода-вывода информации с усо

- •Ва (10)Ввод аналоговый

- •Вд (11)Ввод дискретный

- •Вап(12)Ввод аналоговый помехозащищенный *

- •Ав (13)Аналоговый вывод

- •Дв (14)Дискретный вывод

- •Ив (15)Импульсный вывод

- •Ав8 (16)Аналоговый вывод на 8

- •Алгоритмы системного контроля

- •Авр (17)Аварийный вывод

- •Кпп (18)Контроль пропажи питания

- •Ссо (19)Супервизор сетевого обмена

- •Алгоритмы регулирования

- •Ран (20)Регулирование аналоговое

- •Рим (21)Регулирование импульсное

- •Рпи (22)пи-регулятор

- •Входы -выходы алгоритма рпи

- •Здн (24)Задание

- •Здл (25)Задание локальное

- •Руч (26)Ручное управление

- •Прз (27)Программный задатчик

- •Инз (28)Интегрирующий задатчик

- •Прк (29)Пороговый контроль

- •Динамические преобразования

- •Инт (33)Интегрирование

- •Диф (34)Дифференцирование

- •Фил (35)Фильтрация

- •Дин (36)Динамическое преобразование

- •Диб (37)Динамическая балансировка

- •Огс (38)Ограничение скорости

- •Зап (39)Запаздывание

- •Фвп (40)Фильтр высокочастотной помехи

- •Фпм(41) – Фильтр помех

- •Статические преобразования

- •Сум (42)Суммирование

- •Сма (43)Суммирование с масштабированием

- •Умд (44)Умножение-деление

- •Кор (45)Корень квадратный

- •Мод (46)Модуль сигнала

- •Кус (47)Кусочно-линейная функция

- •Огр (48)Ограничение

- •Скс (49)Скользящее среднее

- •Дис (50)Дискретное среднее

- •Мин (51)Минимум

- •Мкс (52)Максимум

- •Сит (53)Среднее из трех

- •Экс (54)Экстремум

- •Мсш (55)Масштабирование

- •Смз (56)Суммирование с выделением модуля и знака

Огр (48)Ограничение

Назначение.

Алгоритм используется для ограничения верхней и (или) нижней границы диапазона изменения сигнала.

Описание алгоритма.

Алгоритм содержит ограничитель верхнего и нижнего значения сигнала. На двух дискретных выходах Dв и Dн фиксируется достижение сигналом верхней и нижней границы ограничения.

Работа алгоритма определяется следующей таблицей

|

X |

Y |

Dв |

Dн |

|

Хв>Х>Xн |

Х |

0 |

0 |

|

ХХв |

Хв |

1 |

0 |

|

ХХн |

Хн |

0 |

1 |

Алгоритм будет правильно работать, только если Хв>Хн.

Уровни ограничений задаются настроечными входами Хв, Хн.

Режимы работы.

Для последующих алгоритмов алгоритм ОГР не инициирует обратный счет, но если на каскадный выход Y поступит команда отключения со значением начальных условий Yo или команда запрета, эти сигналы транслируются предвключенному алгоритму через каскадный вход Х. Величина Yо может превысить установленные уровни ограничения. Ограничитель этому не препятствует, на выходах Dв и Dн алгоритма при этом формируются дискретные сигналы: Dв=1 и Dн=0 при Yо>Xв; Dв=0 и Dн=1 при Yо<Хн.

После включения алгоритма выходной сигнал может находиться за порогами ограничения, однако изменение выходного сигнала возможно лишь в направлении, приближающем его к порогу ограничения. Если выходной сигнал изменяется именно в этом направлении, сигналы запрета не формируются.

Модификатор МР и масштаб времени МВ отсутствует.

Входы-выходы алгоритма ОГР и его функциональная схема приведены ниже.

Входы-выходы алгоритма ОГР

|

Номер |

Обозначение |

Вх-Вых |

Назначение |

|

01 |

Х |

Вход |

Основной вход алгоритма (каскадный) |

|

02 |

Хв |

“ |

Верхняя граница ограничения |

|

03 |

Хн |

“ |

Нижняя граница ограничения |

|

01 |

Y |

Выход |

Основной выход алгоритма (каскадный) |

|

02 |

Dв |

“ |

Достижение верхней границы |

|

03 |

Dн |

“ |

Достижение нижней границы |

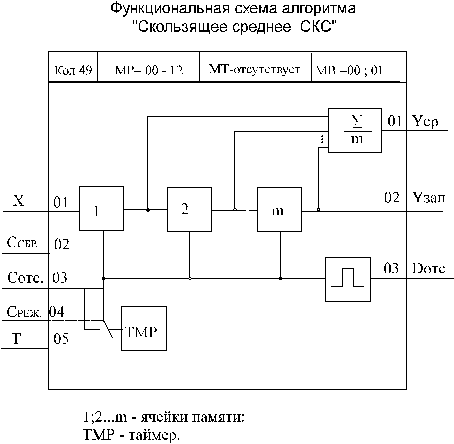

Скс (49)Скользящее среднее

Назначение.

Алгоритм применяется для вычисления среднего из нескольких (до 21) последних отсчетов аналогового сигнала.

Описание алгоритма.

Структура и работа алгоритма СКС соответствует алгоритму запаздывания ЗАП. Отличие алгоритма СКС заключается в наличии дополнительного сумматора, который усредняет значение сигналов на выходах всех ячеек запаздывания. При этом выходной сигнал Yср равен:

m

Yср=( Xi)/m;

i=1

где 1<m<12 значение модификатора,

Хi значение сигнала на выходе i-ой ячейки памяти.

При m=0 выходной сигнал Yср=Х и признак отсчета Dотс=0.

Если требуемое число отсчетов при усреднении превышает 12, алгоритм СКС по аналогии с алгоритмами ЗАП включается последовательно, при этом с помощью алгоритма суммирования с масштабированием СМА сигнал Yср,n от каждого n-го алгоритма СКС суммируется и по каждому сигналу Yср,n устанавливается масштабный коэффициент:

L

Km,n=mn/( mn );

n=1

где mn модификатор n-го алгоритма СКС,

L общее число последовательно включенных алгоритмов СКС.

Полученная сумма будет равна искомому среднему значению.

При сигнале Ссбр=1 внутренний таймер обнуляется и вовсе ячейки памяти записывается текущее значение сигнала Х, при этом Yср=Х.

Алгоритм не имеет каскадных входов и выходов и блокирует процедуру обратного счета.

Модификатор МР=00-12, масштаб времени МВ=00,01.

Входы-выходы алгоритма СКС и его функциональная схема приведены ниже.

Входы-выходы алгоритма СКС

|

Номер |

Обозначение |

Вх-Вых |

Назначение |

|

01 |

Х |

Вход |

Основной вход |

|

02 |

Ссбр |

“ |

Команда сброса |

|

03 |

Сотс |

“ |

Команда отсчета |

|

04 |

Среж |

“ |

Выбор режима |

|

05 |

Т |

“ |

¦ Период отсчета |

|

01 |

Yср |

Выход |

Основной выход алгоритма |

|

02 |

Yзап |

“ |

Запаздывающее значение входа |

|

03 |

Dотс |

“ |

Признак отсчета |