- •2.2. Контроллер клавиатуры

- •2.3. Скэн-Коды

- •2.4. Интерфейс контроллера клавиатуры

- •2.5. Подключение клавиатуры

- •2.6. Драйвер клавиатуры

- •2.7. Обработка скэн-кодов, вывод символов на экран

- •Программа kbdscan

- •Программа kbdascii

- •2.8. Лицевая панель клавиатуры

- •2.9. Конструкция клавиш

- •2.10. Виды клавиатур, эргономические требования

- •Литература

2.4. Интерфейс контроллера клавиатуры

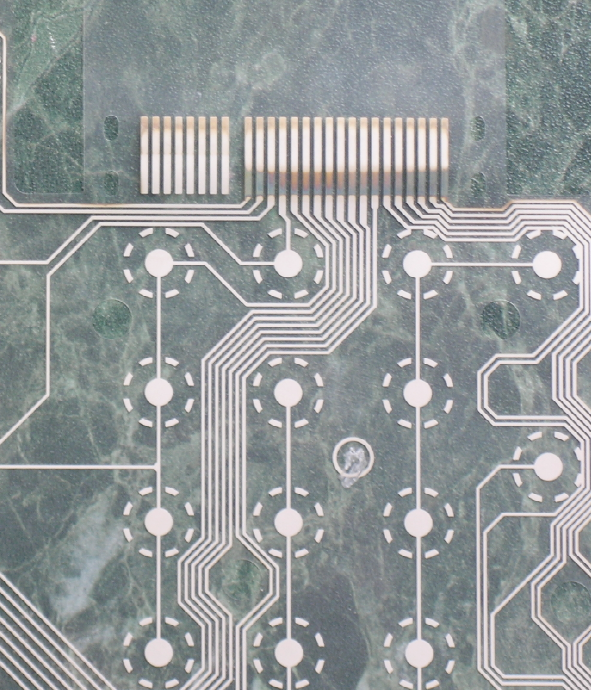

Клавиатура состоит из набора переключателей, объединенных в матрицу (рис. 3). При нажатии на клавишу контроллер клавиатуры, установленный в самой клавиатуре, определяет код нажатой клавиши в матрице. Он также определяет продолжительность нажатия и может даже обработать одновременное нажатие нескольких клавиш. В клавиатуре установлен собственный буфер емкостью 16 байт, в который заносятся данные (коды) при слишком быстрых или одновременных нажатиях на клавиши. Затем эти данные в соответствующей последовательности передаются в системный блок.

Рис. 3. Матрица контактов клавиш

Связь с системным блоком осуществляется через последовательную линию связи, данные по которой передаются «кадрами» по 11 бит, восемь из которых – информационные данные, а остальные – синхронизирующие и управляющие. Это последовательная линия связи. В системах AT контроллер, установленный в клавиатуре (типа 8049), пересылает данные в универсальный интерфейс UPI на системной плате. В компьютерах PC/XT связь была односторонней, но в компьютере AT она стала двунаправленной, т. е. клавиатура может, как передавать данные, так и принимать. Благодаря этому клавиатуру AT можно программировать.

Работу двунаправленного интерфейса иллюстрирует рис. 4а, где пунктиром помечены сигналы, формируемые контроллером, а сплошной линией – клавиатурой. В исходном состоянии обе линии «отпущены» выходными формирователями в состояние с высоким уровнем. Клавиатура может начать передачу данных в произвольный момент, когда интерфейс находится в покое. Клавиатура формирует стартовый бит (низкий уровень) на линии KB-Data и первый импульс KB-Clock, что является сигналом контроллеру о необходимости начала приема. После подъема KB-Clock она выводит 0-й бит данных на линию KB-Data, а затем и следующий импульс KB-Clock. Контроллер должен «защелкивать» принятый бит данных по спаду KB-Clock. Так передаются все 8 бит данных и бит паритета, дополняющий число единичных бит до нечетного. После синхроимпульса бита паритета контроллер клавиатуры должен сформировать импульс KB-Clock, подтверждающий прием байта (Ack). Если весь байт с битом паритета не будет получен контроллером за 2 мс, контроллер прекращает прием данного байта и фиксирует ошибку тайм-аута.

Рис. 4. Временные диаграммы интерфейса клавиатуры:

а) прием посылки от клавиатуры; б) передача команды в клавиатуру

Обратная передача – вывод команды контроллера в клавиатуру – происходит несколько сложнее (рис. 4б). Из состояния покоя контроллер устанавливает низкий уровень KB-Clock на 250 мкс и формирует старт-бит (низкий уровень) – это сигнал клавиатуре на прием команды. На него клавиатура должна ответить серией из 11 импульсов KB-Clock. По спаду очередного синхроимпульса контроллер выставляет очередной бит данных, а клавиатура его «защелкивает» по фронту формируемого ею же синхроимпульса. После бита паритета (9-й импульс) и единичного стоп-бита (10-й) на одиннадцатом импульсе клавиатура формирует нулевой бит подтверждения (Ack). После этого контроллер формирует импульс KB-Clock (60 мкс), который является запросом на прием ответа клавиатуры. Контроллер ожидает окончания ответа на этот запрос не более 20 мс и, если ответ не придет за это время, сформирует ошибку тайм-аута. Ошибка будет также в случае, если клавиатура не введет первый синхроимпульс за 15 мс от начала запроса или контроллер не примет данные, включая стоп-бит, за 2 мс с момента появления синхроимпульса бита 0.