- •Алгебра логика

- •Булева алгебра

- •Стандартные формы

- •Реализация логических функций

- •Диодно-транзисторный логический элемент (лэ-дтл)

- •5. Элементы интегральной инжекционной логики (и2л)

- •6. Преобразователи кодов (пк)

- •Дешифратор

- •Линейный дешифратор

- •Пирамидальный дешифратор

- •Матричный дешифратор

- •Мультиплексор

- •Демультиплексор

- •7. Комбинационные сумматоры (sm)

- •Вычитатель

- •Асинхронные rs-триггеры

- •Синхронные rs-триггеры

- •Модификации rs-триггеры

- •10. Регистры (rg)

- •Счетчики

- •Запоминающие устройства (память)

- •Оперативные зу

Асинхронные rs-триггеры

9.1.1. RS-триггеры на логических элементах ИЛИ-НЕ

Статические параметры:

Динамические параметры.

![]() -

разрешающее время, определяемое как

минимальный период следования входящих

сигналов, при котором триггер сохраняет

работоспособность.

определяет

-

разрешающее время, определяемое как

минимальный период следования входящих

сигналов, при котором триггер сохраняет

работоспособность.

определяет

![]() переключения триггера.

переключения триггера.

![]()

![]() - длительность задержки

распространения сигнала, измеряемая

на выходах триггера по отношению к

каждому из входов.

- длительность задержки

распространения сигнала, измеряемая

на выходах триггера по отношению к

каждому из входов.

![]() - минимальная

длительность входных сигналов, при

которых триггер реагирует на управляющее

воздействие.

- минимальная

длительность входных сигналов, при

которых триггер реагирует на управляющее

воздействие.

Активный уровень – 1.

Активный уровень – 1.

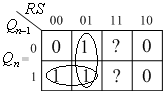

|

|

|

|

0 |

0 |

|

|

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

? |

? |

режим хранения;

установка «1»;

установка «0»;

разрыв триггерной связи.

![]()

9.1.2. RS-триггеры на логических элементах И-НЕ

Синхронные rs-триггеры

Такие триггеры содержат дополнительный тактирующий (синхронизирующий)вход С, определяющий моменты переключения триггера.

![]()

Модификации rs-триггеры

S-триггер

R-триггер

Е-триггер (триггер хранения)

RS-триггер типа «защелка»

На входе

![]() (Режим хранения)

(Режим хранения)

Лекция 10.

9.5. RS- триггер типа MS (Master Slave)

C=0: М – режим хранения; S – Qn;

С=1: М – режим установки;

S – режим хранения;

9.6. D – триггера

D – триггер называется триггером задержки.

9.7. D – триггер типа «защелка»

С=0: А=В=1 - режим хранения;

D=0: F=1; B=0; E=0; A=1 – установка в «0»;

D=1: F=0; B=1; E=1; A=0 – установка в «1»;

Для того чтобы использовать D – триггер в счетчиках, нужно соединить вход D с инверсным выходом.

9.8. D – триггер типа MS

9.9. JK – триггер типа «защелка»

9.10. JK – триггер типа МС

10. Регистры (rg)

Регистры – это последовательностные устройства, предназначенные для приема, хранения простых преобразований и передаче двоичных чисел.

Под простым преобразованием понимают сдвиг числа на данное количество разрядов, а также преобразование последовательного двоичного кода в параллельный и наоборот.

В зависимости от способа приема и передачи двоичной информации, различают параллельные, последовательностные и универсальные регистры.

В параллельных регистрах «ввод-вывод» всех разрядов числа производится одновременно за один такт.

Для построения n-разрядного регистра нужно n триггеров.

В последовательностных регистрах «ввод-вывод» информации осуществляется через один информационный вход и один выход, порозрядно со сдвигом числа. Поэтому последовательностный регистр называют сдвигающим. За один такт вводимая или выводимая информация сдвигается на один разряд вправо или влево. Сдвигающие регистры, реализующие по команде управления сдвиги информации, называют реверсивными.

Последовательно-параллельные регистры имеют один информационный вход для последовательного ввода числа в режиме сдвига и выходные схемы для подачи n-разрядного числа параллельным кодом, то есть для преобразования последовательного кода в параллельный.

В параллельно-последовательном регистре информация вводится параллельным кодом за один такт через тактируемые входные схемы, а выводится параллельно по одному разряду за один такт, то есть реализуется преобразование параллельного кода в последовательный.

Лекция 11.

10.1. Параллельные регистры

![]()

![]()

10.2. Сдвигающие регистры