- •1 Синтез простейших логических функций

- •2 Построение схем классического дешифратора и мультиплексора требуемой размерности

- •2.1 Дешифратор

- •2.2 Мультиплексор

- •3 Построение сумматора, компаратора и прочих комбинационных устройств

- •4 Построение временной диаграммы работы триггера при заданных параметрах

- •5 Построение схем регистров и счётчиков требуемых типов

- •5.1 Регистр

- •5.2 Счётчик

- •6 Реализация преобразователя с помощью условного пзу

- •7. Сумматор – (http://ru.Wikipedia.Org/wiki/Сумматор).

2.2 Мультиплексор

Мультиплексором называется комбинационное устройство, предназначенное для коммутации в желаемом порядке сигналов с нескольких входов на единственный выход. В этом смысле можно уподобить мультиплексор многопозиционному переключателю.

Входы мультиплексора по функциональному назначению делятся на информационные, адресные (или селектирующие) и разрешающие (или стробирующие). Подачей на селектирующие входы кодовой комбинации осуществляется выбор соответствующего этой комбинации информационного входа, подключаемого к выходу мультиплексора, а сигнал на стробирующем входе разрешает это подключение. У большинства мультиплексоров реализуется следующее правило выбора: к выходу подключается тот информационный вход, номер которого в двоичном коде подан на селектирующие входы.

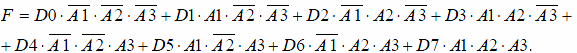

Сказанное можно считать словесным заданием функции мультиплексора. Для аналитического задания положим, например, что число селектирующих входов n=3 и обозначим их A1 – A3. Тогда число информационных входов равно 2n = 8. Обозначим их D0 – D7. С учетом этого аналитическое выражение для функции, реализуемой на выходе мультиплексора, можно записать следующим образом:

Н а

основании этого выражения

представлена схема

мультиплексора в соответствии

с рисунком 2.3.

а

основании этого выражения

представлена схема

мультиплексора в соответствии

с рисунком 2.3.

Наращивание разрядности мультиплексора просходит аналогично наращиванию разрядности дешифратора.

Задача №3.

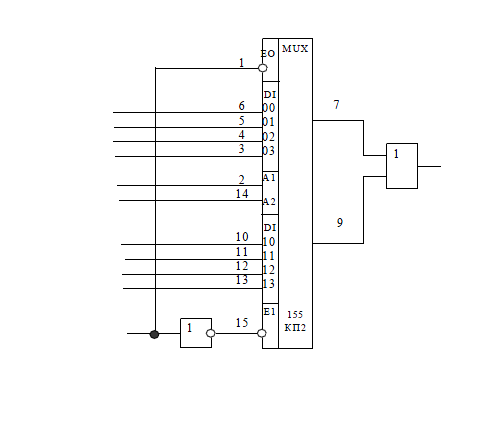

Используя два корпуса микросхем К155КП2 и необходимые логические элементы, синтезировать принципиальную схему мультиплексора размерностью 8х1 со стробированием.

Решение задачи представлено

в соответствии с рисунком 2.4. Здесь вход

стробирования Е, являющийся адресным

входом мультиплексора 8х1, включает

верхнюю микросхему, если на него подана

логическая единица, и включает нижнюю

секцию, если на него подан логический

ноль. Адресные входы А1–А2 выбирают один

из входов DI0–DI7

работающей микросхемы, сигнал с которого

будет направлен на выход 7 или 9. Для

того, чтобы на выходе мультиплексора

8х1 всегда присутствовал активный

уровень, применяется логический элемент

«ИЛИ».

Рис 4.2 мультиплексор со стробированием размерностью 8х1.

3 Построение сумматора, компаратора и прочих комбинационных устройств

Задача №4.

Используя один корпус ИС К155ИМ3 и необходимое количество любых логических элементов, построить схему суммирующего и вычитающего узла в дополнительном коде.

Сумматоры представляют собой функциональные цифровые устройства, выполняющие сложение чисел. Суммирование осуществляется в двоичном коде. Каждый из многоразрядных сумматоров может быть отнесен в зависимости от способов сложения к параллельному или последовательному типу. В последовательных сумматорах сложение выполняется поразрядно и последовательно во времени, а в сумматорах параллельного типа все разряды суммируются одновременно, как и в сумматоре, указанном в задаче.

И те, и другие сумматоры строятся на основе одноразрядных полных сумматоров. Сложение выполняется в каждом разряде отдельно, но с учетом результата сложения в предыдущем разряде, т.е. с учетом переноса. Таким образом, каждый одноразрядный полный сумматор должен иметь один вход переноса P0, два входа слагаемых A и B, выход суммы S и выход переноса P1.

В цифровой технике операция вычитания с использованием заёма практически не применяется. Одним из способов выполнения операции вычитания с помощью двоичного сумматора является замена знака вычитаемого на противоположный и прибавление его к уменьшаемому A-B=A+(-B) с применением специальных кодов для представления отрицательных чисел. Для представления чисел со знаком используются прямой, обратный и дополнительный коды. Во всех этих кодах предусматривается дополнительный разряд (старший, т.е. крайний слева) для представления знака числа, причем знак «+» кодируется символом 0, а знак «-» – символом 1.

По условию задачи, необходимо преобразовать дополнительный код в прямой. Прямой код как положительного, так и отрицательного числа отличается от кода этого числа без знака только наличием знакового разряда с соответствующим его значением. Дополнительный код отрицательных двоичных чисел формируется по следующему правилу: цифры всех разрядов прямого кода числа, кроме знакового разряда, инвертируются, а к младшему разряду подсуммируется 1. Обратное преобразование из дополнительного кода в прямой код производится по тому же правилу.

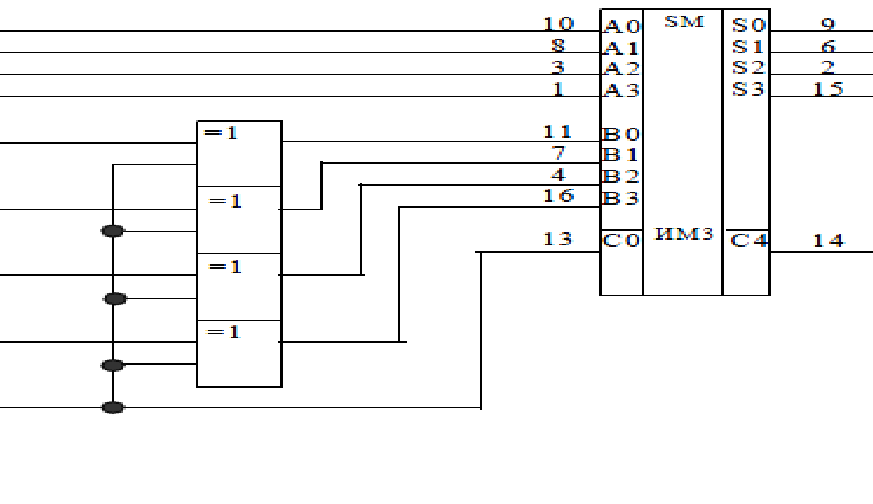

Рис 3 Суммирующий и вычитающий узел в дополнительном коде.

Принципиальная схема для преобразования дополнительного кода в прямой представлена в соответствии с рисунком 3.

На входы сумматора А0–А3 поступает отрицательное число, представленное в дополнительном коде. В данном случае входы B0–B3 для преобразования не нужны, поэтому они замкнуты на «землю», т.е. всегда имеют значение нуля. Разряды А0–А2 отрицательного числа инвертируются, а к младшему разряду прибавляется единица (на входе С0) в соответствии с правилом. Старший разряд не инвертируется, т.к. является разрядом, содержащим знак числа, т.е. единицу. В результате на выходах формируется отрицательное число в прямом коде.