- •Оглавление

- •Введение

- •Лабораторная работа №1 «Ознакомительная»

- •Краткое описание стенда цс-02

- •Меры безопасности

- •Общие рекомендации по выполнению работ

- •Содержание отчета

- •Контрольные вопросы

- •Лабораторная работа №2 «Определение статических и динамических параметров интегральных микросхем 155 серии»

- •Содержание отчета

- •Контрольные вопросы

- •Лабораторная работа №3. «Триггеры»

- •Контрольные вопросы

- •Лабораторная работа №4. «Четырехразрядный двоичный счетчик».

- •Задание 1: Синтезировать электрическую принципиальную схему двоичного четырёхразрядного счётчика, функциональная схема которого представлена на рис. 1.

- •Контрольные вопросы

- •Лабораторная работа №5. «Преобразователи кодов: шифраторы и дешифраторы».

- •Лабораторная работа №6. «Двоичные сумматоры»

- •Теоретические основы лабораторной работы

- •Двоичные сумматоры

- •Контрольные вопросы

- •Лабораторная работа №7. «Генератор прямоугольных импульсов»

- •Теоретические основы лабораторной работы

- •2. Контрольные вопросы

- •Лабораторная работа №8. «Арифметико-логическое устройство»

- •Теоретические основы лабораторной работы

- •Контрольные вопросы

- •Лабораторная работа №9. «Учебная модель эвм»

Лабораторная работа №6. «Двоичные сумматоры»

Цель работы: изучение функционирования и построения двоичных сумматоров и вычитателей.

Теоретические основы лабораторной работы

Важным элементом цифровых устройств, выполняющих арифметическую обработку информации, является сумматор.

Сумматоры выполняют арифметическое (в противоположность логическому) сложение и вычитание чисел.

На основе сумматоров выполняются также умножение и деление. Сумматоры имеют как самостоятельное значение и являются также ядром схем арифметико–логических устройств (АЛУ), реализующих ряд разнообразных операций и являющихся непременной частью всех процессоров.

Двоичные сумматоры

Суммирование многоразрядных двоичных чисел А=anan-1…a0 и B=bnbn-1…b0 производится путем их поразрядного сложения с переносом между разрядами.

Поэтому основным узлом многоразрядных сумматоров является комбинационный одноразрядный сумматор, который выполняет арифметическое сложение трех одноразрядных чисел (цифр): цифры данного разряда первого слагаемого (ai), цифры данного разряда второго слагаемого (bi) и цифры (1 или 0) переноса из соседнего младшего разряда (pi).

В результате сложения для каждого разряда получаются две цифры – сумма для этого разряда (Si) и перенос в следующий старший разряд (pi+1).

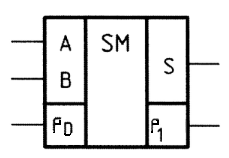

Условное графическое изображение полного двоичного одноразрядного сумматора и его таблица истинности (функционирования) приведены на рис. 1.

|

ai

bi

pi

Si

рi+1

0

0

0

0

0

1

0

0

1

0

0

1

0

1

0

1

1

0

0

1

0

0

1

1

0

1

0

1

0

1

0

1

1

0

1

1

1

1

1

1 |

|||||||||||||||||||||||||||||||||||||||||||||

Рис. 1 – Двоичный сумматор |

Таблица 1 - истинности сумматора |

Многоразрядный последовательный сумматор может быть составлен из одноразрядных сумматоров, число которых равно числу разрядов слагаемых, путем соединения выхода, на котором формируется сигнал переноса данного разряда, с входом для сигнала переноса соседнего старшего разряда. Такой способ организации переноса называется последовательным.

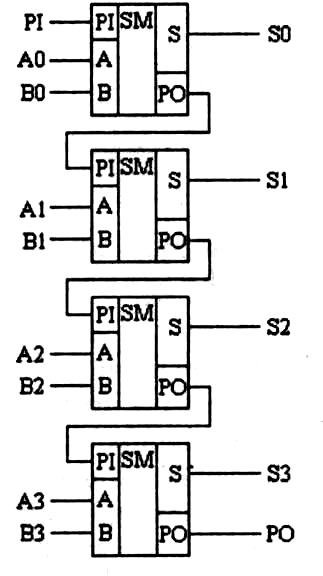

Схема реализации четырехразрядного сумматора на основе четырех одноразрядных приведена на рисунке 2).

|

|

|

Рис. 2 |

Рис. 3 |

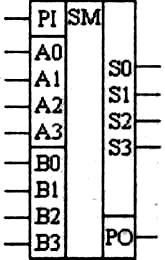

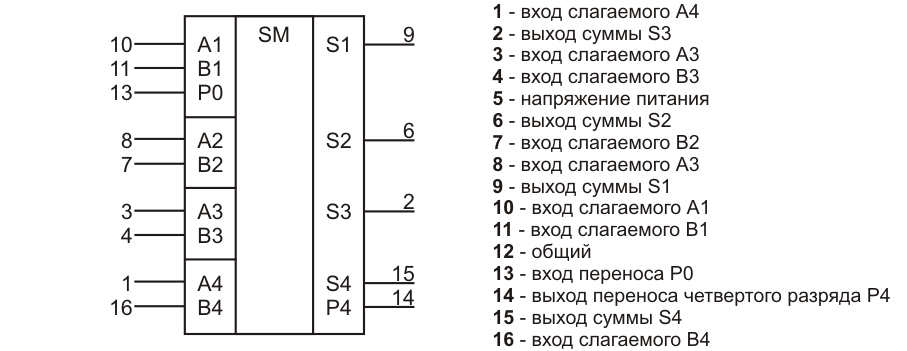

Рис 4 – УГО микросхемы К155ИМ3 |

Полный двоичный четырехразрядный сумматор изображается на схемах с использованием условного графического обозначения, показанного на рисунке 3.

Данный тип сумматора наиболее прост с точки зрения схемы цепей распространения переноса, но имеет сравнительно низкое быстродействие.

Более высоким быстродействием обладают сумматоры с параллельным переносом, в которых сигналы переноса формируются во всех разрядах одновременно. Этой цели служат специальные схемы ускоренного переноса.

Микросхема К155ИМ3 - быстродействующий четырёхразрядный сумматор .Он принимает два четырёхразрядных числа по входам данных А0-А3 и B0-B3, а по входу Р0 - сигнал переноса. Внутри этого сумматора имеется схема ускоренного переноса (СУП).

Задание 1: На базе интегральной ИС К155ИМ3 (рис.4) спроектировать и собрать схему четырёхразрядного двоичного сумматора. Составить и заполнить таблицу истинности его работы. Опишите работу схемы сумматора.

Задание 2: На базе четырёхразрядного двоичного сумматора (микросхема К155ИМ3) выполнить четырехразрядный двоичный вычитатель.

Примечание: использовать инверторы микросхемы К155ЛН1 (рис.5). Необходимо помнить, что с выхода вычитателя снимается 4-разрядный дополнительный код результата S4S3S2S1 и при вычитании чисел разность может быть как положительным числом (в этом случае Р4=1) так и отрицательным (в этом случае Р4=0), пояснить это на примерах.

Рис.5 - Условное графическое обозначение ИС К155ЛН1

Задание 3. На базе четырёхразрядного двоичного сумматора (микросхема К155ИМ3) выполнить четырехразрядный двоичный сумматор-вычитатель двоичных чисел с использованием двухвходовых логических элементов исключающее ИЛИ микросхемы К155ЛП5 (рис.6). Составить и заполнить таблицу истинности его работы. Опишите работу схемы сумматора- вычитателя.

|

14 - напряжение питания; 1,2,4,5,9,10,12,13 - входы; 3,6,8,11 - выходы; 7 - общий; |

Рис.6 – УГО ИС К155ЛП5 |

|