- •1.Последовательные цифровые устройства

- •15.1. Триггеры

- •15.1.1. Общие положения

- •15.1.2. Асинхронный rs-триггер

- •15.1.4. Универсальный jk-триггер

- •15.1.5. Взаимозаменяемость триггеров

- •15.2. Регистры

- •15.2.1. Регистры памяти

- •15.2.2. Регистры сдвига

- •15.2.3. Универсальные регистры

- •15.3. Счетчики

- •15.3.1. Основные определения и виды счетчиков

- •15.3.2. Асинхронные счетчики

- •15.3.3. Синхронные счетчики

- •15.3.4. Кольцевые счетчики

- •15.3.5. Программируемые счетчики

- •Контрольные вопросы

15. Последовательные цифровые устройства

1.Последовательные цифровые устройства

Последовательные схемы обладают внутренней памятью. В них выходные сигналы зависят не только от текущих, но и от предыдущих уровней входных сигналов. Такой подход называется последовательной логикой. По функциональному признаку последовательные цифровые устройства подразделяются на триггеры, регистры и счётчики.

15.1. Триггеры

Триггером называется устройство, которое может длительно находиться в одном из двух устойчивых состояниях. Переход триггера из одного состояния в другое происходит под воздействием входных сигналов. Триггер является базовым элементом регистров и счётчиков.

15.1.1. Общие положения

Триггеры по способу записи информации делятся на асинхронные и синхронные, или тактируемые. У асинхронного триггера изменения его состояния происходит непосредственно с приходом управляющего сигнала. В синхронных триггерах, кроме информационных, имеются входы синхронизации.

Синхронные триггеры разделяются на статические и динамические. Статические триггеры записывают информацию с информационного входа на выход при подаче на вход синхронизации определённого логического уровня напряжения (потенциала).

Динамические триггеры записывают информационные сигналы на выход при подаче на вход синхронизации фронта (прямой вход) или среза (инверсный вход) сигнала. Динамическое управление записью информации необходимо для предотвращения ложных срабатываний устройств. Синхроимпульс должен иметь высокую крутизну фронта или среза, что обеспечивает помехоустойчивость записи. Для прямого динамического входа С используются обозначение, приведённые на рис. 15.1, а, б, а для инверсного – на рис. 15.1, в, г.

Рис. 15.1. Обозначения динамического входа: прямого (а, б) и инверсного (в, г)

По функциональному признаку триггеры делят:

на асинхронные RS-триггеры;

синхронные D-триггеры;

счетные Т-триггеры;

универсальные JK-триггеры.

15.1.2. Асинхронный rs-триггер

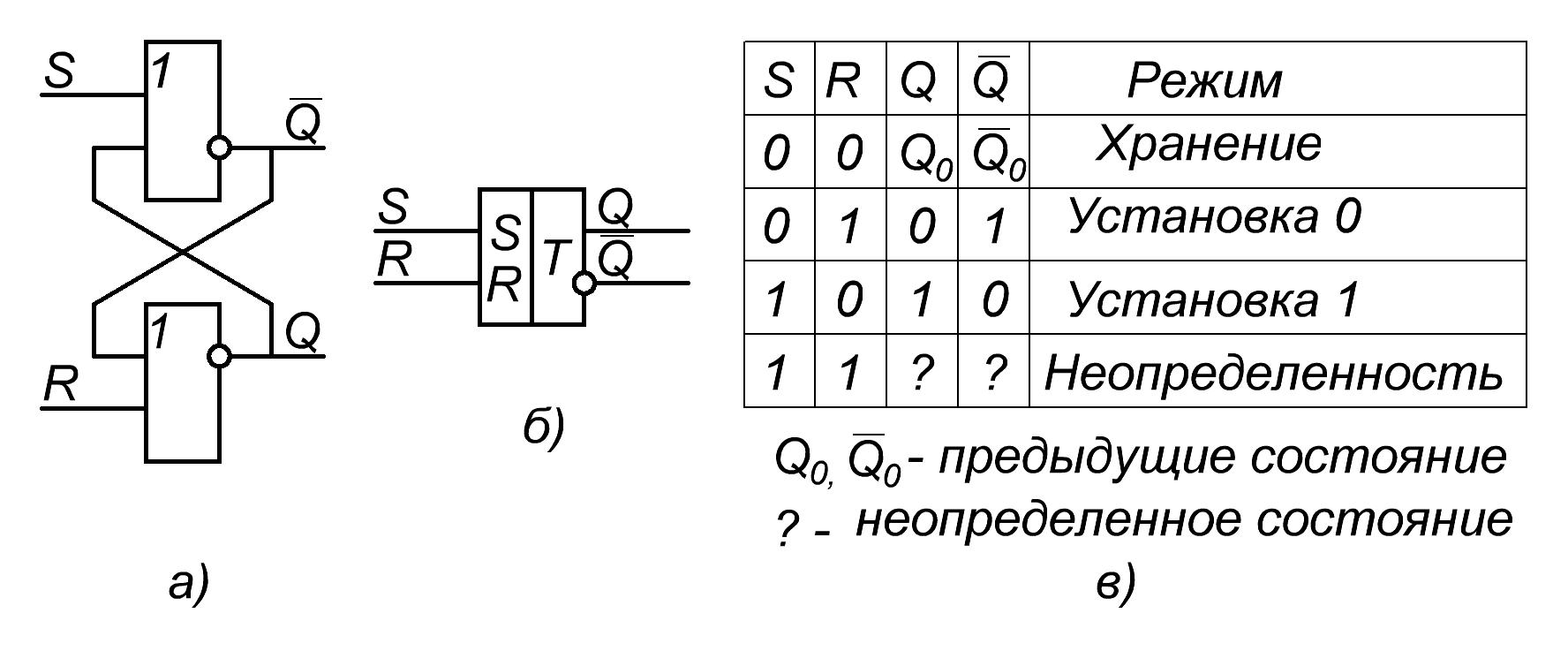

Этот тип триггеров реализуется

на основе двух ЛЭ с перекрестными

обратными связями. RS-триггер,

показанный на рис. 15.2,

а

состоит из двух элементов ИЛИ-НЕ. Входы

триггера (рис. 15.2, а,

б)

обозначаются S

(установка) и R

(сброс). Триггер может иметь два выхода

прямой Q,

и инверсный

![]() .

Асинхронный триггер изменяет своё

состояние непосредственно в момент

появления соответствующего информационного

сигнала R

или S.

.

Асинхронный триггер изменяет своё

состояние непосредственно в момент

появления соответствующего информационного

сигнала R

или S.

Рис. 15.2. RS-триггер: схема (а), обозначение (б), таблица истинности (в)

Работа триггера описывается таблицей истинности, показанной на рис. 15.2, в. Комбинацию входных сигналов S = R = 1 называют запрещённой, так как состояние выхода триггера неопределенно, т.е. на выходе Q может появиться 0 или 1, что заранее предсказать невозможно, поэтому таких ситуаций следует избегать.

Примером реализации данного типа триггера в интегральном исполнении является ИС 564ТР2 , которая содержит четыре асинхронных RS-триггера с одним прямым выходом и общим управляющим входом Н. Этот триггер ввиду отсутствия инверсного выхода не имеет запрещённой комбинации входных сигналов. При R = S = Н = 1 выходной сигнал Q = 1. При подаче на вход Н сигнала низкого уровня выходы всех триггеров переходит в состояние Z.

На рис. 15.3, а,

б

показан

![]() -триггер

на двух элементах И-НЕ, переключение

состояний которого осуществляется

сигналами низкого уровня. Из таблицы

истинности (рис. 15.3, в)

видно, что комбинация

-триггер

на двух элементах И-НЕ, переключение

состояний которого осуществляется

сигналами низкого уровня. Из таблицы

истинности (рис. 15.3, в)

видно, что комбинация

![]() =

=

![]() = 0 является запрещённой.

= 0 является запрещённой.

Рис.

15.3.

![]() –триггер:

схема

(а),

обозначение (б),

таблица истинности (в)

–триггер:

схема

(а),

обозначение (б),

таблица истинности (в)

15.1.3. D- и Т- триггер

Условное обозначение

D-триггера

приведено на рис. 15.4, а.

D-триггер

имеет два входа: информационный D,

синхронизации С

и может иметь два выхода: прямой Q,

и инверсный

![]() .

В этом триггере сигнал поступивший на

вход D,

по сигналу синхронизации на входе С

записывается и передаётся на выход. Так

как информация на выходе остаётся

неизменной до прихода очередного

импульса синхронизации, D-триггер

называют также триггером с запоминанием

информации или триггером-защелкой.

.

В этом триггере сигнал поступивший на

вход D,

по сигналу синхронизации на входе С

записывается и передаётся на выход. Так

как информация на выходе остаётся

неизменной до прихода очередного

импульса синхронизации, D-триггер

называют также триггером с запоминанием

информации или триггером-защелкой.

Рис. 15.4. Триггеры: D–типа (а), Т-типа (б), УГО ИС КР1554ТМ2 (в), её таблица истинности (г)

На рис. 15.4, в, г показаны УГО ИС КР1554ТМ2, которая представляет собой два независимых D-триггера, и её таблица истинности. Триггер работает в асинхронном и синхронном режимах. Асинхронный режим реализуется при подаче сигналов только на входы S и R, причём наличие активного (низкого) уровня на одном из входов S, R приводит к установке триггера в соответствующее состояние независимо от логических уровней на входах D и С. При S = R = 0 состояние триггера является неопределённым, поэтому одновременное присутствие на входах S, R логических 0 следует считать запрещённой входной комбинацией.

В синхронном режиме S = R = 1 информация с входа D переписывается на выходы триггера по положительному фронту тактового импульса на входе С. Входы S, R обладают более высоким приоритетом, чем входы D, С.

Условное обозначение Т-триггера показано на рис. 15.4, б. Т-триггер или счётный триггер переключается в противоположное состояние при подаче сигнала активного уровня на его Т-вход, в противном случае триггер находится в режиме хранения. В зависимости от того фронт или срез используется для управления считается, что Т-триггер имеет прямой или инверсный динамический вход. Т-триггер делит частоту входного сигнала на 2. В интегральном исполнении Т-триггеры не производятся. Они легко создаются на базе других типов триггеров.