- •Кафедра – Информационно- Коммуникационные Технологии

- •Лекция 1. Введение в дисциплину – эвм и периферийные устройства

- •1.1 История развития вычислительной техники

- •1.2 Основные принципы построения эвм

- •Поколения эвм

- •Классификация эвм

- •Вопросы

- •Лекция 2. Компьютер – общие сведения

- •2.1 Основные узлы пк – «Материнская плата»

- •2.2 Основные компоненты компьютера:

- •2.3 Интерфейсные шины

- •2.4 Основные периферийные устройства компьютера

- •Вопросы и задания

- •Лекция 3. Представление данных в эвм.

- •3.1 Форматы файлов

- •3.2 Кодирование чисел

- •3.3 Кодирование текста

- •3.4 Кодирование графической информации

- •3.5 Кодирование звука

- •3.6 Типы данных

- •Лекция 4. Структурная организация эвм - процессор Введение

- •Что известно всем

- •4.1 Микропроцессорная система

- •4.2 Что такое микропроцессор?

- •4.3 Основной алгоритм работы процессора

- •Алу Запросы на пре-ия и пдп

- •4.4 Программный код и система команд

- •4.5 Микроархитектура процессора

- •512 Кбайт

- •Лекция 5. Микропрограммное устройство управления

- •5.1 Устройство управления

- •5.2 Микропроцессорная память

- •5.3 Структура адресной памяти процессора

- •5.4 Интерфейсная часть мп

- •5.5 Назначение и функции чипсета в микропроцессорной системе

- •Лекция 6. Организация памяти

- •6.1 Организация подсистемы памяти в пк

- •6.2 Оперативная память

- •6.4 Технологии оперативной памяти

- •Вопросы для самоконтроля

- •Лекция 7. Внешняя память компьютера Введение

- •Жесткий диск (Hard Disk Drive)

- •Общее устройство нжмд

- •Пластины (диски)

- •Головка записи-чтения

- •Позиционер

- •Контроллер

- •Производительность

- •Структура хранения информации на жестком диске

- •Кластер

- •Магнитооптические диски

- •Лазерные компакт-диски cd - rom

- •Дисковые массивы и уровни raid

- •Raid 0: Базовая конфигурация.

- •Raid1: Зеркальные диски.

- •Raid 2: матрица с поразрядным расслоением

- •Raid 3: аппаратное обнаружение ошибок и четность

- •Raid 4: внутригрупповой параллелизм

- •Raid 5: четность вращения для распараллеливания записей

- •Raid 6: Двумерная четность для обеспечения большей надежности

- •Флэш-память

- •Вопросы и задания

- •Лекция 8. Логическая организация памяти

- •Виртуальная память

- •Основная память

- •Дисковая память

- •Страничная организация памяти

- •Преобразование адресов

- •Сегментная организация памяти.

- •Свопинг

- •Вопросы и задания

- •Лекция 9. Методы адресации

- •Лекция 10. Архитектура risc-процессоров

- •10.1 Основные черты risc-процессоров

- •10.2 Risc-процессоры 3-го поколения

- •Структура процессоров Alpha: 21064, 21264

- •10.3Пиковая производительность risc-процессоров

- •10.4 Области применения risc-процессоров

- •Вопросы для самоконтроля

- •Лекция 11. Высокопроизводительные вс

- •11.1 Параллельная обработка данных на эвм

- •Закон Амдала

- •11.2 История появления параллелизма в архитектуре эвм

- •11.3 Классы параллельных систем

- •11.4 Технологии параллельного программирования

- •11.5 Оценки производительности супер-эвм

- •Вопросы для самоконтроля

- •Лекция 12. Особенности архитектуры современных высокопроизводительных вс Введение

- •Параллельные системы

- •Классификация архитектур по параллельной обработке данных

- •Вычислительные Системы

- •Параллелизм на уровне команд – однопроцессорные архитектуры

- •Конвейерная обработка

- •Суперскалярные архитектуры

- •Мультипроцессорные системы на кристалле

- •Технология Hyper-Threading

- •Многоядерность — следующий этап развития

- •Вопросы и задания

- •Лекция 13. Организация обмена в вычислительной системе

- •13.1 Система прерываний и исключений в архитектуре ia-32

- •13.2 Расширенный программируемый контроллер прерываний (apic)

- •13. 3 Обработка прерываний на основе контроллера 8259a

- •13.4 Подсистема прямого доступа к памяти

- •Вопросы для самоконтроля

- •Лекция 14. Интерфейсы вычислительных систем

- •14.1 Типы и характеристики интерфейсов

- •14.2 Архитектура системных интерфейсов

- •14.3 Системные интерфейсы для пк

- •14.5 Интерфейс pci

- •14.6 Порт agp

- •14.8 Интерфейсы накопителей

- •Вопросы для самоконтроля

- •Лекция 15. Интерфейсы периферийных устройств

- •15.1 Интерфейсы scsi

- •15.2 Интерфейс rs-232c

- •15.3 Интерфейс ieee 1284

- •15.4 Инфракрасный интерфейс

- •15.5 Интерфейс usb

- •15.6 Интерфейс ieee 1394 - FireWire

- •Вопросы для самоконтроля

- •Лекция 16. Состав, классификация и характеристики периферийных устройств

- •16.1 Классификация периферийных устройств

- •16.2 Видеосистема

- •16.3 Видеоадаптеры

- •16.5 Аудиосистема

- •Контрольные вопросы

- •Список основной литературы

- •Список дополнительной литературы

- •Приложение Классификация и основные определения пу.

- •Общая характеристика клавиатуры.

- •Интерфейс клавиатуры и мыши.

- •Скан-коды и системная поддержка.

- •Манипуляторы-указатели

- •Общая характеристика методов вывода изображений.

- •Графический режим.

- •Текстовый режим.

- •Трехмерная графика и способы обработки видеоизображений.

- •Принципы передачи цветных телевизионных изображений.

- •Объединение компьютерной графики и телевизионного изображения.

- •Стандарты кодеков изображений mpeg.

- •Основные технические характеристики.

- •Управление монитором.

- •Плоские дисплеи.

- •Интерфейсы дисплеев.

- •Функциональная схема адаптеров дисплеев

- •Графический процессор адаптера, принцип работы тракта записи.

- •Принцип считывания со сравниванием цветов в графическом адаптере.

- •Параметры видеосистемы.

- •Принципы построения различных типов принтеров.

- •Форматы данных и интерфейсы принтеров

- •Системная поддержка принтеров.

- •Принципы хранения информации.

- •Хранение информации на магнитных дисках.

- •Накопители на гибких магнитных дисках (нгмд).

- •Интерфейс и контроллер нгмд.

- •Конструкция накопителя на жестких магнитных дисках (нжмд).

- •Основные характеристики винчестеров.

- •Особенности функционирования винчестеров

- •Магнитооптические диски.

- •Флэш-память.

- •Основы цифровой обработки сигналов.

- •Звуковая карта пк.

- •Интерфейсы звуковых карт.

- •Проводные интерфейсы связи.

- •40. Беспроводные интерфейсы связи. Инфракрасный интерфейс.

- •Беспроводные интерфейсы связи. Радиоинтерфейс Bluetooth.

- •Модемы. Структурная схема устройства.

- •Основные принципы шинной связи, управление шиной.

- •Арбитраж шин.

- •Передача информации шинами по блочно.

- •Шины расширения.

- •Параллельные шины.

- •Последовательные шины

Структура процессоров Alpha: 21064, 21264

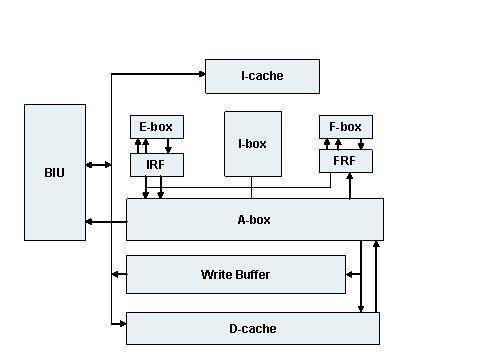

Структура процессора Alpha 21064 представлена на рис. 10.1.

Рис. 10.1. Структура процессора Alpha 21064

Основные функциональные блоки процессора Alpha 21064:

I-cache - кэш команд.

IRF - регистровый файл целочисленной арифметики.

F-box - устройство арифметики с плавающей точкой.

E-box - устройство целочисленной арифметики (7 ступеней конвейера).

I-box - командное устройство (управляет кэш команд, выборкой и дешифрацией команд).

A-box - устройство управления загрузкой/сохранением данных. Управляет процессом обмена данными м/у IRF, FRF, кэш данных и внешней памятью.

Write Buffer - буфер обратной записи.

D-cache - КЭШ данных.

BIU - интерфейсный блок, с помощью которого подключаются внешняя кэш память, размером 128 Кб-8 Мб.

Процессоры PA-RISC компании Hewlett-Packard

Процессор PA-8000 вобрал в себя все известные методы ускорения выполнения команд. В его основе лежит концепция "интеллектуального выполнения", которая базируется на принципе внеочередного выполнения команд. Это свойство позволяет PA-8000 достигать пиковой производительности благодаря широкому использованию механизмов автоматического разрешения конфликтов по данным и управлению аппаратными средствами. Эти средства хорошо дополняют другие архитектурные компоненты, заложенные в структуру кристалла: большое число исполнительных функциональных устройств, средства прогнозирования направления переходов и выполнения команд по предположению, оптимизированная организация кэш-памяти и высокопроизводительный шинный интерфейс. Высокая производительность PA-8000 во многом определяется наличием большого набора функциональных устройств. В состав PA-8000 входят 10 исполнительных устройств: два арифметико-логических устройства (АЛУ) для выполнения целочисленных операций, два устройства для выполнения операций сдвига/слияния данных, два устройства для выполнения умножения/сложения чисел с плавающей точкой, два устройства деления/вычисления квадратного корня и два устройства выполнения операций загрузки/записи. Средства внеочередного выполнения команд процессора PA-8000 обеспечивают аппаратное планирование загрузки конвейеров и лучшее использование функциональных устройств. В каждом такте на выполнение могут выдаваться до четырех команд, которые поступают в 56-строчный буфер переупорядочивания. Этот буфер позволяет поддерживать постоянную занятость функциональных устройств и обеспечивает эффективную минимизацию конфликтов по ресурсам. Кристалл может анализировать все 56 командных строк одновременно и выдавать в каждом такте по 4 готовых для выполнения команды в функциональные устройства. Это позволяет процессору автоматически выявлять параллелизм уровня выполнения команд. Суперскалярный процессор PA-8000 обеспечивает полный набор средств выполнения 64-битовых операций, включая адресную арифметику, а также арифметику с фиксированной и плавающей точкой. При этом кристалл полностью сохраняет совместимость с 32-битовыми приложениями и с предыдущими и будущими реализациями PA-RISC. Это первый процессор, в котором реализована 64-битовая архитектура PA-RISC.