- •Кафедра – Информационно- Коммуникационные Технологии

- •Лекция 1. Введение в дисциплину – эвм и периферийные устройства

- •1.1 История развития вычислительной техники

- •1.2 Основные принципы построения эвм

- •Поколения эвм

- •Классификация эвм

- •Вопросы

- •Лекция 2. Компьютер – общие сведения

- •2.1 Основные узлы пк – «Материнская плата»

- •2.2 Основные компоненты компьютера:

- •2.3 Интерфейсные шины

- •2.4 Основные периферийные устройства компьютера

- •Вопросы и задания

- •Лекция 3. Представление данных в эвм.

- •3.1 Форматы файлов

- •3.2 Кодирование чисел

- •3.3 Кодирование текста

- •3.4 Кодирование графической информации

- •3.5 Кодирование звука

- •3.6 Типы данных

- •Лекция 4. Структурная организация эвм - процессор Введение

- •Что известно всем

- •4.1 Микропроцессорная система

- •4.2 Что такое микропроцессор?

- •4.3 Основной алгоритм работы процессора

- •Алу Запросы на пре-ия и пдп

- •4.4 Программный код и система команд

- •4.5 Микроархитектура процессора

- •512 Кбайт

- •Лекция 5. Микропрограммное устройство управления

- •5.1 Устройство управления

- •5.2 Микропроцессорная память

- •5.3 Структура адресной памяти процессора

- •5.4 Интерфейсная часть мп

- •5.5 Назначение и функции чипсета в микропроцессорной системе

- •Лекция 6. Организация памяти

- •6.1 Организация подсистемы памяти в пк

- •6.2 Оперативная память

- •6.4 Технологии оперативной памяти

- •Вопросы для самоконтроля

- •Лекция 7. Внешняя память компьютера Введение

- •Жесткий диск (Hard Disk Drive)

- •Общее устройство нжмд

- •Пластины (диски)

- •Головка записи-чтения

- •Позиционер

- •Контроллер

- •Производительность

- •Структура хранения информации на жестком диске

- •Кластер

- •Магнитооптические диски

- •Лазерные компакт-диски cd - rom

- •Дисковые массивы и уровни raid

- •Raid 0: Базовая конфигурация.

- •Raid1: Зеркальные диски.

- •Raid 2: матрица с поразрядным расслоением

- •Raid 3: аппаратное обнаружение ошибок и четность

- •Raid 4: внутригрупповой параллелизм

- •Raid 5: четность вращения для распараллеливания записей

- •Raid 6: Двумерная четность для обеспечения большей надежности

- •Флэш-память

- •Вопросы и задания

- •Лекция 8. Логическая организация памяти

- •Виртуальная память

- •Основная память

- •Дисковая память

- •Страничная организация памяти

- •Преобразование адресов

- •Сегментная организация памяти.

- •Свопинг

- •Вопросы и задания

- •Лекция 9. Методы адресации

- •Лекция 10. Архитектура risc-процессоров

- •10.1 Основные черты risc-процессоров

- •10.2 Risc-процессоры 3-го поколения

- •Структура процессоров Alpha: 21064, 21264

- •10.3Пиковая производительность risc-процессоров

- •10.4 Области применения risc-процессоров

- •Вопросы для самоконтроля

- •Лекция 11. Высокопроизводительные вс

- •11.1 Параллельная обработка данных на эвм

- •Закон Амдала

- •11.2 История появления параллелизма в архитектуре эвм

- •11.3 Классы параллельных систем

- •11.4 Технологии параллельного программирования

- •11.5 Оценки производительности супер-эвм

- •Вопросы для самоконтроля

- •Лекция 12. Особенности архитектуры современных высокопроизводительных вс Введение

- •Параллельные системы

- •Классификация архитектур по параллельной обработке данных

- •Вычислительные Системы

- •Параллелизм на уровне команд – однопроцессорные архитектуры

- •Конвейерная обработка

- •Суперскалярные архитектуры

- •Мультипроцессорные системы на кристалле

- •Технология Hyper-Threading

- •Многоядерность — следующий этап развития

- •Вопросы и задания

- •Лекция 13. Организация обмена в вычислительной системе

- •13.1 Система прерываний и исключений в архитектуре ia-32

- •13.2 Расширенный программируемый контроллер прерываний (apic)

- •13. 3 Обработка прерываний на основе контроллера 8259a

- •13.4 Подсистема прямого доступа к памяти

- •Вопросы для самоконтроля

- •Лекция 14. Интерфейсы вычислительных систем

- •14.1 Типы и характеристики интерфейсов

- •14.2 Архитектура системных интерфейсов

- •14.3 Системные интерфейсы для пк

- •14.5 Интерфейс pci

- •14.6 Порт agp

- •14.8 Интерфейсы накопителей

- •Вопросы для самоконтроля

- •Лекция 15. Интерфейсы периферийных устройств

- •15.1 Интерфейсы scsi

- •15.2 Интерфейс rs-232c

- •15.3 Интерфейс ieee 1284

- •15.4 Инфракрасный интерфейс

- •15.5 Интерфейс usb

- •15.6 Интерфейс ieee 1394 - FireWire

- •Вопросы для самоконтроля

- •Лекция 16. Состав, классификация и характеристики периферийных устройств

- •16.1 Классификация периферийных устройств

- •16.2 Видеосистема

- •16.3 Видеоадаптеры

- •16.5 Аудиосистема

- •Контрольные вопросы

- •Список основной литературы

- •Список дополнительной литературы

- •Приложение Классификация и основные определения пу.

- •Общая характеристика клавиатуры.

- •Интерфейс клавиатуры и мыши.

- •Скан-коды и системная поддержка.

- •Манипуляторы-указатели

- •Общая характеристика методов вывода изображений.

- •Графический режим.

- •Текстовый режим.

- •Трехмерная графика и способы обработки видеоизображений.

- •Принципы передачи цветных телевизионных изображений.

- •Объединение компьютерной графики и телевизионного изображения.

- •Стандарты кодеков изображений mpeg.

- •Основные технические характеристики.

- •Управление монитором.

- •Плоские дисплеи.

- •Интерфейсы дисплеев.

- •Функциональная схема адаптеров дисплеев

- •Графический процессор адаптера, принцип работы тракта записи.

- •Принцип считывания со сравниванием цветов в графическом адаптере.

- •Параметры видеосистемы.

- •Принципы построения различных типов принтеров.

- •Форматы данных и интерфейсы принтеров

- •Системная поддержка принтеров.

- •Принципы хранения информации.

- •Хранение информации на магнитных дисках.

- •Накопители на гибких магнитных дисках (нгмд).

- •Интерфейс и контроллер нгмд.

- •Конструкция накопителя на жестких магнитных дисках (нжмд).

- •Основные характеристики винчестеров.

- •Особенности функционирования винчестеров

- •Магнитооптические диски.

- •Флэш-память.

- •Основы цифровой обработки сигналов.

- •Звуковая карта пк.

- •Интерфейсы звуковых карт.

- •Проводные интерфейсы связи.

- •40. Беспроводные интерфейсы связи. Инфракрасный интерфейс.

- •Беспроводные интерфейсы связи. Радиоинтерфейс Bluetooth.

- •Модемы. Структурная схема устройства.

- •Основные принципы шинной связи, управление шиной.

- •Арбитраж шин.

- •Передача информации шинами по блочно.

- •Шины расширения.

- •Параллельные шины.

- •Последовательные шины

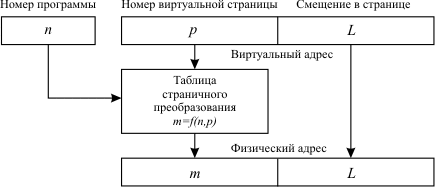

Преобразование адресов

В наиболее простом и наиболее часто используемом случае страничной виртуальной памяти каждая виртуальная память (виртуальная память каждого процесса) и физическая основная память представляются состоящими из наборов блоков или страниц одинакового размера. Для удобства реализации размер страницы всегда выбирается равным числу, являющемуся степенью 2. Тогда, если общая длина виртуального адреса есть N (в последние годы это тоже всегда некоторая степень 2 - 16, 32, 64), а размер страницы есть 2M), то виртуальный адрес рассматривается как структура, состоящая из двух полей: первое поле занимает (N-M+1) разрядов адреса и задает номер страницы виртуальной памяти, второе поле занимает (M-1) разрядов и задает смещение внутри страницы до адресуемого элемента памяти (в большинстве случаев - байта). Аппаратная интерпретация виртуального адреса показана на рисунке 8.4. Рисунок иллюстрирует механизм на концептуальном уровне, не вдаваясь в детали по поводу того, что из себя представляет и где хранится таблица страниц. Мы не будем рассматривать возможные варианты, а лишь заметим, что в большинстве современных компьютеров со страничной организацией виртуальной памяти все таблицы страниц хранятся в основной памяти, а быстрота доступа к элементам таблицы текущей виртуальной памяти достигается за счет наличия сверхбыстродействующей буферной памяти (КЭШа).

Рис. 8.4 Преобразование виртуального адреса в физический адрес

Приведем пример реального страничного распределения памяти. При загрузке процесса часть его виртуальных страниц помещается в оперативную память, а остальные - на диск. Смежные виртуальные страницы не обязательно располагаются в смежных физических страницах. При загрузке операционная система создает для каждого процесса информационную структуру - таблицу страниц, в которой устанавливается соответствие между номерами виртуальных и физических страниц для страниц, загруженных в оперативную память, или делается отметка о том, что виртуальная страница выгружена на диск. Кроме того, в таблице страниц содержится управляющая информация, такая как признак модификации страницы, признак невыгружаемости (выгрузка некоторых страниц может быть запрещена), признак обращения к странице (используется для подсчета числа обращений за определенный период времени) и другие данные, формируемые и используемые механизмом виртуальной памяти.

Сгенерированный процессором

виртуальный адрес (линейный адрес)

31 21 11

Directory

Table Offset

Каталог таблиц

страниц (адреса

таблиц страниц)

Таблица страниц Физическая память

4 К

4К

4

К

…. …..

4К

Начальный

Начальный

адрес

А дрес искомого

э

лемента

таблицы

лемента

таблицы

Управляющие биты

Рис. 8.5 Страничная трансляция адресов

При активизации очередного процесса в специальный регистр процессора загружается адрес таблицы страниц данного процесса. При каждом обращении к памяти происходит чтение из таблицы страниц информации о виртуальной странице, к которой произошло обращение. Если данная виртуальная страница находится в оперативной памяти, то выполняется преобразование виртуального адреса в физический. Если же нужная виртуальная страница в данный момент выгружена на диск, то происходит так называемое страничное прерывание. Выполняющийся процесс переводится в состояние ожидания, и активизируется другой процесс из очереди готовых процессов. Параллельно программа обработки страничного прерывания находит на диске требуемую виртуальную страницу и пытается загрузить ее в оперативную память. Если в памяти имеется свободная физическая страница, то загрузка выполняется немедленно, если же свободных страниц нет, то решается вопрос, какую страницу следует выгрузить из оперативной памяти.