- •Схемотехника

- •Часть 1: схемотехника цифровых устройств

- •Общие организационно-методические указания

- •2. Задание на курсовое проектирование

- •2.1. Задание для курсантов (студентов) очной формы обучения.

- •2.2. Задание для курсантов (студентов) заочной формы обучения.

- •Методические указания и рекомендации по выполнению курсового проектирования

- •Методика настройки модели цифрового вольтметра

- •4.1 Приемы модификации элементов схем и управления процессом моделирования.

- •Анализ исходной схемы (прототипа) цифрового вольтметра.

- •4.2.1. Подготовительные действия:

- •4.2.2. Проверка работоспособности прототипа цифрового вольтметра:

- •4.3. Изменение параметров усилителей входных сигналов, поступающих на компаратор da3:

- •4.5. Регулировка начального значения ступенчатого напряжения цап, определяющего нижний предел измерения цифрового вольтметра:

- •4.6. Регулировка верхнего предела измерений цифрового вольтметра:

- •4.7. Завершающая проверка настройки цифрового вольтметра:

- •Требования к оформлению пояснительной части проекта

- •6. Требования и рекомендации к моделированию

- •Рекомендуемая литература и электронные ресурсы

- •Часть1. «Схемотехника цифровых устройств»

- •Пояснительная записка

- •1. Описание цифрового вольтметра.

- •1.1. Параметры и характеристики цифрового вольтметра:

- •1.2. Состав цифрового вольтметра:

- •1.3. Принцип работы цифрового вольтметра

- •2. Структура программы, моделирующей цифровой вольтметр

- •Индикаторы.

- •Преобразователь двоичного кода в двоично-десятичный (пБл1, Сх1-15).

- •Коммутатор (Сх8).

- •Схемотехника цифрового вольтметра

- •4.1. Индикаторная часть цифрового вольтметра.

- •4.2. Измерительная часть прототипа цифрового вольтметра.

- •Общие организационно-методические указания ……………………………………………………2

- •Дмитрий Петрович Степаненко схемотехника

- •Часть 1: схемотехника цифровых устройств

Коммутатор (Сх8).

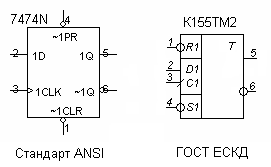

Задан триггер SN7474N (Dual D flip-flop). Фирма производитель: Texas Instruments.

Эта микросхема содержит два D-триггера. Каждый триггер имеет прямой выход Q и инверсный ему выход. Помимо входа приема данных D, у каждого триггера имеется положительный динамический вход синхронизации приема данных СLK (Clock), два асинхронных приоритетных потенциальных инверсных входа PR (Preset) и CLR (Clear) помощью которых триггер устанавливает свой прямой выход в состояние Q = 1 или Q = 0 (соответственно). Одновременное активное воздействие логическим нулем на входы PRE и CLR должно быть исключено.

Логика управления триггером SN7474N поясняется на Рис.П.4 и Таблицей П.3.

Таблица П.3. Управление D-триггером

Таблица П.3. Управление D-триггером

SN7474N

Входы |

Выходы |

||||

D |

CLK |

СLR |

PR |

Q |

Инв. |

0 |

0-1 |

1 |

1 |

0 |

1 |

1 |

0-1 |

1 |

1 |

1 |

0 |

Х |

Х |

0 |

1 |

0 |

1 |

Х |

Х |

1 |

0 |

1 |

0 |

Рис.П.4. УГО D-триггера Примечание: 0-1 перепад уровней от 0 к 1

Параметры микросхемы SN7474N:

питание: 4.5-5.5V;

уровни логических сигналов: стандарт ТТЛ;

технология: ТТЛ;

максимальная частота записи (CLC): 25МHz;

задержка установки (по входам PRE и CLR): 20ns;

нагрузочные параметры: см. SN7400N;

средняя мощность потребления (на один триггер):

79 mW.

Отечественный аналог: К155ТМ2 (см. Рис.П.4).

Схемотехника цифрового вольтметра

Нумерация блока, подблока, схем, подсхем и микросхем отражает последовательность создания моделирующей программы цифрового вольтметра.

Первой разработана и отлажена индикаторная часть, далее – измерительная часть, а завершала разработку отладка взаимодействия этих частей между собой и с отдельными элементами управления и сигнализации.

4.1. Индикаторная часть цифрового вольтметра.

Бл1 «Преобразователь кодов» - блок комбинационных цифровых устройств, осуществляющих формирование заданного выходного кода в момент появления на входе этого блока преобразуемой кодовой комбинации.

Бл1 построен по принципу поэтапного преобразования кодов (Лист 2 чертежей принципиальной электрической схемы цифрового вольтметра).

ПБл1-входящий в Бл1 подблок схем, аналогичных отечественной микросхеме К155ПР7 или иностранной микросхемы SN185N, предназначеннs[ для преобразования двоичного кода в двоично-десятичный код.

Микросхема К155ПР7 представляет собой постоянное запоминающее устройство (ПЗУ), запрограммированное на выдачу выходных кодовых комбинаций в ответ на подачу входные кодовых комбинаций в соответствие со следующей таблицей истинности:

Таблица П.4. Логика микросхемы К155ПР7.

-

Входной код

Выходной код

32

16

8

4

2

40

20

10

8

4

2

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

1

0

0

0

1

0

0

0

0

0

1

0

0

0

0

1

1

0

0

0

0

1

1

0

0

1

0

0

0

0

0

1

0

0

0

0

1

0

1

0

0

1

0

0

0

0

0

1

1

0

0

0

1

0

0

1

0

0

1

1

1

0

0

1

0

1

0

0

1

0

0

0

0

0

1

0

1

1

0

1

0

0

1

0

0

1

1

0

0

0

1

0

1

0

0

1

0

0

0

0

0

1

0

1

1

0

1

0

0

0

1

0

1

1

0

0

0

1

0

0

1

0

0

1

1

0

1

0

1

0

0

1

1

0

1

1

1

0

0

1

0

1

0

0

0

1

1

1

1

0

1

1

0

0

0

1

0

0

0

0

0

1

1

0

0

1

1

0

0

0

1

0

1

1

0

1

0

1

0

0

1

0

0

1

1

0

1

1

1

0

0

1

1

0

1

1

1

0

0

1

0

1

0

0

1

0

0

0

0

0

1

0

1

0

1

1

0

0

0

0

1

1

0

1

1

0

1

0

0

0

1

0

1

0

1

1

1

1

0

0

0

1

1

1

1

0

0

0

1

0

0

1

0

0

1

1

0

0

1

1

0

1

0

0

0

1

1

0

1

0

1

0

1

0

0

1

1

1

0

1

1

1

0

1

0

1

0

1

1

1

0

0

1

0

1

0

1

1

1

1

1

0

1

1

1

0

1

0

0

1

1

1

1

0

1

1

0

0

0

0

1

1

1

1

1

1

1

0

0

0

1

Логика преобразования входного весового кода в другой весовой код, реализованная микросхемой К155ПР7 заключается в том, чтобы сумма весов входного кода (значений его единичных разрядов) равнялась сумме весов выходного кода (значений своих единичных разрядов). Например, в предпоследней строке Таблицы П.5 входной код имеет вес 32+16+8+4 = 60, а выходной код равен ему по весу, поскольку 40+20 = 64.

Для преобразования исходного двоичного кода в двоично-десятичный код единиц, десятков и сотен необходимы три такие схемы, соединенные как показано на листе 3 чертежей принципиальной электрической схемы цифрового вольтметра.

Аналог ПР7 (Сх1-Сх3) – представляют из себя одинаковые типовые блоки собранные на логических схемах, которые реализуют логику преобразования аналогичную микросхеме К155ПР7.

Каждый такой блок, как показано на листе 4 чертежей принципиальной электрической схемы цифрового вольтметра, представляет собой соединение пяти схем преобразующих четырехразрядный двоичный весовой код в весовой код 1-2-4-5, согласно таблице истинности, приведенной в Таблице П.5.

Таблица П.5. Логика преобразователя двоичного весового кода в весовой код 1-2-4-5.

-

Входной код

Выходной код

8

4

2

1

5

4

2

1

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

1

0

0

1

0

0

0

1

0

0

0

1

1

0

0

1

1

0

1

0

0

0

1

0

0

0

1

0

1

1

0

0

0

0

1

1

0

1

0

0

1

0

1

1

1

1

0

1

0

1

0

0

0

1

0

1

1

1

0

0

1

1

1

0

0

1

0

1

0

*

*

*

*

1

0

1

1

*

*

*

*

1

1

0

0

*

*

*

*

1

1

0

1

*

*

*

*

1

1

1

0

*

*

*

*

1

1

1

1

*

*

*

*

0

0

0

0

*

*

*

*

0

0

0

1

*

*

*

*

0

0

1

0

*

*

*

*

Примечание: символ * в значениях выходного кода указывает на то, что эти значения безразличны, поскольку осуществляется только преобразовании кодов десятичных цифр от 0 до 9.

Логика преобразования кодов, приведенная в Таблице П.5 аналогична логике Таблицы П.4.

На листе 5 чертежей принципиальной электрической схемы цифрового вольтметра показано соединение логических микросхем, реализующее логику преобразования в соответствие с Таблицей 6. При этом не ставилась задача унификации логических микросхем или задача минимизации используемых логических микросхем.

Исходя из вышесказанного, для реализации ПБл1 используются 15-ть таких подсхем пронумерованных от ПСх1 до ПСх15. Лист 5 чертежей принципиальной электрической схемы цифрового вольтметра показывает схемотехнику одной такой подсхемы.

Для иллюстрации возможности дальнейшего наращивания разрядности преобразуемого кода в схеме ПБл1 (лист 3 чертежей принципиальной электрической схемы цифрового вольтметра) и в схеме Аналог ПР7 (лист 4 этих чертежей) показаны входы и выходы, в которых нет необходимости для реализации цифрового вольтметра с пределом измерения 10В и с погрешностью измерения 0.05В. Ненужные для этого входы – заземлены, а выходы – не используются. Следовательно, часть из 90-ста логических микросхем в ПБл1 реально не используется.

Формирователь общей шины двоичных кодов десятичных цифр (Сх4).

Для реализации принципа динамической индикации двоичные коды десятичных цифр сотен, десятков и единиц поступают одновременно на входы всех семисегментных индикаторов поочередно по общей шине, изображенной на листе 6 чертежей принципиальной электрической схемы цифрового вольтметра.

Для возможности передачи сигналов на одну линию от трех источников в Сх4 использованы формирующие микросхемы DD91-DD93 с тремя состояниями выхода, имеющие вход управления этими состояниями.

Поочередно поступающими сигналами включения передачи кодов: Вкл.С, Вкл.Д и Вкл.Е в общие линии шины передаются, соответственно, только код цифры сотен или десятков или единиц.

При этом на каждой из четырех линий общей шины два не передающих свои коды формирователя обеспечивают на своих выходах высокоимпедансное (Z) состояние, не влияющее на логические состояния формирователя, передающего в линию свой разряд кода.

Дешифратор (Сх5).

Как это следует из листа 7 чертежей принципиальной электрической схемы цифрового вольтметра, используется неполный дешифратор с инверсными выходами для входного четырехразрядного двоичного весового кода. Дешифрируются только двоичные коды десятичных цифр от 0 до 9.

Каждый из трех дешифраторов построен на 9-ти логических микросхемах И-НЕ (DD94-DD98) и 4-х логических инверторах НЕ (DD99).

Дешифратор является первой частью преобразования двоичных кодов цифр в коды индикации.

Шифратор в код индикации (Сх6).

Этот элемент представляет собой вторую часть преобразователя двоичных кодов цифр в коды индикации. Логика шифрации зависит от вида используемого знакосинтезирующего индикатора для изображения цифр.

Шифраторов, изображенный на листе 8 чертежей принципиальной электрической схемы цифрового вольтметра, имеет 7-мь выходов в соответствии с входами управления сегментами используемого семисегментного индикатора (HL1-HL3), имеющими общий заземленный катод. Зажигание каждого сегмента от А доG производится уровнем логической 1 в соответствие с Таблицей П.1 этой пояснительной записки.

Шифратор построен на шести логических схемах 8И-НЕ (DD100-DD105), одной логической схеме 4И-НЕ (DD106A) и на одной логической схеме И (DD107A), необходимой для увеличения количества входов у одной из схем 8И-НЕ (DD102).

Усилитель (Сх7).

Усилитель предназначен для обеспечения тока 5mA, минимально необходимого для свечения каждого сегмента индикатора. Кроме того возможность перевода всех выходов усилителя в третье (Z) состояние позволяет, при необходимости, индикацию цифрового вольтметра.

Схема усилителя, как это следует из листа 9 чертежей принципиальной электрической схемы цифрового вольтметра, представляет собой семь независимых не инвертирующих микросхем с повышенной нагрузочной способностью (DD108-DD109), имеющих дополнительный вход управления состоянием своего выхода.

При высоком логическом уровне 1 на входе управления выход каждой микросхемы имеет третье (Z) состояние. Низкий уровень на объединенных входах управления этими микросхемами передает коды показания измерительной части цифрового вольтметра на семисегментные индикаторы.

Подбор номиналов резисторов R1-R7 обеспечивает минимально необходимые токи для свечения сегментов этих коммутируемых индикаторов. Таким подбором определены R1-R7 = 600 Ом.

Коммутатор индикаторов и источников сигналов в общую шину индикаторов (Сх8).

Коммутатор, согласно листу 10 чертежей принципиальной электрической схемы цифрового вольтметра, представляет собой кольцевой сдвиговой регистр на трех D-триггерах (DD111, DD 112).

При начальном сбросе только один из триггеров этого регистра устанавливается в единичное состояние (DD111A). Единственная логическая 1 на выходе одного из триггеров очередным импульсом с выхода подсхемы делителя частоты импульсов на 10 (ПСх16) перемещается в присоединенный к нему смежный триггер. Триггер DD102A передает ее в DD111A, закольцовывая схему сдвигового регистра.

Делитель частоты импульсов на 10 (ПСх16).

Для снижения частоты переключения индикаторов до минимально допустимой величины (с целью экономии потребляемой индикаторами мощности от источника энергоснабжения) коммутатор (Сх8) использует импульсную последовательность, частота которой в 10 раз ниже исходной частоты импульсов в измерительной части цифрового вольтметра (от которой зависит его быстродействие).

На листе 11 чертежей принципиальной электрической схемы цифрового вольтметра приведен необходимый для этого делитель частоты на микросхеме DD114 с расширенными входами сброса в 0 (при R01 = R02 = 1) и записи 1 в старший (QD) и младший (QA) разряды (при R91 = R92 = 1).