- •Глава 1. Основы коммутации

- •1.1 Эволюция локальных сетей

- •1.2 Функционирование коммутаторов локальной сети

- •1.3 Методы коммутации

- •1.4 Конструктивное исполнение коммутаторов

- •1.5 Физическое стекирование коммутаторов

- •1.6 Типы интерфейсов коммутаторов

- •1.7 Архитектура коммутаторов

- •1.7.1 Архитектура с разделяемой шиной

- •1.7.2 Архитектура с разделяемой памятью

- •1.7.3 Архитектура на основе коммутационной матрицы

- •1.8 Характеристики, влияющие на производительность коммутаторов

- •1.8.1 Скорость фильтрации и скорость продвижения кадров

- •1.8.2. Размер таблицы коммутации

- •1.8.3. Объем буфера кадров

- •1.9. Управление потоком в полудуплексном и дуплексном режимах

- •1.10. Технологии коммутации и модель osi

- •1.11. Программное обеспечение коммутаторов

- •1.12. Общие принципы сетевого дизайна

- •1.13 Трехуровневая иерархическая модель сети

- •Глава 2. Начальная настройка коммутатора

- •2.1 Классификация коммутаторов по возможности управления

- •2.2. Средства управления коммутаторами

- •2.3. Подключение к коммутатору

- •2.3.1. Подключение к консоли интерфейса командной строки коммутатора

- •2.4 Начальная конфигурация коммутатора

- •2.4.1. Вызов помощи по командам

- •2.4.2. Базовая конфигурация коммутатора

- •2.5. Подключение к Web-интерфейсу управления коммутатора

- •2.6. Загрузка нового программного обеспечения на коммутатор

- •2.7. Загрузка и резервное копирование конфигурации коммутатора

- •Глава 3. Обзор функциональных возможностей коммутаторов

- •Глава 4. Виртуальные локальные сети (vlan)

- •4.1 Типы vlan

- •4.2 Vlan на основе портов

- •4.3. Vlan на основе стандарта ieee 802.1q

- •4.3.1 Некоторые определения ieee 802.1q

- •4.3.2. Теги vlan 802.1q

- •4.3.4. Продвижение кадров vlan 802.1q

- •4.3.5. Пример настройки vlan 802.1q

- •4.4. Статические и динамические vlan

- •4.5. Протокол gvrp

- •4.5.1 Таймеры gvrp

- •4.5.2. Пример настройки протокола gvrp

- •4.6.1. Формат кадра q-in-q

- •4.6.2 Реализации q-in-q

- •4.6.3 Значения tpid в кадрах q-in-q vlan

- •4.6.4 Роли портов в Port-based q-in-q и Selective q-in-q vlan

- •4.6.5. Политики назначения внешнего тега и приоритета в q-in-q vlan

- •4.6.6. Базовая архитектура сети с функцией Port-based q-in-q

- •4.6.7. Пример настройки функции Port-based q-in-q

- •4.6.8. Пример настройки функции Selective q-in-q

- •4.7. Vlan на основе портов и протоколов – стандарт ieee 802.1v

- •4.7.1 Пример настройки ieee 802.1v vlan

- •4.8 Асимметричные vlan

- •4.8.1. Примеры настройки асимметричных vlan

- •4.9. Функция Traffic Segmentation

- •4.9.1 Примеры использования и настройки функции Traffic Segmentation

- •Глава 5. Функции повышения надежности и производительности

- •5.1 Протоколы Spanning Tree

- •5.2.1. Понятие петель

- •5.2.2. Построение активной топологии связующего дерева

- •5.2.4 Состояния портов

- •5.2.5 Таймеры stp

- •5.2.6 Изменение топологии

- •5.2.8. Настройка stp

- •5.3.1 Роли портов

- •5.3.2. Формат bpdu

- •5.3.3. Быстрый переход в состояние продвижения

- •5.3.4 Механизм предложений и соглашений

- •5.3.5 Новый механизм изменения топологии

- •1. Определение изменений топологии.

- •2. Распространение информации об изменении топологии.

- •5.3.6 Стоимость пути rstp

- •5.3.7. Совместимость с stp

- •5.3.8. Настройка rstp

- •5.4.1 Логическая структура mstp

- •5.4.3. Формат mstp bpdu

- •5.4.4 Вычисления в mstp

- •5.4.5 Роли портов mstp

- •5.4.6 Пример топологии mstp

- •5.4.7 Состояние портов mstp

- •5.4.8 Счетчик переходов mstp

- •5.4.9 Совместимость с stp и rstp

- •5.4.10 Настройка протокола mstp на коммутаторах

- •5.5 Дополнительные функции защиты от петель

- •5.5.1 Настройка функции LoopBack Detection

- •5.6 Функции безопасности stp

- •5.7 Агрегирование каналов связи

- •5.7.1 Настройка статических и динамических агрегированных каналов

- •Глава 6. Качество обслуживания (QoS)

- •6.1. Модели QoS

- •6.2. Приоритезация пакетов

- •6.3. Классификация пакетов

- •4 Очереди приоритетов

- •8 Очередей приоритетов

- •6.4. Маркировка пакетов

- •6.5. Управление перегрузками и механизмы обслуживания очередей

- •6.6. Механизм предотвращения перегрузок

- •6.7 Контроль полосы пропускания

- •6.8 Пример настройки QoS

- •Глава 7. Функции обеспечения безопасности и ограничения доступа к сети

- •7.1 Списки управления доступом (acl)

- •7.1.1 Профили доступа и правила acl

- •7.1.2 Примеры настройки acl

- •7.2 Функции контроля над подключением узлов к портам коммутатора

- •7.2.1 Функция Port Security

- •7.2.1.1 Пример настройки функции Port Security

- •7.2.2 Функция ip-mac-Port Binding

- •7.2.2.1 Пример настройки функции ip-mac-Port Binding

- •7.3 Аутентификация пользователей 802.1x

- •7.3.1 Роли устройств в стандарте 802.1х

- •7.3.4. Состояние портов коммутатора

- •7.4.1. Пример настройки 802.1х Guest vlan

- •7.5 Функции защиты цпу коммутатора

- •7.5.1 Функция Safeguard Engine

- •7.5.1.1 Пример настройки функции Safeguard Engine

- •7.6.1 Функция cpu Interface Filtering

- •7.6.1.1 Пример настройки функции cpu Interface Filtering

- •Глава 8. Многоадресная рассылка

- •8.1 Адресация многоадресной ip-рассылки

- •8.3 Подписка и обслуживание групп

- •8.4 Управление многоадресной рассылкой на 2-м уровне модели osi (igmp Snooping)

- •8.4.1 Пример настройки igmp Snooping

- •8.5 Функция igmp Snooping Fast Leave

- •8.5.1. Пример настройки igmp Snooping Fast Leave

- •Глава 9. Функции управления коммутаторами

- •9.1 Управление множеством коммутаторов

- •9.1.1. Объединение коммутаторов в физический стек

- •9.1.2 Виртуальный стек. Технология Single ip Management (sim)

- •9.2 Протокол snmp

- •9.2.1 Компоненты snmp

- •9.2.2 База управляющей информации snmp

- •9.2.3 Типы сообщений протокола snmp

- •9.2.4 Безопасность snmp

- •9.2.5 Пример настройки протокола snmp

- •9.4 Функция Port Mirroring

- •Глава 10. Обзор коммутаторов d-Link

- •10.1 Неуправляемые коммутаторы

- •10.2 Коммутаторы серии Smart

- •10.3 Управляемые коммутаторы

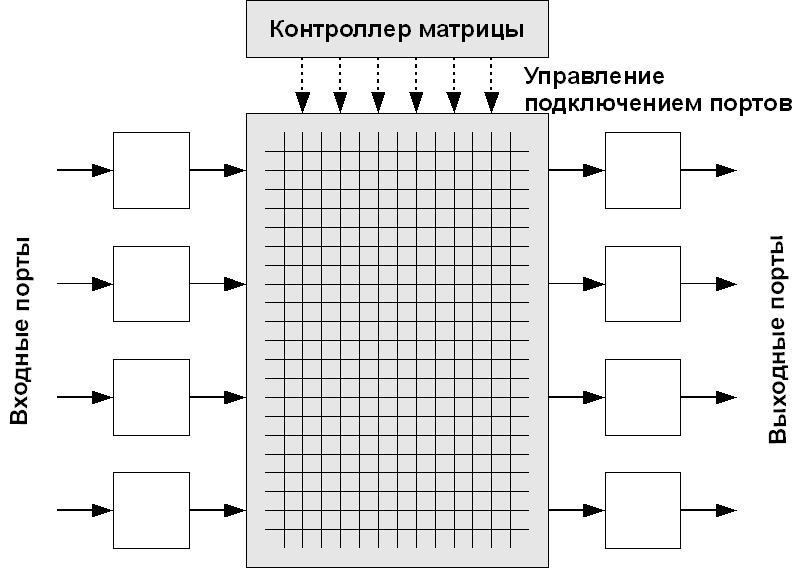

1.7.3 Архитектура на основе коммутационной матрицы

Параллельно с появлением архитектуры с разделяемой памятью (в середине 1990-х годов) была разработана архитектура на основе коммутационной матрицы (Crossbar architecture). Эта архитектура используется для построения коммутаторов различных типов.

Существует множество вариаций архитектуры этого типа. Базовая архитектура на основе коммутационной матрицы N x N непосредственно соединяетN входных портов с N выходными портами в виде матрицы. В местах пересечения проводников, соединяющих входы и выходы,находятся коммутирующие устройства,которыми управляет специальный контроллер. В каждый момент времени, анализируя адресную информацию, контроллер сообщает коммутирующим устройствам, какой выход должен быть подключен к какому входу. В том случае, если два входящих пакета от разных портов-источников будут переданы на один и тот же выходной порт, он будет заблокирован. Существуют различные подходы к решению этой проблемы: повышение производительности матрицы по сравнению с производительностью входных портов или использование буферов памяти и арбитров.

Несмотря на простой дизайн, одной из фундаментальных проблем архитектуры на основе коммутационной матрицы остается ее масштабируемость. При увеличении количества входов и выходов усложняется схемотехника матрицы и в особенности контроллера. Поэтому для построения многопортовых коммутационных матриц используется другой подход,который заключается в том, что простые коммутационные матрицы связываются между собой, образуя одну большую коммутационную матрицу.

Рис. 1.14. Архитектура на основе коммутационной матрицы

Можно выделить два типа коммутаторов на основе коммутационной матрицы:

· коммутаторы на основе коммутационной матрицы с буферизацией (bufferedcrossbar);

· коммутаторы на основе коммутационной матрицы с арбитражем (arbitrated crossbar).

Коммутаторы на основе коммутационной матрицы с буферизацией

В коммутаторах на основе коммутационной матрицыс буферизацией буферы расположены на трех основных стадиях: на входе и выходе, и непосредственно на коммутационной матрице. Благодаря наличию очередей на трех стадиях, эта архитектура позволяет избежать сложностей, связанных с реализацией механизма централизованного арбитража. На выходе каждой из стадий осуществляется управление очередями с помощью одного из алгоритмов диспетчеризации.

Несмотря на то, что эта архитектура является простейшей архитектурой коммутаторов, из-за независимости стадий для нее существуют сложности с реализацией качества обслуживания ( QoS ) в пределах коммутатора.

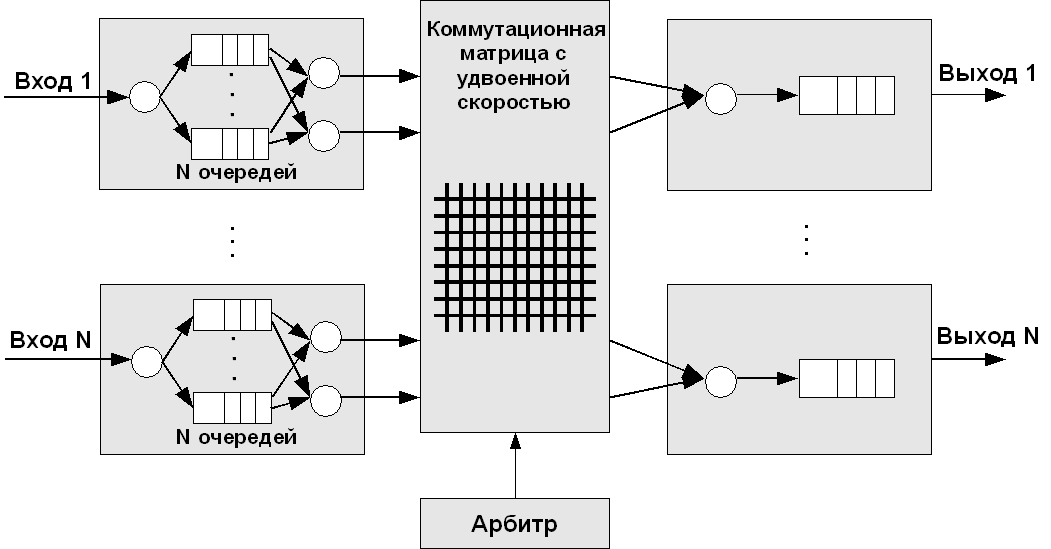

Коммутаторы на основе коммутационной матрицы с арбитражем

Эта архитектура характеризуется наличием без буферных коммутирующих элементов и арбитра, который управляет передачей трафика между входами и выходами матрицы.Отсутствие буферов у коммутирующих элементов компенсируется наличием буферов входных и выходных портов. Обычно разработчики используют один из трех методов буферизации: выходные буферы, входные буферы, комбинированные входные и выходные буферы.

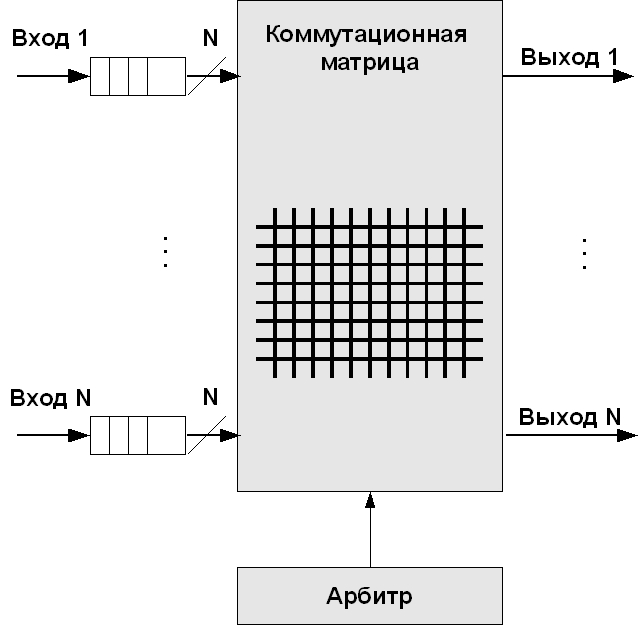

В коммутаторах с входными очередями (Input-Queued Switch )память каждого входного порта организована в виде очередей типа FIFO (First Input First Output , «первым пришел, первым ушел»), которая используется для буферизации пакетов перед началом процесса коммутации. Одной из проблем этого типа коммутационной матрицы является блокировка первым в очереди (Head-Of-Line blocking, HOL).Она возникает в том случае, когда коммутатор пытается одновременно передать пакеты из нескольких входных очередей на один выходной порт. При этом пакеты,находящиеся в начале этих очередей блокируют все остальные пакеты, находящиеся за ними. Для принятия решения о том, какой пакет и из какой очереди может получить доступ к матрице, используется арбитр. Перед передачей пакета входные порты направляют арбитру запросы на подключение к разделяемому ресурсу (в данном случае пути матрицы) и получают от него право на подключение.

Рис. 1.15.

Архитектура на основе коммутационной

матрицы с входными очередями

Рис. 1.15.

Архитектура на основе коммутационной

матрицы с входными очередями

Арбитр принимает решение о последовательности передачи пакетов из входных очередей на основе алгоритма диспетчеризации (scheduling algorithm).

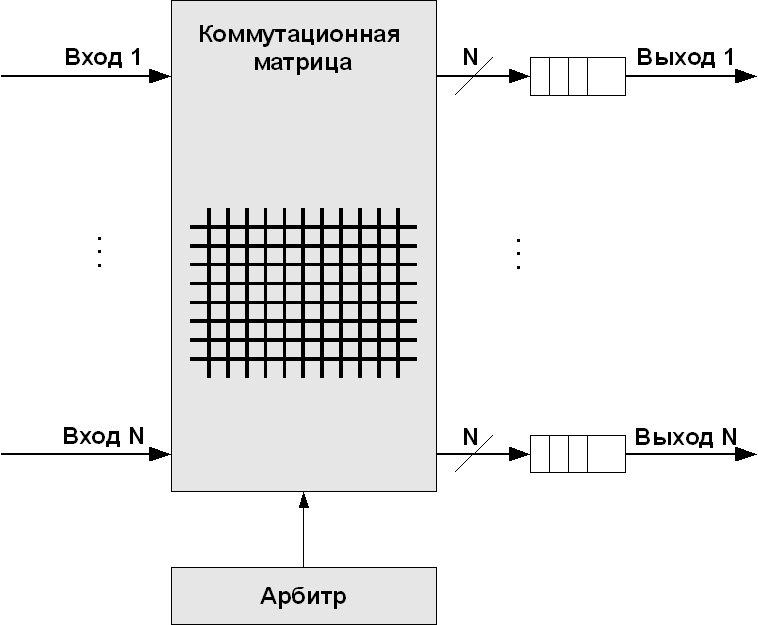

В коммутаторах с выходными очередями (output-queued switch) пакеты буферизируются только на выходных портах после завершения процесса коммутации. В этом случае удается избежать проблемы, связанной с блокированием очередей HOL . Коммутаторы этой архитектуры используют арбитр для управления временем, за которое пакеты коммутируются через матрицу. При правильно разработанном арбитре, коммутаторы с выходными очередями могут обеспечивать качество обслуживания (QoS).

Следует отметить, что выходной буфер каждого порта требует большего объема памяти по сравнению с входным буфером. Это позволяет избежать блокирования на выходе, когда все входные порты пытаются подключиться к одному выходу. Еще одним важным фактором, является скорость выполнения операции «запись» коммутируемых пакетов в выходную очередь. По этим двум причинам архитектура с выходными очередями должна быть реализована на высокоскоростных элементах, что делает ее очень дорогостоящей.

Рис. 1.16.

Архитектура на основе коммутационной

матрицы с выходными очередями

Рис. 1.16.

Архитектура на основе коммутационной

матрицы с выходными очередями

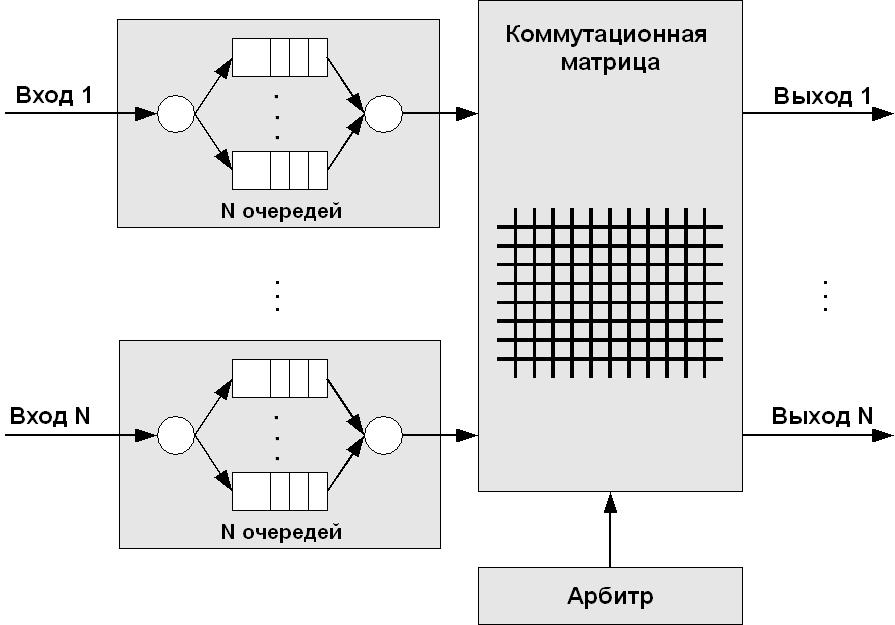

Коммутаторы с виртуальными очередями (Virtual Output Queues, VOQ ) позволяют преодолеть проблему блокировки очередей HOL , не внося издержек по сравнению с коммутаторами с выходными очередями. В этой архитектуре память каждого входного порта организована в виде N ( N –количество выходных портов) логических очередей типа FIFO , по одной для каждого выходного порта. Эти очереди используются для буферизации пакетов, поступающих на входной порт и предназначенных для выходного порта j ( j = 1,…. N ).

Рис. 1.17.

Архитектура на основе коммутационной

матрицы с виртуальными очередями

Рис. 1.17.

Архитектура на основе коммутационной

матрицы с виртуальными очередями

В том случае,если существует несколько виртуальных очередей, может возникнуть проблема, связанная с одновременным доступом к коммутационной матрице и блокировкой очередей. Для решения этой проблемы используется арбитр, который на основе алгоритма диспетчеризации выбирает пакеты из разных очередей.

В коммутаторах с комбинированными входными и выходными очередями (Combined Inputand Output Queued, CIOQ) буферы памяти подключены как к входным, так и выходным портам. Память каждого из входных портов организована в виде N виртуальных выходных очередей типа FIFO, по одной для каждого выходного порта. Каждый из N выходных портов также содержит очередь типа FIFO, которая используется для буферизации пакетов, ожидающих передачи через него. Система коммутации работает по принципу конвейера, каждая стадия которого называется временным слотом (time slot). В течение временного слота 1, который называется стадией прибытия, пакеты поступают на входные порты. Для передачи внутри коммутатора все пакеты сегментируются на ячейки фиксированного размера. Размер такой ячейки данных определяется производителем коммутатора. Каждая ячейка снабжается меткой с указанием размера, номера входного порта и порта назначения, и помещается в виртуальную выходную очередь соответствующего выходного порта. Входные порты отправляют «запросы на подключение к выходам» централизованному арбитру, а все выходные порты отправляют ему «информацию о перегрузке» (переполнении выходных буферов).

Во временной слот 2, который называется стадией диспетчеризации, ячейки передаются из входных очередей в выходные. Последовательность передачи ячеек определяется централизованным арбитром с помощью алгоритма диспетчеризации. Для того чтобы выходные очереди быстро заполнялись пакетами из входных очередей (с целью уменьшения задержки передачи пакетов и обеспечения QoS), алгоритм диспетчеризации должен обеспечивать циклическое высокоскоростное сопоставление входных и выходных очередей. Это сопоставление используется для настройки управляемых переключателей матрицы перед передачей пакетов с входов на выходы.

Во временной слот 3, который называется стадией передачи, осуществляется сборка пакетов и их передача с выходных портов.

Рис. 1.18.

Архитектура на основе коммутационной

матрицы с CIOQ

Рис. 1.18.

Архитектура на основе коммутационной

матрицы с CIOQ