- •Глава 1. Основы коммутации

- •1.1 Эволюция локальных сетей

- •1.2 Функционирование коммутаторов локальной сети

- •1.3 Методы коммутации

- •1.4 Конструктивное исполнение коммутаторов

- •1.5 Физическое стекирование коммутаторов

- •1.6 Типы интерфейсов коммутаторов

- •1.7 Архитектура коммутаторов

- •1.7.1 Архитектура с разделяемой шиной

- •1.7.2 Архитектура с разделяемой памятью

- •1.7.3 Архитектура на основе коммутационной матрицы

- •1.8 Характеристики, влияющие на производительность коммутаторов

- •1.8.1 Скорость фильтрации и скорость продвижения кадров

- •1.8.2. Размер таблицы коммутации

- •1.8.3. Объем буфера кадров

- •1.9. Управление потоком в полудуплексном и дуплексном режимах

- •1.10. Технологии коммутации и модель osi

- •1.11. Программное обеспечение коммутаторов

- •1.12. Общие принципы сетевого дизайна

- •1.13 Трехуровневая иерархическая модель сети

- •Глава 2. Начальная настройка коммутатора

- •2.1 Классификация коммутаторов по возможности управления

- •2.2. Средства управления коммутаторами

- •2.3. Подключение к коммутатору

- •2.3.1. Подключение к консоли интерфейса командной строки коммутатора

- •2.4 Начальная конфигурация коммутатора

- •2.4.1. Вызов помощи по командам

- •2.4.2. Базовая конфигурация коммутатора

- •2.5. Подключение к Web-интерфейсу управления коммутатора

- •2.6. Загрузка нового программного обеспечения на коммутатор

- •2.7. Загрузка и резервное копирование конфигурации коммутатора

- •Глава 3. Обзор функциональных возможностей коммутаторов

- •Глава 4. Виртуальные локальные сети (vlan)

- •4.1 Типы vlan

- •4.2 Vlan на основе портов

- •4.3. Vlan на основе стандарта ieee 802.1q

- •4.3.1 Некоторые определения ieee 802.1q

- •4.3.2. Теги vlan 802.1q

- •4.3.4. Продвижение кадров vlan 802.1q

- •4.3.5. Пример настройки vlan 802.1q

- •4.4. Статические и динамические vlan

- •4.5. Протокол gvrp

- •4.5.1 Таймеры gvrp

- •4.5.2. Пример настройки протокола gvrp

- •4.6.1. Формат кадра q-in-q

- •4.6.2 Реализации q-in-q

- •4.6.3 Значения tpid в кадрах q-in-q vlan

- •4.6.4 Роли портов в Port-based q-in-q и Selective q-in-q vlan

- •4.6.5. Политики назначения внешнего тега и приоритета в q-in-q vlan

- •4.6.6. Базовая архитектура сети с функцией Port-based q-in-q

- •4.6.7. Пример настройки функции Port-based q-in-q

- •4.6.8. Пример настройки функции Selective q-in-q

- •4.7. Vlan на основе портов и протоколов – стандарт ieee 802.1v

- •4.7.1 Пример настройки ieee 802.1v vlan

- •4.8 Асимметричные vlan

- •4.8.1. Примеры настройки асимметричных vlan

- •4.9. Функция Traffic Segmentation

- •4.9.1 Примеры использования и настройки функции Traffic Segmentation

- •Глава 5. Функции повышения надежности и производительности

- •5.1 Протоколы Spanning Tree

- •5.2.1. Понятие петель

- •5.2.2. Построение активной топологии связующего дерева

- •5.2.4 Состояния портов

- •5.2.5 Таймеры stp

- •5.2.6 Изменение топологии

- •5.2.8. Настройка stp

- •5.3.1 Роли портов

- •5.3.2. Формат bpdu

- •5.3.3. Быстрый переход в состояние продвижения

- •5.3.4 Механизм предложений и соглашений

- •5.3.5 Новый механизм изменения топологии

- •1. Определение изменений топологии.

- •2. Распространение информации об изменении топологии.

- •5.3.6 Стоимость пути rstp

- •5.3.7. Совместимость с stp

- •5.3.8. Настройка rstp

- •5.4.1 Логическая структура mstp

- •5.4.3. Формат mstp bpdu

- •5.4.4 Вычисления в mstp

- •5.4.5 Роли портов mstp

- •5.4.6 Пример топологии mstp

- •5.4.7 Состояние портов mstp

- •5.4.8 Счетчик переходов mstp

- •5.4.9 Совместимость с stp и rstp

- •5.4.10 Настройка протокола mstp на коммутаторах

- •5.5 Дополнительные функции защиты от петель

- •5.5.1 Настройка функции LoopBack Detection

- •5.6 Функции безопасности stp

- •5.7 Агрегирование каналов связи

- •5.7.1 Настройка статических и динамических агрегированных каналов

- •Глава 6. Качество обслуживания (QoS)

- •6.1. Модели QoS

- •6.2. Приоритезация пакетов

- •6.3. Классификация пакетов

- •4 Очереди приоритетов

- •8 Очередей приоритетов

- •6.4. Маркировка пакетов

- •6.5. Управление перегрузками и механизмы обслуживания очередей

- •6.6. Механизм предотвращения перегрузок

- •6.7 Контроль полосы пропускания

- •6.8 Пример настройки QoS

- •Глава 7. Функции обеспечения безопасности и ограничения доступа к сети

- •7.1 Списки управления доступом (acl)

- •7.1.1 Профили доступа и правила acl

- •7.1.2 Примеры настройки acl

- •7.2 Функции контроля над подключением узлов к портам коммутатора

- •7.2.1 Функция Port Security

- •7.2.1.1 Пример настройки функции Port Security

- •7.2.2 Функция ip-mac-Port Binding

- •7.2.2.1 Пример настройки функции ip-mac-Port Binding

- •7.3 Аутентификация пользователей 802.1x

- •7.3.1 Роли устройств в стандарте 802.1х

- •7.3.4. Состояние портов коммутатора

- •7.4.1. Пример настройки 802.1х Guest vlan

- •7.5 Функции защиты цпу коммутатора

- •7.5.1 Функция Safeguard Engine

- •7.5.1.1 Пример настройки функции Safeguard Engine

- •7.6.1 Функция cpu Interface Filtering

- •7.6.1.1 Пример настройки функции cpu Interface Filtering

- •Глава 8. Многоадресная рассылка

- •8.1 Адресация многоадресной ip-рассылки

- •8.3 Подписка и обслуживание групп

- •8.4 Управление многоадресной рассылкой на 2-м уровне модели osi (igmp Snooping)

- •8.4.1 Пример настройки igmp Snooping

- •8.5 Функция igmp Snooping Fast Leave

- •8.5.1. Пример настройки igmp Snooping Fast Leave

- •Глава 9. Функции управления коммутаторами

- •9.1 Управление множеством коммутаторов

- •9.1.1. Объединение коммутаторов в физический стек

- •9.1.2 Виртуальный стек. Технология Single ip Management (sim)

- •9.2 Протокол snmp

- •9.2.1 Компоненты snmp

- •9.2.2 База управляющей информации snmp

- •9.2.3 Типы сообщений протокола snmp

- •9.2.4 Безопасность snmp

- •9.2.5 Пример настройки протокола snmp

- •9.4 Функция Port Mirroring

- •Глава 10. Обзор коммутаторов d-Link

- •10.1 Неуправляемые коммутаторы

- •10.2 Коммутаторы серии Smart

- •10.3 Управляемые коммутаторы

1.7 Архитектура коммутаторов

Одним из основных компонентов всего коммутационного оборудования является коммутирующая матрица (switch fabric). Коммутирующая матрица представляет собой чипсет, соединяющий множество входов с множеством выходов на основе фундаментальных технологий и принципов коммутации. Коммутирующая матрица выполняет три функции:

· переключает трафик с одного порта матрицы на другой, обеспечивая их равнозначность;

· предоставляет качество обслуживания (Quality of Service, QoS);

· обеспечивает отказоустойчивость.

Поскольку коммутирующая матрица является ядром аппаратной платформы, к ней предъявляются требования по масштабированию производительности и возможности быстрого развития системы QoS .

Производительность коммутирующей матрицы (switch capacity)определяется как общая полоса пропускания (bandwidth), обеспечивающая коммутацию без отбрасывания пакетов трафика любого типа (одноадресного, многоадресного, широковещательного).

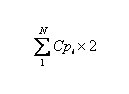

«Неблокирующей»коммутирующей матрицей (non-blocking switch fabric) является такая матрица, у которой производительность и QoS не зависят от типа трафика, коммутируемого через матрицу и производительность равна сумме скоростей всех портов:

Мбит/с * ,

Мбит/с * ,

где N – количество портов, Cpi- максимальная производительность протокола, поддерживаемого i-м портом коммутатора.

* Умножение на 2 для дуплексного режима работы.

Например,производительность коммутатора с 24 портами 10/100 Мбит/с и 2 портами 1 Гбит/с вычисляется следующим образом:

((24 х 100 Мбит/с) +(2 х 1 Гбит/с)) х 2 = 8.8 Гбит/с

Коммутатор обеспечивает портам равноправный доступ к матрице, если в системе не установлено преимущество одних портов над другими.

Поскольку коммутирующая матрица располагается в ядре платформы коммутатора, то одним из наиболее важных вопросов остается ее отказоустойчивость. Этот вопрос решается за счет реализации отказоустойчивой архитектуры, предусматривающей резервирование критичных для работы коммутатора блоков.

Одним из ключевых компонентов архитектуры современных коммутаторов является контроллер ASIC (Application Specific Integrated Circuit). Контроллеры ASIC представляют собой быстродействующие и относительно недорогие кремниевые кристаллы, которые предназначены для выполнения определенных операций. Использование в архитектуре коммутаторов контроллеров ASIC повышает производительность системы, т.к. ACIS выполняет операции аппаратно, благодаря чему не возникают накладные расходы, связанные с выборкой и интерпретацией хранимых команд. Современные контроллеры ACIS часто содержат на одном кристалле 32-битные процессоры, блоки памяти, включая ROM, RAM, EEPROM, Flash,и встроенное программное обеспечение. Такие ASIC получили название System-on-a-Chip (SoC).

В настоящее время существует много типов архитектур коммутирующих матриц. Выбор архитектуры матрицы во многом определяется ролью коммутатора в сети и количеством трафика,которое ему придется обрабатывать. В действительности, матрица обычно реализуется на основе комбинации двух или более базовых архитектур. Рассмотрим самые распространенные типы архитектур коммутирующих матриц.