- •А. В. Поздняков, б. Я. Цилькер микропроцессоры и микропроцессорные системы

- •Часть 1

- •(Учебное пособие)

- •Содержание

- •1. Микропроцессорные системы

- •1.1. Историческая справка

- •1.2. Архитектура мпс с магистрально-модульной организацией

- •1.3. Режимы работы мпс

- •2. Микропроцессорный модуль

- •2.1. Центральный процессор

- •2.1.1. Классификация микропроцессоров

- •2.1.2. Структура центрального процессора

- •2.1.2.1. Краткая характеристика микропроцессора Intel 8086

- •2.1.2.2. Архитектура микропроцессора Intel 8086

- •2.1.2.3. Программная модель микропроцессора Intel 8086

- •2.1.2.4. Представление информации в мп Intel 8086

- •2.1.2.5. Способы адресации операндов в мп Intel 8086

- •2.1.2.6. Система команд мп Intel 8086

- •2.1.2.7. Содержание цикла команды, типовые машинные циклы мп Intel 8086

- •2.1.2.8. Входные и выходные сигналы мп Intel 8086

- •2.2. Сопроцессор

- •2.3. Генератор тактовых импульсов

- •2.4. Системный контроллер

- •2.5. Согласующие элементы микропроцессорных систем

- •2.5.1. Шинные формирователи

- •2.5.2. Буферные регистры

- •2.6. Контроллер прерываний

- •2.7. Контроллер прямого доступа к памяти

- •2.8. Программируемый таймер

- •3. Модуль памяти

- •3.1. Организация модуля памяти

- •3.2. Распределение адресного пространства зу

- •3.3. Декодирование старших разрядов адреса.

- •3.3.1. Декодирование адресов методом линейной выборки

- •3.3.2. Декодирование адресов с помощью логических компараторов

- •3.3.3. Декодирование адресов с применением комбинационных логических схем

- •3.4. Выбор типа зу

- •3.5. Функциональная схема модуля памяти

- •3.6. Обеспечение необходимой емкости зу

- •3.6.1. Увеличение разрядности зу

- •3.6.2. Увеличение адресного пространства зу

- •4. Модуль ввода-вывода

- •4.1. Интерфейс ввода-вывода

- •4.2. Параллельные порты

- •4.2.1. Параллельный порт вывода

- •4.2.2. Параллельный порт ввода

- •4.2.3. Параллельные порты ввода-вывода

- •4.3. Последовательные порты

- •4.3.1. Последовательный асинхронный порт вывода

- •4.3.2. Последовательный асинхронный порт ввода

- •4.3.3. Программируемый последовательный интерфейс

- •4.4. Организация обращения к портам ввода/вывода

- •4.4.1. Обращение к портам ввода/вывода с помощью специальных команд

- •4.4.2. Обращение к портам ввода/вывода с помощью команд пересылок

- •4.5. Способы организации ввода/ вывода информации в мпс

- •4.5.1. Организация ввода/вывода информации под управлением основной программы

- •4.5.2. Организация ввода/вывода в режиме прерывания программы

- •4.5.3. Организация ввода/вывода в режиме прямого доступа к памяти

- •Система команд микропроцессора Intel 8086 Команды пересылки данных

- •Арифметические команды

- •Логические команды

- •Команды передачи управления

- •Команды управления процессором

- •Команды обработки строк

- •Литература

2.1.2. Структура центрального процессора

Структуру центрального процессора будем рассматривать на примере микропроцессора Intel 8086 (в странах восточной Европы его аналог производился с маркой К1810ВМ86) [МИКР86].

2.1.2.1. Краткая характеристика микропроцессора Intel 8086

МП Intel 8086 выпущен в июне 1978 г., содержит 29 тыс. транзисторов, тактовая частота 4,77–10 МГц, производительность менее 1 млн. операций в секунду, начальная цена 360 $.

Это однокристальный МП с фиксированной системой команд, c мультиплексированной 20-разрядной шиной адреса и 16-разрядной шиной данных. Синхронизация работы МП осуществляется импульсами внешнего тактового генератора. МП выпускался в корпусе, имеющем 40 выводов. МП может работать с памятью до 1Мбайт, обмениваться информацией с 65536 портами ввода и 65536 портами вывода, имеет 256 различных прерываний. Питание МП осуществляется от источника с напряжением 5В. Максимально потребляемая мощность от источника питания 1,75 Вт.

2.1.2.2. Архитектура микропроцессора Intel 8086

Упрощенная структурная схема МП Intel 8086 и его условное обозначение представлены на рис. 2.2.

Рис. 2.2. Упрощенная структурная схема МП Intel 8086 (а) и его условное обозначение (б)

Микропроцессор включает два основных асинхронно работающих устройства: блок выполнения команд (Execution Unit) и блок сопряжения с шиной (Bus Interface Unit). В функции блока выполнения команд входит декодирование и выполнение команд, а в функции блока сопряжения с шиной - извлечение из памяти кода команд и их операндов, а также запись результатов в память. Блоки могут работать независимо друг от друга, и процессы преобразования и передачи информации в них могут идти параллельно.

Блок выполнения команд. Блок выполнения команд включает 16-разрядное АЛУ, регистры временного хранения, регистр состояния, 8 регистров общего назначения. Все регистры и внутренние шины блока 16-разрядные.

На АЛУ поступают коды команд из конвейера команд, расположенного в блоке сопряжения с шинами. Конвейер команд представляет собой буфер типа «очередь» (FIFO – First in First Out). Если в результате дешифрации кода команд в АЛУ необходимо получение одного или нескольких операндов по внешним шинам МП, то блок выполнения команд запрашивает блок сопряжения с шинами на получение и размещение необходимых данных в блоке сопряжения с шиной.

Блок регистров общего назначения включает восемь регистров. Четыре регистра AX, BX, CX, DX являются регистрами данных и используются при выполнении арифметических операций. Эти же регистры могут выполнять некоторые специальные функции, что нашло отражение в их мнемонических обозначениях:

AX (Accumulator) – аккумулятор;

BX (Base) – базовый регистр;

CX (Counter) – счетчик;

DX (Data) – регистр данных.

Регистры допускают раздельную адресацию к старшему байту (Н) и младшему байту (L). Они могут использоваться в виде набора 8-разрядных регистров AH, AL, BH, BL, CH, CL, DH, DL.

Регистры общего назначения указатель стека SP (Stack Pointer ), указатель базы BP (Base Pointer), регистр индекса источника SI (Source Index), регистр индекса приемника DI (Destination Index) называются адресными регистрами. В них хранятся относительные адреса, используемые для определения адресов операндов в пределах одного из сегментов памяти. Сегмент памяти - область памяти, состоящая из 64К ячеек с последовательно нарастающими адресами. В указателе стека SP содержится относительный адрес в пределах стекового сегмента памяти. В регистрах BP, SI и DI хранятся относительные адреса в пределах сегмента данных.

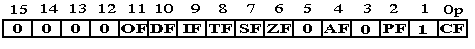

Р егистр

состояния или флагов

(FLAGS

register)

– 16-разрядный регистр хранит девять

признаков (флагов) (см. рис 2.3).

егистр

состояния или флагов

(FLAGS

register)

– 16-разрядный регистр хранит девять

признаков (флагов) (см. рис 2.3).

Рис. 2.3. Регистр флагов

Их делят на флаги состояния процессора и управляющие флаги. Если признак выполняется (удовлетворяется), в соответствующий триггер записывается 1 (флаг поднят), иначе 0 (флаг опущен).

Флагами состояния процессора являются:

CF (Carry Flag) – флаг (бит) переноса. Бит устанавливается, если при выполнении сложения возникает перенос из старшего разряда результата, а при выполнении вычитания – заем в старший разряд. При наличии переноса (заема) CF=1, иначе CF=0.

PF (Parity Flag) – флаг четности. Бит устанавливается, если сумма по модулю два младших 8 битов равна нулю. При четном числе единиц PF=1, иначе PF=0.

AF (Auxiliary carry Flag) – флаг вспомогательного переноса. Бит устанавливается, если при выполнении сложения возникает перенос из старшего бита младшей тетрады результата, а при выполнении вычитания – заем в старший бит младшей тетрады. При наличии переноса (заема) AF=1, иначе AF=0.

ZF (Zero Flag) – флаг нулевого результата. Бит устанавливается, если результат операции равен нулю, иначе бит ZF сбрасывается (ZF=0).

SF (Sign Flag) – флаг знака. Бит устанавливается, если старший бит результата равен единице, иначе бит SF сбрасывается.

OF (Overflow Flag) – флаг переполнения. Бит отображает переполнение разрядной сетки при выполнении операций с числами со знаком. Бит устанавливается, если возникает перенос в старший бит результата, но не возникает перенос из старшего бита результата (или же наоборот). Другими словами, бит устанавливается, если при сложении чисел одного знака результат имеет другой знак.

Управляющие флаги. Выставляя и сбрасывая их можно изменять ход выполнения операций процессором. Управляющими флагами в микропроцессоре Intel 8086 являются:

TF (Trap Flag) – флаг трассировки. Устанавливает для МП пошаговый режим выполнения программы, при котором после выполнения каждой команды МП приостанавливает свою работу. Этот режим используется при отладке программ.

IF (Interrupt Flag) – флаг разрешения прерывания. Установка флага (IF=1) разрешает прием микропроцессору запроса прерывания по входу INT.

DF (Direction Flag) – флаг направления. Он служит для автоматического увеличения или уменьшения адреса при обработке последовательности символов. При установленном бите адрес уменьшается (обработка символов “справа налево”), а при сброшенном – увеличивается (обработка символов “слева направо”).

Блок сопряжения с шиной. Блок сопряжения с шиной включает в себя:

16-разрядный регистр указатель команд IP (Instruction Pointer);

четыре 16-разрядных сегментных регистра CS, DS, SS, ES;

сумматор;

конвейер команд;

логику управления шиной.

Блок производит все пересылки данных и кодов для блока выполнения команд. В то время как блок выполнения команд занят выполнением команды, блок сопряжения получает последующие в программе коды команд из памяти и сохраняет их в конвейере команд. Это позволяет выдавать в блок выполнения сохраненные команды по мере необходимости без загрузки внешних шин микропроцессора. Блок сопряжения организует получение нового кода команды, как только второй байт из конвейера команд будет передан в блок выполнения. За один цикл с шины данных в блок сопряжения записывается два байта. В большинстве случаев в конвейере находится хотя бы одна команда, блок выполнения команд не ждет, пока очередная команда будет извлечена из памяти.

Коды команд поступают в блок выполнения команд последовательно, как они записаны в программе. Если выполняется команда передачи управления (безусловный переход, условный переход, вызов подпрограммы и т.п.), то блок сопряжения с шиной очищает конвейер команд, получает код команды из нового адреса и начинает заполнять конвейер заново. Если выполняется команда, требующая обращение к памяти или внешнему устройству, то блок сопряжения приостанавливает процесс получения команд в конвейер и организует необходимый процесс обмена данными.

Сегментные регистры используются при обращении к памяти для вычисления физических адресов ячеек и содержат информацию о начальных адресах сегментов:

регистр CS (Code Segment) определяет текущий программный сегмент;

регистр DS (Date Segment) – сегмент текущих данных;

регистр SS (Stack Segment) – текущий стековый сегмент;

регистр ES (Extra Segment) – дополнительный сегмент текущих данных.

Физический адрес представляется 20-разрядным числом и однозначно определяет любую из 1М ячеек памяти в диапазоне адресов 00000h –FFFFFh.

В силу того, что внутренние регистры микропроцессора имеют 16 разрядов, программы используют логический адрес. Он состоит из двух частей: значения базы сегмента и значения смещения в сегменте, которые выражаются 16-разрядными числами. Как только блок сопряжения с шиной обращается к памяти, физический адрес формируется исходя из следующего выражения:

ФА=БС*24+ЕА,

где ФА – физический адрес ячейки памяти,

БС – база сегмента,

ЕА – исполнительный адрес, или смещение в сегменте.

Иными словами, значение базы сегмента смещается на четыре разряда влево (см. рис. 2.4), и полученное 20-разрядное число (с четырьмя нулями в младших 4 разрядах) складывается со значением смещения в сегменте. Как следует из приведенного выражения, к одной и той же ячейке памяти можно обратиться, используя различные значения базы и смещения.

0000

База сегмента

0

+

Физический адрес

памяти

Смещение

(EA)

Рис. 2.4. Схема формирования физического адреса памяти

В зависимости от команд блок сопряжения с шиной получает информацию о логическом адресе памяти из различных регистров микропроцессора. Коды команд всегда извлекаются из памяти по адресу, определяемому содержимым регистра CS и регистра IP. Регистр IP содержит смещение в сегменте текущего кода (CS) и выполняет функции счетчика команд. Команды со стеком всегда используют регистры SS и SP. Данные или переменные в командах извлекаются из адресов памяти, расположенных в сегменте данных. Способ формирования исполнительного адреса определяется способом адресации. Регистр ES обычно применяется как вспомогательный сегмент данных.

Система прерываний. Микропроцессор имеет многоуровневую систему прерываний с векторным способом идентификации подпрограмм обслуживания прерываний. Микропроцессор обрабатывает до 256 видов прерываний, каждому из которых соответствует четырехбайтовый вектор прерывания, задающий начальный адрес подпрограммы обслуживания прерывания. Вектор прерывания включает два байта IP и два байта регистра CS. Для записи таблицы векторов прерываний резервируются ячейки памяти с адресами от 00000h до 003FFh. Векторы прерываний занимают 1К байт адресного пространства (см. рис. 2.5).

Номер вектора прерывания 0

Адрес памяти

CS 255

N=255

003FEh

IP 255

003FCh

CS 1

N=1

00006h

IP 1

00004h

CS 0

00002h

N=0

IP 0

00000h

0

15

Рис.2.5. Распределение векторов прерывания в памяти МП

Прерывания могут вызываться внешними и внутренними сигналами. Запросы внешних прерываний подаются на входы INT и NMI. Прерывания по входу INT относятся к аппаратным маскируемым прерываниям. Если сигнал на входе имеет высокий уровень и установлен флаг IF регистра состояний, то запрос принимается и начинается его обслуживание. Вход немаскируемого запроса прерывания NMI используется для сообщений о «катастрофических» событиях. Обработка немаскируемого запроса не зависит от состояния флага IF и ему присвоен номер вида прерывания N=2. К внутренним аппаратным прерываниям относятся прерывание по ошибке деления (N=0), прерывание пошагового режима (N=1), прерывание по переполнению (N=4).

Прямой доступ к памяти. Режим инициируется подачей на вход HLD микропроцессора единичного сигнала запроса. По завершению текущего машинного цикла микропроцессор выдает сигнал подтверждения захвата HLDA и переводит свои шины в третье состояние. Установка низкого уровня сигнала на входе HLD приводит к прекращению режима захвата и выполнению очередного машинного цикла.