- •А. В. Поздняков, б. Я. Цилькер микропроцессоры и микропроцессорные системы

- •Часть 1

- •(Учебное пособие)

- •Содержание

- •1. Микропроцессорные системы

- •1.1. Историческая справка

- •1.2. Архитектура мпс с магистрально-модульной организацией

- •1.3. Режимы работы мпс

- •2. Микропроцессорный модуль

- •2.1. Центральный процессор

- •2.1.1. Классификация микропроцессоров

- •2.1.2. Структура центрального процессора

- •2.1.2.1. Краткая характеристика микропроцессора Intel 8086

- •2.1.2.2. Архитектура микропроцессора Intel 8086

- •2.1.2.3. Программная модель микропроцессора Intel 8086

- •2.1.2.4. Представление информации в мп Intel 8086

- •2.1.2.5. Способы адресации операндов в мп Intel 8086

- •2.1.2.6. Система команд мп Intel 8086

- •2.1.2.7. Содержание цикла команды, типовые машинные циклы мп Intel 8086

- •2.1.2.8. Входные и выходные сигналы мп Intel 8086

- •2.2. Сопроцессор

- •2.3. Генератор тактовых импульсов

- •2.4. Системный контроллер

- •2.5. Согласующие элементы микропроцессорных систем

- •2.5.1. Шинные формирователи

- •2.5.2. Буферные регистры

- •2.6. Контроллер прерываний

- •2.7. Контроллер прямого доступа к памяти

- •2.8. Программируемый таймер

- •3. Модуль памяти

- •3.1. Организация модуля памяти

- •3.2. Распределение адресного пространства зу

- •3.3. Декодирование старших разрядов адреса.

- •3.3.1. Декодирование адресов методом линейной выборки

- •3.3.2. Декодирование адресов с помощью логических компараторов

- •3.3.3. Декодирование адресов с применением комбинационных логических схем

- •3.4. Выбор типа зу

- •3.5. Функциональная схема модуля памяти

- •3.6. Обеспечение необходимой емкости зу

- •3.6.1. Увеличение разрядности зу

- •3.6.2. Увеличение адресного пространства зу

- •4. Модуль ввода-вывода

- •4.1. Интерфейс ввода-вывода

- •4.2. Параллельные порты

- •4.2.1. Параллельный порт вывода

- •4.2.2. Параллельный порт ввода

- •4.2.3. Параллельные порты ввода-вывода

- •4.3. Последовательные порты

- •4.3.1. Последовательный асинхронный порт вывода

- •4.3.2. Последовательный асинхронный порт ввода

- •4.3.3. Программируемый последовательный интерфейс

- •4.4. Организация обращения к портам ввода/вывода

- •4.4.1. Обращение к портам ввода/вывода с помощью специальных команд

- •4.4.2. Обращение к портам ввода/вывода с помощью команд пересылок

- •4.5. Способы организации ввода/ вывода информации в мпс

- •4.5.1. Организация ввода/вывода информации под управлением основной программы

- •4.5.2. Организация ввода/вывода в режиме прерывания программы

- •4.5.3. Организация ввода/вывода в режиме прямого доступа к памяти

- •Система команд микропроцессора Intel 8086 Команды пересылки данных

- •Арифметические команды

- •Логические команды

- •Команды передачи управления

- •Команды управления процессором

- •Команды обработки строк

- •Литература

4.2. Параллельные порты

4.2.1. Параллельный порт вывода

Параллельный порт вывода, работающий в синхронном режиме, при реализации требует минимальных аппаратных затрат. На рис. 4.1 представлена функциональная схема такого порта. Порт включает в свой состав:

параллельный регистр DD1;

дешифратор адреса (номера) порта DD2;

формирователь сигнала записи в регистр DD3.

Р ис.

4.1. Функциональная схема синхронного

параллельного порта вывода

ис.

4.1. Функциональная схема синхронного

параллельного порта вывода

Разрядность регистра DD1 определяется разрядностью шины данных периферийного устройства. В регистре могут использоваться триггеры типа "защелка".

Д ешифратор адреса подключен к 8 младшим разрядам шины адреса. При наличии адреса порта (01h) и управляющего сигнала IOW на шине управления информация с шины данных МПС записывается в регистр и поступает на периферийное устройство.

4.2.2. Параллельный порт ввода

Параллельный порт ввода, работающий в синхронном режиме, имеет в своем составе те же функциональные узлы, что и порт вывода. Но поскольку выходы регистра должны подключаться к шине данных МПС, необходимо использовать регистр, выходы которого имеют Z-состояние или реализованы по схеме с открытым коллектором. На рис. 4.2. приведена функциональная схема параллельного синхронного порта ввода.

П ри наличии на шине адреса кода 02h и управляющего сигнала IOR, информация записывается в регистр DD1 и выдается на шину данных. Снятие сигнала IOR переводит выходы регистра DD1 в Z-состояние и шина данных МПС освобождается.

Р ис.

4.2. Функциональная схема синхронного

параллельного порта ввода

ис.

4.2. Функциональная схема синхронного

параллельного порта ввода

4.2.3. Параллельные порты ввода-вывода

В составе МПК имеются микросхемы, которые путем предварительного программирования могут быть настроены на ввод или вывод информации в параллельном коде в синхронном и асинхронном режимах. Примером микросхем данного типа может служить микросхема I8255 (КР580ВВ55) "Параллельный программируемый интерфейс" [АЛЕК84, ХВОЩ87].

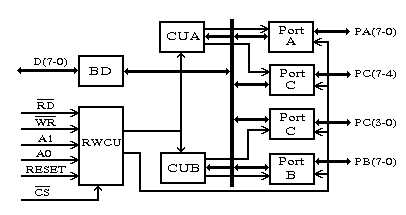

Микросхема позволяет осуществить обмен 8-разрядными данными по трем каналам. Направление обмена и режимы работы для каждого канала задаются программно. Структурная схема I8255 представлена на рис. 4.3.

Р ис.

4.3. Структурная схема микросхемы I8255

"Программируемый параллельный

интерфейс

ис.

4.3. Структурная схема микросхемы I8255

"Программируемый параллельный

интерфейс

В состав микросхемы входят:

двунаправленный 8-разрядный буфер данных (BD), связывающий микросхему с системной шиной данных;

блок управления записью/чтением (RWCU), обеспечивающий управление передачей информации как внутри микросхемы, так и между микросхемой и внешними устройствами;

три 8-разрядных канала ввода/вывода (Port A, Port B, Port C) для обмена информацией с внешними устройствами;

схема управления группой А (CUA), вырабатывающая сигналы управления каналом A и старшими разрядами канала C (PC[7-4]);

схема управления группой B (CUB), вырабатывающая сигналы управления каналом B и младшими разрядами канала C (PC[3-0]).

О бмен информацией между шиной данных МПС и микросхемой осуществляется через двунаправленную шину D7-0 и буфер данных, при наличии определенных сигналов на адресных входах (A1,A0), сигнала чтения (RD), сигнала записи (WR) и сигнала выбора микросхемы (CS).

Доступ к каналу A обеспечивается при наличии на входах A1, A2 адреса 00b, к каналу B – адреса 01b, а к каналу C – адреса 10b.

Сигналом, подаваемым на вход RESET, все каналы устанавливаются в нулевое состояние и переводятся в режим ввода.

Перед началом работы необходимо запрограммировать интерфейс: задать для каждого канала направление передачи информации и режим работы. Это обеспечивается путем записи определенной кодовой комбинации в регистр управляющего слова (РУС), который на структурной схеме не показан. Регистр РУС имеет адрес 11b и доступен только для записи.

Микросхема позволяет реализовать три режима обмена информацией:

синхронный режим (Режим 0);

асинхронный (стробируемый) однонаправленный режим (Режим 1);

асинхронный двунаправленный режим (Режим 2).

Канал A может работать в любом из трех режимах, канал B – режимах 0 и 1. Канал С может быть использован для передачи данных только в режиме 0. Режим 0 задается для каналов C7–C4 и C3–C0 нулевым режимом той группы, в которую данный канал входит. В остальных режимах канал C используется для передачи и формирования управляющих сигналов, сопровождающих асинхронный обмен по каналам A и B. Каналы одновременно могут работать в различных режимах. При изменении режима канала все его разряды устанавливаются в нулевое состояние.

Структура управляющего слова обеспечивающего задание режимов работы каналов и направление передачи информации представлена на рис. 4.4.

Рис. 4.4. Структура управляющего слова обеспечивающего задание режимов работы каналов и направление передачи информации в микросхеме I8255

Р ежим 0 – основной режим работы интерфейса, используется при организации синхронного обмена информацией между микропроцессором и внешними устройствами. При выводе информации по сигналу WR, данные находящиеся на ШД, запоминаются в буферном регистре соответствующего канала и сразу же передаются на его выход. При вводе информации данные с каналов A,B,C записываются в буферные регистры этих каналов без стробирования и при поступлении сигнала RD информация выбранного канала передается на ШД.

Режим 1 – обеспечивает возможность организации однонаправленной асинхронной передачи информации по каналам A и B. Канал C(7-4), в этом случае, используется для приема и формирования трех управляющих сигналов сопровождающих асинхронный обмен по каналу A, а канал C(3-0) – трех управляющих сигналов сопровождающих асинхронный обмен по каналу B.

При асинхронном обмене информации используется работа микропроцессора в режиме прерывания.

Режим 2 – обеспечивает двунаправленный асинхронный обмен информации по каналу A. Процесс обмена сопровождают пять управляющих сигналов, подаваемых по линиям С(7-3) канала C.

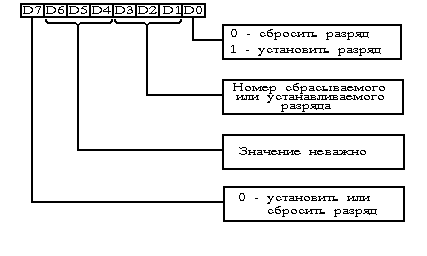

Регистр управляющего слова позволяет также произвести установку или сброс отдельных разрядов канала С. Структура управляющего слова позволяющего реализовать это представлена на рис. 4.5.

В микроконтроллерах параллельные порты ввода-вывода реализованы на том же кристалле, что и процессор. Причем линии портов могут индивидуально настраиваться или на ввод, или на вывод информации.

Р ис.

4.5. Структура управляющего слова

позволяющего произвести

установку

или сброс отдельных разрядов канала С

ис.

4.5. Структура управляющего слова

позволяющего произвести

установку

или сброс отдельных разрядов канала С