- •А. В. Поздняков, б. Я. Цилькер микропроцессоры и микропроцессорные системы

- •Часть 1

- •(Учебное пособие)

- •Содержание

- •1. Микропроцессорные системы

- •1.1. Историческая справка

- •1.2. Архитектура мпс с магистрально-модульной организацией

- •1.3. Режимы работы мпс

- •2. Микропроцессорный модуль

- •2.1. Центральный процессор

- •2.1.1. Классификация микропроцессоров

- •2.1.2. Структура центрального процессора

- •2.1.2.1. Краткая характеристика микропроцессора Intel 8086

- •2.1.2.2. Архитектура микропроцессора Intel 8086

- •2.1.2.3. Программная модель микропроцессора Intel 8086

- •2.1.2.4. Представление информации в мп Intel 8086

- •2.1.2.5. Способы адресации операндов в мп Intel 8086

- •2.1.2.6. Система команд мп Intel 8086

- •2.1.2.7. Содержание цикла команды, типовые машинные циклы мп Intel 8086

- •2.1.2.8. Входные и выходные сигналы мп Intel 8086

- •2.2. Сопроцессор

- •2.3. Генератор тактовых импульсов

- •2.4. Системный контроллер

- •2.5. Согласующие элементы микропроцессорных систем

- •2.5.1. Шинные формирователи

- •2.5.2. Буферные регистры

- •2.6. Контроллер прерываний

- •2.7. Контроллер прямого доступа к памяти

- •2.8. Программируемый таймер

- •3. Модуль памяти

- •3.1. Организация модуля памяти

- •3.2. Распределение адресного пространства зу

- •3.3. Декодирование старших разрядов адреса.

- •3.3.1. Декодирование адресов методом линейной выборки

- •3.3.2. Декодирование адресов с помощью логических компараторов

- •3.3.3. Декодирование адресов с применением комбинационных логических схем

- •3.4. Выбор типа зу

- •3.5. Функциональная схема модуля памяти

- •3.6. Обеспечение необходимой емкости зу

- •3.6.1. Увеличение разрядности зу

- •3.6.2. Увеличение адресного пространства зу

- •4. Модуль ввода-вывода

- •4.1. Интерфейс ввода-вывода

- •4.2. Параллельные порты

- •4.2.1. Параллельный порт вывода

- •4.2.2. Параллельный порт ввода

- •4.2.3. Параллельные порты ввода-вывода

- •4.3. Последовательные порты

- •4.3.1. Последовательный асинхронный порт вывода

- •4.3.2. Последовательный асинхронный порт ввода

- •4.3.3. Программируемый последовательный интерфейс

- •4.4. Организация обращения к портам ввода/вывода

- •4.4.1. Обращение к портам ввода/вывода с помощью специальных команд

- •4.4.2. Обращение к портам ввода/вывода с помощью команд пересылок

- •4.5. Способы организации ввода/ вывода информации в мпс

- •4.5.1. Организация ввода/вывода информации под управлением основной программы

- •4.5.2. Организация ввода/вывода в режиме прерывания программы

- •4.5.3. Организация ввода/вывода в режиме прямого доступа к памяти

- •Система команд микропроцессора Intel 8086 Команды пересылки данных

- •Арифметические команды

- •Логические команды

- •Команды передачи управления

- •Команды управления процессором

- •Команды обработки строк

- •Литература

2.7. Контроллер прямого доступа к памяти

Режим прямого доступа к памяти используется в МПС для быстрого обмена массивами данных между ЗУ и периферийным устройством. При работе в этом режиме МП отключается от шин адреса, данных и частично от шины управления, а функции работы с памятью и периферийным устройством берет на себя специальная ИМС контроллера прямого доступа к памяти (КПДП).

Основное назначение контроллера – формирование в процессе обмена между ЗУ и периферийным устройством последовательности адресов ЗУ, а также сигналов управления обменом и процессом прямого доступа к памяти.

КПДП может иметь несколько независимых каналов, связанных с отдельными источниками запроса на прямой доступ к памяти. Каждому из каналов присваивается определенный уровень приоритета. В КПДП может использоваться как фиксированный, так и циклический приоритет запросов прямого доступа к памяти. Каждый канал включает регистр адреса и регистр-счетчик. В регистр адреса заносится начальный адрес ЗУ для передаваемого массива данных. В регистр-счетчик помещается число, соответствующее длине передаваемого массива, а также информация о направлении передачи данных (из ЗУ в периферийное устройство или наоборот). Запись информации в регистр начального адреса и регистр-счетчик осуществляется микропроцессором и носит название инициализации КПДП. При наличии сигналов запроса от периферийных устройств на прямой доступ к памяти (DRQx) КПДП выдает сигнал запроса захвата HRQ, который поступает на вход HLD микропроцессора. При поступлении от МП сигнала подтверждения захвата HLDA КПДП формирует для периферийного устройства, запросившего прямой доступ к памяти и имеющего наивысший приоритет, сигнал подтверждения прямого доступа к памяти DACKx (direct-memory-access acknowledge). Получив доступ к памяти, контроллер выставляет на шину адреса адрес ЗУ, хранящийся в регистре адреса канала, и формирует, в зависимости от направления передачи информации, пару управляющих сигналов: “Чтение УВВ” – ”Запись ЗУ” или “Чтение ЗУ” – “Запись УВВ”. После записи или чтения одного слова, содержимое регистра адреса увеличивается на единицу, а содержимое регистра-счетчика уменьшается на единицу. Процедура будет повторяться до тех пор, пока содержимое регистра-счетчика регистра не станет равным нулю. В этом случае контроллер снимает сигнал подтверждения прямого доступа к памяти DACKx. В ответ на это периферийное устройство снимает сигнал запроса на прямой доступ к памяти DRQx с контроллера, а контроллер, в свою очередь, снимает сигнал запроса захвата с вывода HLD микропроцессора и процедура прямого доступа к памяти завершается.

Примером КПДП может служить микросхема I8257, которая имеет 4 независимых канала обмена, каждый из которых обеспечивает передачу блока данных размером до 16 Кбайт c произвольным начальным адресом в диапазоне от 0 до 64 Кбайт [АЛЕК84].

2.8. Программируемый таймер

Программируемый таймер предназначен для задания временных интервалов в МПС и может использоваться как счетчик внешних событий. Основу таймера составляет один или несколько счетчиков, работающих на вычитание либо на суммирование. МП имеет возможность предварительной записи числа в счетчик и чтения его содержимого в произвольный момент времени. В режиме таймера на вход счетчика поступают импульсы тактового генератора, в режиме счетчика внешних событий – внешний сигнал. При обнулении или переполнении счетчика на выходе таймера формируется сигнал, который может быть использован в качестве сигнала запроса прерывания.

Примером таймера может служить микросхема I8253 [АЛЕК84, ХВОЩ87]. В состав микросхемы входят три 16-разрядных счетчика, образующие три независимых канала, имеющих стробирующие входы. Каждый канал может работать в одном из 6 режимов, задаваемых программно:

таймера;

одновибратора;

двух режимах делителя частоты;

двух режимах формирователя строба.

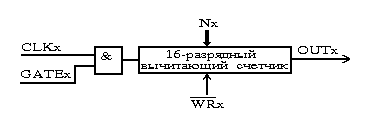

Упрощенная структура одного канала, без учета схемы управления режимами его работы, имеет вид представленный на рис. 2.24.

Диаграммы, поясняющие работу канала в разных режимах, приведены на рис. 2.25–2.28. Счет во всех режимах происходит при наличии сигнала логической единицы на входе GATEx.

Режим 0 (режим таймера). После занесения числа Nx в счетчик на выходе OUTx устанавливается ”0”. По окончании счета на выходе OUTx появляется ”1”.

Режим 1 (режим ждущего мультивибратора). С момента появления ”1” на входе GATEx на выходе OUTx формируется отрицательный импульс длительностью t*Nx.

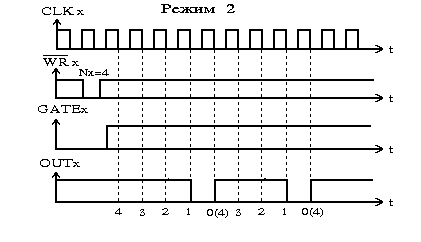

Режим 2 (режим делителя частоты). На выходе OUTx генерируется периодический сигнал c частотой в Nx раз меньше тактовой и длительностью t.

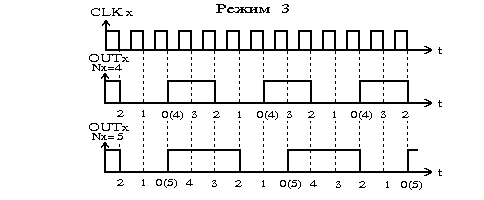

Режим 3 (режим делителя частоты). На выходе OUTx генерируется периодический сигнал c частотой в Nx раз меньше тактовой и длительностью t*Nx/2.

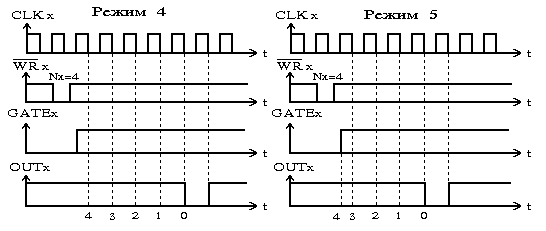

Режим 4 (режим формирователя строба). На выходе OUTx через время t*Nx после появления ”1” на входе GATEx формируется отрицательный импульс длительностью t. При исчезновении ”1” на входе GATEx счет задержки приостанавливается до ее восстановления.

Р ежим

5

(режим формирователя строба). На выходе

OUTx через время t*Nx

после появления ”1” на входе GATEx

формируется отрицательный импульс

длительностью t. При исчезновении”1”

на входе GATEx счет задержки прекращается

и начинается сначала после восстановления”1”

на входе GATEx.

ежим

5

(режим формирователя строба). На выходе

OUTx через время t*Nx

после появления ”1” на входе GATEx

формируется отрицательный импульс

длительностью t. При исчезновении”1”

на входе GATEx счет задержки прекращается

и начинается сначала после восстановления”1”

на входе GATEx.

Рис. 2.24. Упрощенная структура одного канала таймера I8253

Р ис.

2.25. Временные диаграммы работы таймера

I8253 в 0 и 1 режимах

ис.

2.25. Временные диаграммы работы таймера

I8253 в 0 и 1 режимах

Р

ис.

2.26. Временные диаграммы работы таймера

I8253 во 2 режиме

ис.

2.26. Временные диаграммы работы таймера

I8253 во 2 режиме

Рис. 2.27. Временные диаграммы работы таймера I8253 в 3 режиме

Р ис.

2.28. Временные диаграммы работы таймера

I8253 в 4 и 5 режимах

ис.

2.28. Временные диаграммы работы таймера

I8253 в 4 и 5 режимах