- •А. В. Поздняков, б. Я. Цилькер микропроцессоры и микропроцессорные системы

- •Часть 1

- •(Учебное пособие)

- •Содержание

- •1. Микропроцессорные системы

- •1.1. Историческая справка

- •1.2. Архитектура мпс с магистрально-модульной организацией

- •1.3. Режимы работы мпс

- •2. Микропроцессорный модуль

- •2.1. Центральный процессор

- •2.1.1. Классификация микропроцессоров

- •2.1.2. Структура центрального процессора

- •2.1.2.1. Краткая характеристика микропроцессора Intel 8086

- •2.1.2.2. Архитектура микропроцессора Intel 8086

- •2.1.2.3. Программная модель микропроцессора Intel 8086

- •2.1.2.4. Представление информации в мп Intel 8086

- •2.1.2.5. Способы адресации операндов в мп Intel 8086

- •2.1.2.6. Система команд мп Intel 8086

- •2.1.2.7. Содержание цикла команды, типовые машинные циклы мп Intel 8086

- •2.1.2.8. Входные и выходные сигналы мп Intel 8086

- •2.2. Сопроцессор

- •2.3. Генератор тактовых импульсов

- •2.4. Системный контроллер

- •2.5. Согласующие элементы микропроцессорных систем

- •2.5.1. Шинные формирователи

- •2.5.2. Буферные регистры

- •2.6. Контроллер прерываний

- •2.7. Контроллер прямого доступа к памяти

- •2.8. Программируемый таймер

- •3. Модуль памяти

- •3.1. Организация модуля памяти

- •3.2. Распределение адресного пространства зу

- •3.3. Декодирование старших разрядов адреса.

- •3.3.1. Декодирование адресов методом линейной выборки

- •3.3.2. Декодирование адресов с помощью логических компараторов

- •3.3.3. Декодирование адресов с применением комбинационных логических схем

- •3.4. Выбор типа зу

- •3.5. Функциональная схема модуля памяти

- •3.6. Обеспечение необходимой емкости зу

- •3.6.1. Увеличение разрядности зу

- •3.6.2. Увеличение адресного пространства зу

- •4. Модуль ввода-вывода

- •4.1. Интерфейс ввода-вывода

- •4.2. Параллельные порты

- •4.2.1. Параллельный порт вывода

- •4.2.2. Параллельный порт ввода

- •4.2.3. Параллельные порты ввода-вывода

- •4.3. Последовательные порты

- •4.3.1. Последовательный асинхронный порт вывода

- •4.3.2. Последовательный асинхронный порт ввода

- •4.3.3. Программируемый последовательный интерфейс

- •4.4. Организация обращения к портам ввода/вывода

- •4.4.1. Обращение к портам ввода/вывода с помощью специальных команд

- •4.4.2. Обращение к портам ввода/вывода с помощью команд пересылок

- •4.5. Способы организации ввода/ вывода информации в мпс

- •4.5.1. Организация ввода/вывода информации под управлением основной программы

- •4.5.2. Организация ввода/вывода в режиме прерывания программы

- •4.5.3. Организация ввода/вывода в режиме прямого доступа к памяти

- •Система команд микропроцессора Intel 8086 Команды пересылки данных

- •Арифметические команды

- •Логические команды

- •Команды передачи управления

- •Команды управления процессором

- •Команды обработки строк

- •Литература

2.4. Системный контроллер

Системный контроллер предназначен для формирования сигналов управления памятью, УВВ и другими устройствами, входящими в состав МПС.

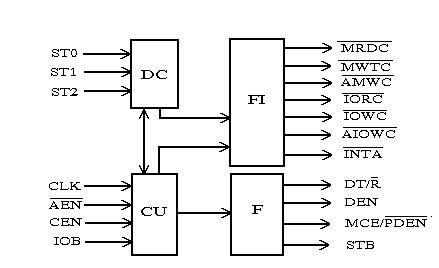

На рис. 2.20 приведена структурная схема системного контроллера I8288, который носит название "Контроллер шин" [ХВОЩ87]. Контроллер используется совместно с микропроцессором Intel 8086 при его работе в режиме максимальной конфигурации.

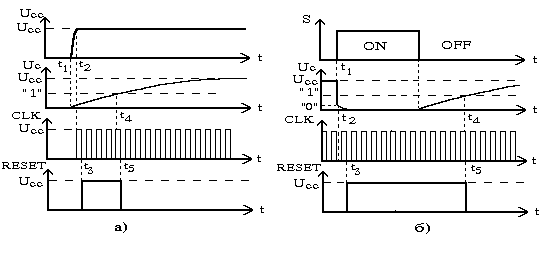

Р ис.

2.19. Временные диаграммы формирования

сигнала RESET:

ис.

2.19. Временные диаграммы формирования

сигнала RESET:

а) при включении питания; б) при нажатии кнопки S

Контроллер включает в себя:

дешифратор состояния (DC);

схему управления (CU);

формирователь командных сигналов (FI);

ф

ормирователь

управляющих сигналов (F).

ормирователь

управляющих сигналов (F).

Рис. 2.20. Структурная схема контроллера шин I8288

Контроллер обеспечивает, в соответствии с выполняемым МП машинным циклом, формирование командных сигналов:

ч

тения

из памяти MRDC;

тения

из памяти MRDC;з

аписи

в память MWTC, AMWC;

аписи

в память MWTC, AMWC;ч

тения

из УВВ IORC;

тения

из УВВ IORC;з

аписи

в УВВ IOWC, AIOWC;

аписи

в УВВ IOWC, AIOWC;п

одтверждения

прерывания INTA.

одтверждения

прерывания INTA.

С игналы AMWC и AIOWC называются сигналами записи с упреждением поскольку формируются на такт раньше соответственно сигналов MWTC и IOWC.

Контроллер обеспечивает формирование также управляющих сигналов:

D

T/R

– задающего направление передачи

информации через приемопередатчики

(”1” при записи и “0” при чтении);

T/R

– задающего направление передачи

информации через приемопередатчики

(”1” при записи и “0” при чтении);DEN – разрешения передачи данных, используемый для отпирания приемопередатчиков;

M

CE/PDEN

– выполняющего две функции: при входном

сигнале IOB=0 сигнал MCE служит для считывания

адреса из имеющего наивысший приоритет

контроллера прерываний, а при IOB=1 сигнал

PDEN разрешает работу приемопередатчиков

канала данных в процессе ввода-вывода;

CE/PDEN

– выполняющего две функции: при входном

сигнале IOB=0 сигнал MCE служит для считывания

адреса из имеющего наивысший приоритет

контроллера прерываний, а при IOB=1 сигнал

PDEN разрешает работу приемопередатчиков

канала данных в процессе ввода-вывода;STB – сигнала стробирования адреса.

Командные сигналы и сигналы управления формируются с помощью логических элементов, которые реализуют определенные логические функции. В качестве аргументов используются выходные сигналы МП и сигналы, поступающие от других устройств МПС.

Входными сигналами для контроллера являются:

сигналы состояния микропроцессора ST0, ST1, ST2;

сигнал от генератора тактовых импульсов CLK;

с

игнал

разрешения адресации AEN, открывающий

командные выходы при AEN=0 и переводящий

их в высокоимпедансное состояние при

AEN=1;

игнал

разрешения адресации AEN, открывающий

командные выходы при AEN=0 и переводящий

их в высокоимпедансное состояние при

AEN=1;сигнал разрешения команды CEN, открывающий командные выходы и управляющие выходы DEN и PDEN при CEN=1 и переводящий их в пассивное состояние при CEN=0;

сигнал режима управления каналом IOB; при IOB=1 устанавливается режим управления каналом ввода-вывода, а при IOB=0 – режим управления системным каналом.

При работе МП INTEL 8086 в режиме минимальной конфигурации необходимые командные и управляющие сигналы формируются непосредственно на выводах микропроцессора.

В современных микроконтроллерах системный контроллер реализуется на том же кристалле, что и процессор. В этом случае, на выходах микроконтроллера имеются управляющие сигналы, которые и образуют шину управления.

2.5. Согласующие элементы микропроцессорных систем

При создании МПС обычно приходится подключать к шинам МП значительное количество самых разнообразных устройств. Такое подключение сопряжено с необходимостью разрешения следующих проблем:

шины адреса, данных и управления МП допускают потребление относительно небольшого тока подключенными к ним устройствами, т. е. обладают невысокой нагрузочной способностью;

в ряде случаев, например, при прямом доступе к памяти, требуется отключение устройств, не участвующих в этом процессе, в том числе и самого МП от шин МПС, что обеспечивается переводом выходов таких устройств в высокоимпедансное состояние (Z-состояние). Возможность временного отключения от шин выгодно использовать и для снижения нагрузки на шинах, организовав МПС так, что в каждый конкретный момент к шинам подключены лишь необходимые для данной операции микросхемы, а выходы остальных находятся в Z-состоянии. Однако не все микросхемы, подключаемые к шинам МПС, обладают возможностью перевода своих выходов в Z-состояние;

логика совместной работы МП и ряда устройств МПС предполагает буферизацию (временное хранение) определенной информации, что многими устройствами непосредственно не обеспечивается;

некоторые устройства МПС рассчитаны на прием и выдачу информации в инверсном коде, что требует соответствующего преобразования при ее передаче.

Решение всех этих проблем в МПС обычно возлагается на согласующие микросхемы, к которым относятся шинные формирователи и буферные регистры.