Курсовой проект / Пункт 2

.doc2. Анализ схемотехнических решений проектируемого узла

Регистры - это устройства, выполняющие функции приема, хранения и передачи информации в виде т-разрядного двоичного кода, каждому разряду которого соответствует свой элемент памяти (разряд регистра), выполненный на основе триггеров RS-, JK-, или D-типа.

Основным классификационным признаком регистров являются способ записи двоичного кода в регистр и его выдача, т.е. различают параллельные, последовательные (сдвигающие) и параллельно-последовательные регистры. Параллельный регистр выполняет операцию записи параллельным кодом. Последовательный регистр осуществляет запись последовательным кодом, начиная с младшего или старшего разряда, путем последовательного сдвига кода тактирующими импульсами. Параллельно-последовательные регистры имеют входы, как для параллельной, так и для последовательной записи кода числа. Кроме того, сдвигающие регистры делятся на одно- и двунаправленные (реверсивные). Однонаправленные регистры осуществляют сдвиг кода влево или вправо, а двунаправленные - и влево, и вправо.

По способу ввода-вывода информации различают параллельные, последовательные и параллельно-последовательные регистры. В регистрах памяти ввод и вывод информации осуществляются в параллельном коде. При этом время ввода (вывода) всего числа равно времени ввода (вывода) одного разряда. В регистрах сдвига число вводится и выводится последовательно разряд за разрядом. Время ввода (вывода) m-разрядного двоичного числа в таких регистрах определяется величиной mTc, где Tc - период следования тактовых импульсов, осуществляющих ввод (вывод) информации. В параллельно-последовательном регистре ввод числа может осуществляться в параллельном коде, а вывод - в последовательном или наоборот.

По характеру представления вводимой и выводимой информации различают регистры однофазного и парафазного типов. В однофазных регистрах информация вводится в прямом либо в обратном кодах, а в парафазных - одновременно и прямом и в обратном. Регистры первого типа строятся на основе D-триггеров, второго - на основе RS- или JK-триггеров. Вывод информации из регистров обоих типов может осуществляться в прямом и в обратном кодах.

Принцип построения простейшего параллельного Т-разрядного регистра показан на рисунке ниже.

В параллельном регистре цифры кода подаются на D-вход соответствующих триггеров. Запись осуществляется при подаче логической единицы на вход С. Код снимается с выходов Q. Параллельные регистры служат только для хранения информации в виде параллельного двоичного кода и для преобразования прямого кода в обратный и наоборот.

Последовательные регистры, помимо хранения информации, способны преобразовывать последовательный код в параллельный и наоборот. При построении последовательных регистров триггеры соединяются последовательно путем подключения выхода Qi-го триггера ко входу Di-го триггера, как это показано на рисунке ниже.

В

последовательных регистрах принципиально

необходимо, чтобы новый сигнал на выходе

Qш-го триггера возникал только после

окончания синхросигнала. Для выполнения

этого условия в последовательных

регистрах необходимо применять

двухступенчатые триггеры.

В

последовательных регистрах принципиально

необходимо, чтобы новый сигнал на выходе

Qш-го триггера возникал только после

окончания синхросигнала. Для выполнения

этого условия в последовательных

регистрах необходимо применять

двухступенчатые триггеры.

При действии каждого очередного тактового импульса код, содержащийся в регистре, сдвигается на один разряд. Для схемы, приведенной на рисунке выше, сдвиг кода происходит вправо (в сторону младших разрядов). Действительно, сигнал выхода Qi+1-го триггера действует на вход Di-го триггера, а сигнал выхода Qi-го триггера действует на вход Di-1-го триггера. При действии синхросигнала i-й триггер примет состояние i+1-го, а i-1-й - состояние i-го триггера, т.е., произойдет сдвиг кода вправо на один разряд.

Параллельный двоичный код одновременно снимается с выходов Q триггеров. Для сдвига кода влево необходимо, чтобы сигнал с выхода Qi-1-го триггера подавался на вход Qi-го (старшего) триггера.

Для преобразования параллельного кода информации в последовательный может быть использован любой универсальный регистр сдвига, например ИР11.

|

|

Здесь: C - вход синронизации, R - вход сброса, DR, DL - входы последовательного сдвига вправо и влево, S0,S1 - входы установки режима, D - 1,2,4,8 - информационные входы, Q - 1,2,4,8 - информационные выходы.

|

Если, например, в регистре записано число 0101 и линия связи соединена с выходом D8, то в этом случае необходимо для преобразования параллельной формы числа 0101 в последовательную сдвигать биты этого числа влево, а если смотреть на условное графическое обозначение микросхемы, то сдвигать биты нужно от разряда единиц к разряду восьмерок, что и означает при записи этого числа в строке сдвиг влево. Режим сдвига влево реализуется при S1=1, S0=0. Сдвиг происходит синхронно с приходом фронта тактового импульса. Порядок построения диаграммы сдвига для пяти тактовых импульсов показан на рисунках 1-6.

На рисунке 6 можно увидеть преобразованное число 0101 в последовательной форме, если посмотреть на диаграмму выхода D8 (последняя строка диаграмм).

Если линия связи будет соединена с выходом D1 (это разряд единиц), то алгоритм построения диаграммы сдвига будет аналогичен приведенному выше, с той лишь разницей, что число в последовательной форме после 5-го тактового импульса будет находиться на диаграмме выхода D1. И соответственно сдвиг нужно будет производить не влево, а вправо.

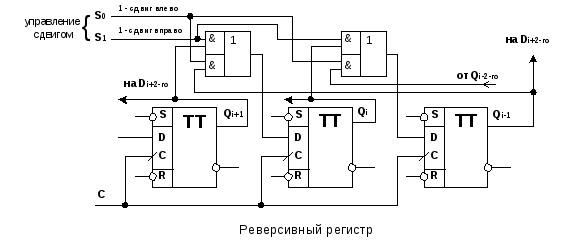

Реверсивные регистры должны содержать логические схемы управления, обеспечивающие прохождение сигнала с выхода Qi-го триггера на вход Di-1-го триггера при сдвиге кода вправо и прохождение этого же сигнала на вход Di+1-го при реализации сдвига кода влево. Схема построения реверсивного регистра приведена на рисунке ниже.

Направление

сдвига кода определяется подачей

требуемых сигналов управления на

соответствующие входы. Так, в схеме,

показанной на рисунке выше, при подаче

на вход S0 напряжения логической единицы

сдвиг кода будет происходить влево (в

сторону старших разрядов), поскольку

логическая схема управления 2И - 2И - 2ИЛИ

будет разрешать прохождение сигналов

с выходов Qi-го триггера на вход Di-го

триггера, и наоборот, при подаче на вход

S1 напряжения логической единицы будет

разрешено прохождение сигнала с выхода

Qi-го триггера на вход Di1-го триггера -

будет реализовываться сдвиг кода вправо

(в сторону младших разрядов).

Направление

сдвига кода определяется подачей

требуемых сигналов управления на

соответствующие входы. Так, в схеме,

показанной на рисунке выше, при подаче

на вход S0 напряжения логической единицы

сдвиг кода будет происходить влево (в

сторону старших разрядов), поскольку

логическая схема управления 2И - 2И - 2ИЛИ

будет разрешать прохождение сигналов

с выходов Qi-го триггера на вход Di-го

триггера, и наоборот, при подаче на вход

S1 напряжения логической единицы будет

разрешено прохождение сигнала с выхода

Qi-го триггера на вход Di1-го триггера -

будет реализовываться сдвиг кода вправо

(в сторону младших разрядов).

Примеры условного графического обозначения параллельного, сдвигового и реверсивного регистров приведено на рисунке ниже.

Выводы микросхем, показанных на рисунке выше, следующие: D1-Dn - входы D-триггеров соответствующих разрядов при записи информации в параллельном коде; Q1-Qn - прямые выходы Q-триггеров; С - вход тактовых импульсов; R - вход обнуления; S0,S1 - входы управления направлением сдвига; VR - вход последовательного кода при сдвиге вправо (R - от англ. Right), при сдвиге кода влево применяется обозначение VL - (Left).

Основную массу регистров, применяемых на практике, представляют регистры сдвига, т.к. помимо операции хранения они могут осуществлять преобразование параллельного кода в последовательный и наоборот, прямого кода - в обратный и наоборот, выполнять арифметические и логические операции, временную задержку и деление частоты.

Иногда объединяют два понятия логический и циклический сдвиг. Рассмотрим логический (циклический) сдвиг на трех разрядном регистре состоящем из RS-триггеров. Под логическим сдвигом понимают – на освободившееся место записывается 0. Под циклическим сдвигом понимают – на освободившееся место записывается буква, выпадавшая при переносе слова.

Пусть исходным состоянием будет 010 и зададим логический сдвиг вправо на один разряд. Можно записать и по другому: (RG)0 = 010, ЛП1.

Составим таблицу переходов для регистра:

|

Старое состояние |

Новое состояние |

||||

|

Q1 |

Q2 |

Q3 |

Q1t |

Q2t |

Q3t |

|

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

0 |

|

0 |

1 |

0 |

0 |

0 |

1 |

|

0 |

1 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

0 |

1 |

0 |

|

1 |

0 |

1 |

1 |

1 |

0 |

|

1 |

1 |

0 |

0 |

1 |

1 |

|

1 |

1 |

1 |

1 |

1 |

1 |

Теперь составим временную диаграмму, по которой видно как работает регистр.

После третьего синхросигнала видно, что выходной сигнал начинает повторяться, т.е. зацикливается.

А теперь рассмотрим арифметический сдвиг. Под ним понимают – на освободившееся место записывается содержимое бита переноса.

Пусть исходным состоянием будет 010 и зададим арифметический сдвиг вправо на один разряд. Можно записать и по другому: (RG)0 = 010, АП1.

Составим таблицу переходов для регистра:

|

Старое состояние |

Новое состояние |

||||

|

Q1 |

Q2 |

Q3 |

Q1t |

Q2t |

Q3t |

|

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

0 |

0 |

|

0 |

1 |

0 |

0 |

0 |

1 |

|

0 |

1 |

1 |

0 |

0 |

1 |

|

1 |

0 |

0 |

1 |

1 |

0 |

|

1 |

0 |

1 |

1 |

1 |

0 |

|

1 |

1 |

0 |

1 |

1 |

1 |

|

1 |

1 |

1 |

1 |

1 |

1 |

Также и для арифметического сдвига составим временную диаграмму, по которой видно как работает регистр.

Далее рассмотрим параллельный парафазный Т-разрядный регистр. Схему регистра построим на асинхронных RS–триггерах.

Информация в регистрах данного типа заносится по линиям a1, a2,..., an только при подаче активного сигнала на вход "Прием информации". Записанный код числа будет храниться в регистре до тех пор, пока не будет сброса регистра или записи новой информации. Регистр позволяет выдавать данные в прямом коде, инверсном и парафазном коде.

В итоге регистр имеет несколько режимов работы: установка нуля (сброс), прием информации, выдача информации в прямом и инверсном коде, а также выдача информации в парафазном коде, т.е. выдается прямое значение и инверсное.

Что касается микроопераций, выполняемых регистрами, то современные регистры мало приспособлены для выполнения этих операций, однако при необходимости их можно выполнить, пользуясь регистрами на RS-триггерах. Для выполнения операции «ИЛИ» на S-входы статического регистра с исходным нулевым состояниям подается первое слово «А», единичные разряды которого устанавливают соответствующие триггеры. Затем без сброса регистра на S-выходы подается второе слово «В». В результате получим результат Q=A V B.

При выполнении поразрядной операции «И» в первом такте на S-входы регистра подается слово «А», устанавливающее те разряды регистра, в которых слово «А» имеет единицы. Затем следует подать на регистр слово «В». Чтобы в регистре сохранились единицы только в тех разрядах, в которых единицы имеют оба слова, слово «В» подается на входы R-триггеров в инверсном виде.

Сложение по модулю 2 может быть выполнено схемой с триггерами типа «Т» в разрядах путем последовательной во времени подачи на неё двух слов «А» и «В».

Исходя из анализа схемотехнического решения курсового проекта, приступим к реализации главного задания курсового проекта – универсальный регистр.

2.1. Разработка структурной схемы

2.2. Разработка функциональной схемы

При разработке функциональной схемы универсального регистра будем отталкиваться от построения ее готовых интегральных микросхемах. Универсальный реверсивный сдвиговый регистр ИР11 удовлетворяет требованиям задания. Он реализует следующие режимы работы, а именно: хранение четырехразрядного кода, сдвиг кода влево, сдвиг кода вправо, параллельный и последовательный ввод и вывод кода. Режимы работы задаются двухразрядным кодом, подаваемым на входы управления S0,S1. Режимы работы регистра при определенных значениях сигналов на входах S0,S1 обозначены в таблице ниже.

|

S0 |

S1 |

Режим |

|

0 |

0 |

Хранение |

|

0 |

1 |

Сдвиг влево |

|

1 |

0 |

Сдвиг вправо |

|

1 |

1 |

Параллельный ввод |

При подаче логического «0» на вход R происходит установка триггеров регистра в 0. При подаче логической «1» на входе R режим работы определяется управляющими сигналами на входах S0 и S1. При логической «1» на входе S0 и логического «0» на входе S1 по спадам импульсов отрицательной полярности на входе С происходит последовательный прием информации с входа DR и сдвиг вправо. При подаче логической «1» на входе S1 и логического «0» на входе S1 происходит последовательный прием информации с входа DL и сдвиг влево.

При логической «1» на обоих входа S0 и S1 по спаду импульса отрицательной полярности на входе С произойдет параллельная запись информации со входов A, B, C, D. Если на входах S0 и S1 логический «0», переключение триггеров регистра при изменении информации на входе С не происходит.

Полная таблица истинности регистра ИР11:

|

Режим работы |

Вход |

Выход |

||||||||||||

|

R |

Режим работы |

C |

DL

|

D R |

Параллельная запись |

QA |

QB |

QC |

QD |

|||||

|

S1 |

S0 |

A |

B |

C |

D |

|||||||||

|

Установка “0” |

0 |

X |

X |

X |

X |

X |

X |

X |

X |

X |

0 |

0 |

0 |

0 |

|

Хранение |

1 |

X |

X |

0 |

X |

X |

X |

X |

X |

X |

QA0 |

QB0 |

QC0 |

QD0 |

|

|

1 |

1 |

1 |

|

X |

X |

A |

B |

C |

D |

A |

B |

C |

D |

|

|

1 1 |

0 0 |

1 1 |

|

X X |

0 1 |

X X |

X X |

X X |

X X |

0 1 |

QAn QAn |

QBn QBn |

QCn QCn |

|

|

1 1 |

1 1 |

0 0 |

|

0 1 |

X X |

X X |

X X |

X X |

X X |

QBn QBn |

QCn QCn |

QDn QDn |

0 1 |

|

Хранение |

1 |

0 |

0 |

X |

X |

X |

X |

X |

X |

X |

QA0 |

QB0 |

QC0 |

QD0 |

Ниже представлена функциональная схема универсально 8-ми разрядного регистра соединенного из двух 4х разрядных регистров ИР11.

Параллельная

запись

Параллельная

запись

Сдвиг

вправо

Сдвиг

вправо

Сдвиг

влево

Сдвиг

влево