- •Мови, рівні і віртуальні машини

- •Сучасні багаторівневі машини

- •Поняття архітектури пк

- •1.4. Розвиток комп’ютерної архітектури

- •Розвиток багаторівневих машин

- •Типи сучасних еом

- •Питання до лекції

- •2.1. Принципи розробки сучасних комп'ютерів

- •2.2. Паралелізм на рівні команд

- •2.3. Конвеєри

- •2.4. Суперскалярні архітектури

- •2.5. Паралелізм на рівні процесорів

- •2.6. Векторні комп'ютери

- •Блок управління

- •2.7. Мультипроцессори

- •2.8. Мультикомпьютери

- •Питання до лекції

- •3. Основи комп’ютерної організації : пам’ять

- •3.1. Ієрархічна структура пам'яті

- •3.2. Загальні відомості про пам'ять

- •3.4. Методи звертання до пам'яті

- •3.5. Модулі пам'яті

- •3.6. Ряди і банки пам'яті

- •3.8. Код з виправленням помилок

- •3. 9. Скільки потрібно пам'яті

- •Питання до лекції

- •4. Цифровий рівень побудови ом

- •4.1. Вентилі і булева алгебра

- •4.2. Булева алгебра

- •4.3. Реалізація булевих функцій

- •4.4. Еквівалентність схем

- •Основні цифрові логічні схеми Інтегральні схеми

- •4.5. Комбінаційні схеми

- •3 Входи і 8 виходів

- •4.6. Арифметичні схеми.

- •4.7. Тактові генератори

- •Питання до лекції

- •Цифровий рівень побудови ом.

- •5. Цифровий логічний рівень архітектури: пам’ять, мікропроцесори

- •5.2. Синхронні sr-защіпки

- •5.3. Синхронні d-защіпки

- •5.4. Тригери (flip-flops)

- •5.5. Регістри

- •5.6. Організація пам'яті

- •Тригер (б)

- •Кожний ряд представляє одне з 3-бітних слів. При операції зчитування і запису завжди зчитується або записується ціле слово

- •5.7. Мікросхеми пам'яті

- •5.9. Мікросхеми процесорів

- •Стрілочки указують вхідні і вихідні сигнали. Короткі діагональні лінії вказують на наявність декількох висновків.

- •Питання до лекції

- •6. Шини

- •6.1. Ширина шини

- •6.2. Синхронізація шини

- •6.3. Синхронні шини

- •6.5. Асинхронні шини

- •6.6. Арбітраж шини

- •6.7. Принципи роботи шини

- •Питання до лекції

- •7. Мікроархітектурний рівень

- •7.1. Приклад мікроархітектури

- •7.2. Тракт даних

- •В цьому розділі

- •Табліця 7.1. Деякі комбінації сигналів аллу і відповідні їм функції

- •7.3. Синхронізація тракту даних

- •7.4. Робота пам'яті.

- •7.5. Мікрокоманди

- •7.6. Управління мікрокомандами: Mic-1

- •7.7. Приклад архітектури команд: ijvm

- •7.8. Модель пам'яті ijvm

- •Питання до лекції

- •8. Рівень архітектури команд

- •8.1. Моделі пам'яті

- •8.2. Загальний огляд рівня архітектури команд

- •8.3. Властивості рівня команд

- •8.4. Регістри

- •8.5. Команди

- •8.6. Загальний огляд рівня команд машини Pentium II

- •8.8. Загальний огляд рівня команд системи ultrasparc II

- •8.9. Загальний огляд віртуальної машини Java

- •8.10. Типи даних

- •8.11. Числові типи даних

- •8.12. Нечислові типи даних

- •8.13. Типи даних процесора Pentium II

- •Підтримувані типи відмічені хрестом (х)

- •8.14. Типи даних машини UltraSparc II

- •8.16. Типи даних віртуальної машини Java

- •8.17. Формати команд

- •Питання до лекції

- •9. Адресація

- •9.1. Способи адресації

- •9.2. Безпосередня адресація

- •9.3. Пряма адресація

- •9.4. Регістрова адресація

- •9.5. Непряма регістрова адресація

- •Лістинг 9.1 - Програма на асемблері для обрахунку суми елементів масиву.

- •9.6. Індексна адресація

- •Листинг 9.2. Програма на мові асемблера для обчислення операції або від (Аі і Ві ) для масиву з 1024 елементів.

- •9.7. Відносна індексна адресація

- •9.8. Стекова адресація

- •9.9. Зворотній польський запис

- •9.10. Обчислення формул в зворотнім польськім записі

- •Питання до лекції

8.8. Загальний огляд рівня команд системи ultrasparc II

Архітектура SPARC була вперше введена в 1987 році компанією Sun Microsystems. Ця архітектура була однією з першої архітектури промислового призначення типу RISC. Вона була заснована на дослідженні, проведеному в Берклі в 80-і роки [110, 113]. Спочатку система SPARC була 32-розрядною архітектурою, але UltraSPARC II — це 64-розрядна машина, заснована на Version 9, і саме її ми описуватимемо в цьому розділі. В цілях узгодженості з рештою частин книги ми називатимемо дану систему UltraSPARC II, хоча на рівні команд всі машини UltraSPARC ідентичні.

Структура пам'яті машини UltraSPARC II дуже проста: пам'ять є лінійним масивом з 264 байтів. На жаль, пам'ять настільки велика (18 446 744 073 709 551 616 байтів), що в даний час її неможливо реалізувати. Сучасні реалізації мають обмеження на розмір адресного простору, до якого вони можуть звертатися (244байтов у UltraSPARC II), але в майбутньому це число збільшиться. Байти нумеруються зліва направо, але нумерацію можна зрадити і зробити її справа наліво, встановивши біт в регістрі прапора.

Важливо, що архітектура команд має більше байт, чим потрібний для реалізації, оскільки в майбутньому, швидше за все, знадобиться збільшити розмір пам'яті, до якої може звертатися процесор. Одна з найсерйозніших проблем при розробці архітектури полягає в тому, що архітектура команд обмежує розмір пам'яті, що адресується. У інформатиці існує одне питання, яке неможливо вирішити: ніколи не вистачає тої кількість бітів, яка є в даний момент. Коли-небудь ваші внуки запитають у вас, як же могли працювати комп'ютери, які містять всього лише 32-бітові адреси і лише 4 Гбайт пам'яті.

Архітектура команд SPARC достатньо проста, хоча організація регістрів була небагато ускладнена, щоб зробити виклики процедур ефективнішими. Практика показує, що організація регістрів вимагає великих зусиль і в загальному ці зусилля не коштують того, але правило сумісності не дозволяє позбавитися цього.

У системі UltraSPARC II є дві групи регістрів: 32 64-бітових регістра загального призначення і 32 регістри з плаваючою крапкою. Регістри загального призначення називаються R0-R31, але в певних контекстах використовуються інші назви. Варіанти назв регістрів і їх функції приведені в табл. 8.1.

Таблиця 8.1 - Регістри загального призначення в системі UltraSPARC II

Регістр |

Інший варіант назви |

Функція |

R0

R1-R7 R8-R13

R14 R15 R16-R23

R24-R29 R30

R31 |

G0

G1-G7 O0-O5

SP O7 L0-L7

I0-I5 FP

I7 |

Зв'язаний з 0. Те, що збережене в цьому регістрі просто ігнорується Містить глобальні змінні Містить параметри процедури, що викликається Покажчик стека Тимчасовий регістр Містить локальні змінні для поточної процедури Містить вхідні параметри Покажчик на основу поточного стекового фрейма Містить адресу повернення для поточної процедури |

Всі регістри загального призначення 64-бітові. Всі вони, окрім R0, значення якого завжди рівне 0, можуть прочитуватися і записуватися за допомогою різних команд завантаження і збереження. Функції, приведені в табл. 8.1, частково визначені за угодою, але частково засновані на тому, як апаратне забезпечення обробляє їх. Взагалі не варто відхилятися від цих функцій, якщо ви не являєтесь крупним фахівцем, блискуче розбираєтесь в комп'ютерах SPARC. Програміст повинен бути упевнений, що програма правильно звертається до регістрів і виконує над ними допустимі арифметичні дії. Наприклад, дуже легко завантажити числа з плаваючою крапкою в регістри загального призначення, а потім провести над ними цілочисельне складання, операцію, яка приведе до повної нісенітниці, але яку центральний процесор обов'язково виконає, якщо цього зажадає програма.

Глобальні змінні використовуються для зберігання констант, змінних і покажчиків, які потрібні у всіх процедурах, хоча вони можуть завантажуватися і перезавантажутись при вході в процедуру і при виході з процедури, якщо потрібно. Регістри Іх і Ох використовуються для передачі параметрів процедурам, щоб уникнути звернень до пам'яті. Нижче ми розповімо, як це відбувається.

Спеціальні регістри використовуються для особливих цілей. Регістри FP і SP обмежують поточний фрейм. Перший указує на основу поточного фрейма і використовується для звернення до локальних змінних так само як LV на мал. 4.9. Іншою указує на поточну вершину стека і змінюється, коли слова поміщаються в стек або виштовхуються звідти. Значення регістра FP змінюється тільки при виклику і завершенні процедури. Третій спеціальний регістр — R31. Він містить адресу повернення для поточної процедури.

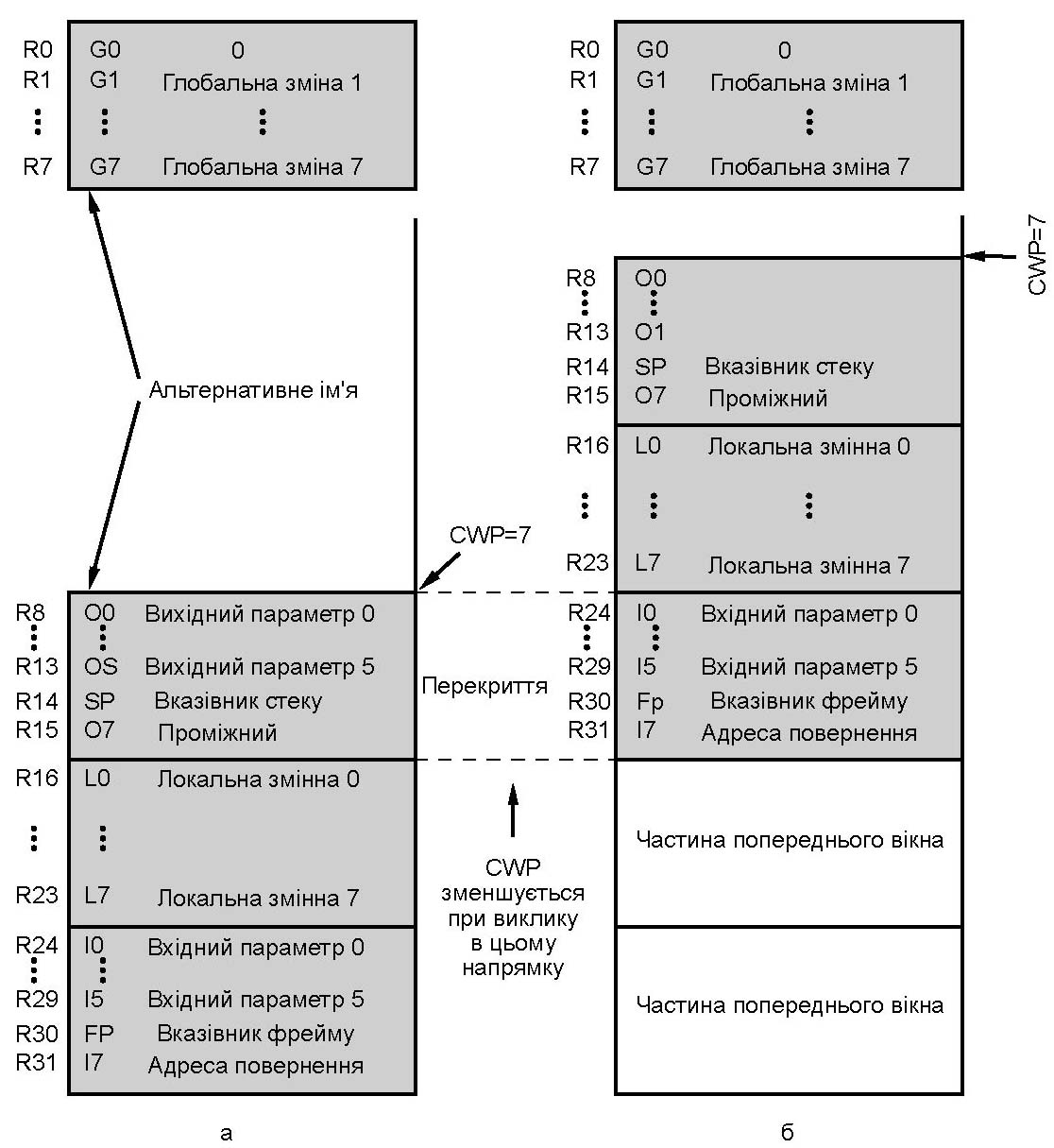

Насправді процесор UltraSPARC II має більше 32 регістрів загального призначення, але тільки 32 з них видно для програми у будь-який момент часу. Ця особливість, звана регістровими вікнами, призначена для підвищення ефективності виклику процедур. Система регістрових вікон проілюстрована на мал. 5.4. Основна ідея — імітувати стек, використовуючи при цьому регістри. Тобто існує декілька наборів регістрів, так само як і декілька фреймів в стеку. Рівно 32 регістри загального призначення видно у будь-який момент. Регістр CWP (Current Window Pointer - покажчик поточного вікна) стежить за тим, який набір регістрів використовується в даний момент.

Команда виклику процедури приховує старий набір регістрів і шляхом зміни CWP надає новий набір, який може використовувати викликана процедура. Проте деякі регістри переносяться з тієї, що викликає процедури до викликаної процедури, що забезпечує ефективний спосіб передачі параметрів між процедурами. Для цього деякі регістри перейменовуються: після виклику процедури колишні вихідні регістри з R8 по R15 все ще видно, але тепер це вхідні регістри з R24 по R31. Вісім глобальних регістрів не міняються. Це завжди один і той же набір регістрів.

Мал. 8.4 - Регістрові вікна системи UltraSPARC II

На відміну від пам'яті, яка квазібескінечна (принаймні, в відношенні стеків), якщо відбувається багатократне вкладення процедур, машина виходить з регістрових вікон. У цей момент найстаріший набір регістрів скидається в пам'ять, щоб звільнити новий набір. Так само після багатократних виходів з процедур може знадобитися викликати набір регістрів з пам'яті. В цілому така ускладненість є великою перешкодою і, взагалі кажучи, не дуже корисна. Така система вигідна тільки в тому випадку, якщо немає багатократних вкладених процедур.

У системі UltraSPARC II є також 32 регістри з плаваючою крапкою, які можуть містити або 32-бітові (одинарна точність), або 64-бітові (подвійна точність) значення. Можливо також використовувати пару цих регістрів, щоб підтримувати 128-бітові значення.

Архітектура UltraSPARC II — архітектура завантаження/зберігання. Це означає, що єдині операції, які безпосередньо звертаються до пам'яті, — це команди LOAD (завантаження) і STORE (збереження), що служать для переміщення даних між регістрами і пам'яттю. Всі операнди для команд арифметичних і логічних дій повинні братися з регістрів або надаватися самою командою (але не повинні братися з пам'яті), і всі результати повинні зберігатися в регістрах (але не в пам'яті).