- •Мови, рівні і віртуальні машини

- •Сучасні багаторівневі машини

- •Поняття архітектури пк

- •1.4. Розвиток комп’ютерної архітектури

- •Розвиток багаторівневих машин

- •Типи сучасних еом

- •Питання до лекції

- •2.1. Принципи розробки сучасних комп'ютерів

- •2.2. Паралелізм на рівні команд

- •2.3. Конвеєри

- •2.4. Суперскалярні архітектури

- •2.5. Паралелізм на рівні процесорів

- •2.6. Векторні комп'ютери

- •Блок управління

- •2.7. Мультипроцессори

- •2.8. Мультикомпьютери

- •Питання до лекції

- •3. Основи комп’ютерної організації : пам’ять

- •3.1. Ієрархічна структура пам'яті

- •3.2. Загальні відомості про пам'ять

- •3.4. Методи звертання до пам'яті

- •3.5. Модулі пам'яті

- •3.6. Ряди і банки пам'яті

- •3.8. Код з виправленням помилок

- •3. 9. Скільки потрібно пам'яті

- •Питання до лекції

- •4. Цифровий рівень побудови ом

- •4.1. Вентилі і булева алгебра

- •4.2. Булева алгебра

- •4.3. Реалізація булевих функцій

- •4.4. Еквівалентність схем

- •Основні цифрові логічні схеми Інтегральні схеми

- •4.5. Комбінаційні схеми

- •3 Входи і 8 виходів

- •4.6. Арифметичні схеми.

- •4.7. Тактові генератори

- •Питання до лекції

- •Цифровий рівень побудови ом.

- •5. Цифровий логічний рівень архітектури: пам’ять, мікропроцесори

- •5.2. Синхронні sr-защіпки

- •5.3. Синхронні d-защіпки

- •5.4. Тригери (flip-flops)

- •5.5. Регістри

- •5.6. Організація пам'яті

- •Тригер (б)

- •Кожний ряд представляє одне з 3-бітних слів. При операції зчитування і запису завжди зчитується або записується ціле слово

- •5.7. Мікросхеми пам'яті

- •5.9. Мікросхеми процесорів

- •Стрілочки указують вхідні і вихідні сигнали. Короткі діагональні лінії вказують на наявність декількох висновків.

- •Питання до лекції

- •6. Шини

- •6.1. Ширина шини

- •6.2. Синхронізація шини

- •6.3. Синхронні шини

- •6.5. Асинхронні шини

- •6.6. Арбітраж шини

- •6.7. Принципи роботи шини

- •Питання до лекції

- •7. Мікроархітектурний рівень

- •7.1. Приклад мікроархітектури

- •7.2. Тракт даних

- •В цьому розділі

- •Табліця 7.1. Деякі комбінації сигналів аллу і відповідні їм функції

- •7.3. Синхронізація тракту даних

- •7.4. Робота пам'яті.

- •7.5. Мікрокоманди

- •7.6. Управління мікрокомандами: Mic-1

- •7.7. Приклад архітектури команд: ijvm

- •7.8. Модель пам'яті ijvm

- •Питання до лекції

- •8. Рівень архітектури команд

- •8.1. Моделі пам'яті

- •8.2. Загальний огляд рівня архітектури команд

- •8.3. Властивості рівня команд

- •8.4. Регістри

- •8.5. Команди

- •8.6. Загальний огляд рівня команд машини Pentium II

- •8.8. Загальний огляд рівня команд системи ultrasparc II

- •8.9. Загальний огляд віртуальної машини Java

- •8.10. Типи даних

- •8.11. Числові типи даних

- •8.12. Нечислові типи даних

- •8.13. Типи даних процесора Pentium II

- •Підтримувані типи відмічені хрестом (х)

- •8.14. Типи даних машини UltraSparc II

- •8.16. Типи даних віртуальної машини Java

- •8.17. Формати команд

- •Питання до лекції

- •9. Адресація

- •9.1. Способи адресації

- •9.2. Безпосередня адресація

- •9.3. Пряма адресація

- •9.4. Регістрова адресація

- •9.5. Непряма регістрова адресація

- •Лістинг 9.1 - Програма на асемблері для обрахунку суми елементів масиву.

- •9.6. Індексна адресація

- •Листинг 9.2. Програма на мові асемблера для обчислення операції або від (Аі і Ві ) для масиву з 1024 елементів.

- •9.7. Відносна індексна адресація

- •9.8. Стекова адресація

- •9.9. Зворотній польський запис

- •9.10. Обчислення формул в зворотнім польськім записі

- •Питання до лекції

7.4. Робота пам'яті.

Наша машина може взаємодіяти з пам'яттю двома способами: через порт з послівною адресацією (32-бітовий) і через порт з байтовою адресацією (8-бітовий). Порт з послівною адресацією управляється двома регістрами: MAR (Memory Address Register — регістр адреси елементу пам'яті) і MDR (Memory Data Register — інформаційний регістр пам'яті), які показані на мал. 4.1. Порт з байтовою адресацією управляється регістром PC, який записує 1 байт в 8 молодших розрядів регістра MBR (Memory Buffer Register — буферний регістр пам'яті). Цей порт може прочитувати дані з пам'яті, але не може їх записувати в пам'ять. Кожний з цих регістрів, а також вся решта регістрів, зображених на мал. 7.1, запускається одним з сигналів управління. Біла стрілка під регістром указує на сигнал управління, який дозволяє передавати вихідний сигнал регістра на шину В. Регістр MAR не пов'язаний з шиною В, тому у нього немає сигналу дозволу. Біля регістра Н цього сигналу теж немає, оскільки він є єдиним можливим лівим входом АЛЛУ і тому завжди дозволений.

Не враховуються 32-бітний регістр MAR (вимірюється в словах)

32-бітна

адресна шина (вимірюється в байтах)

32-бітна

адресна шина (вимірюється в байтах)

Рис. 7.3. Розподілення бітів регістра MAR в адресній шині

Чорна стрілка під регістром указує на сигнал управління, який записує (тобто завантажує) регістр з шини С. Оскільки регістр MBR не може завантажуватися з шини С, у нього немає сигналу запису (та зате є два сигнали дозволу, про які мова піде нижчим).

Як вже було сказано вище, дані, лічені з пам'яті через 8-бітовий порт, зберігаються в 8-бітовому регістрі MBR. Цей регістр може бути скопійований на шину В двома способами: із знаком і без знаку. Коли потрібне значення без знаку, 32-бітове слово, що поміщається на шину В, містить значення MBR в молодших 8 бітах і нулі в решті 24 біт. Значення без знаку потрібні для індексації таблиць або для отримання цілого 16-бітового числа з двох послідовних байтів (без знаку) в потоці команд.

Інший спосіб перетворення 8-бітового регістра MBR в 32-бітове слово — розглядати його як значення із знаком між -128 і +127 і використовувати це значення для породження 32-бітового слова з тим же самим чисельним значенням. Це перетворення робиться шляхом дублювання знакового біта (найлівішого біта) регістра MBR у верхній 24 бітовій позиції шини В. Такий процес називається розширенням по знаку або знаковим розширенням. Якщо вибраний даний параметр, то або всі старші 24 біти приймуть значення 0, або всі вони приймуть значення 1, залежно від того, який найлівіший біт регістра MBR: 0 або 1.

У яке саме 32-бітове значення (із знаком або без знаку) перетвориться 8-бітове значення регістра MBR, визначається тим, який з двох сигналів управління (дві білі стрілки під регістром MBR на рис. 7.1) встановлений. Прямокутник, позначений на малюнку пунктиром, показує здатність 8-бітового регістра MBR діяти як джерело 32-бітових слів для шини В.

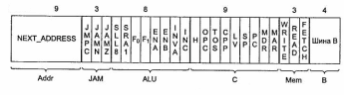

7.5. Мікрокоманди

Для управління трактом даних, зображеним на рис. 7.1, нам потрібно 29 сигналів. Їх можна розділити на п'ять функціональних груп:

¦ 9 сигналів для запису даних з шини З в регістри.

+ 9 сигналів для дозволу передачі регістрів на шину В'ючи АЛЛУ.

¦ 8 сигналів для управління АЛЛУ і схемою зсуву.

+ 2 сигнали, які указують, що потрібно здійснити читання або запис через регістри MAR/MDR (на малюнку вони не показані).

+ 1 сигнал, який указує, що потрібно здійснити виклик з пам'яті через регістри PC/MBR (на малюнку також не показаний).

Значення ці 29 сигналів управління визначають операції для одного циклу тракту даних. Цикл складається з передачі значень регістрів на шину В, проходження цих сигналів через АЛЛУ і схему зсуву, передачі одержаних результатів на шину З і записи їх в потрібний регістр (регістри). Крім того, якщо встановлений сигнал прочитування даних, то в кінці циклу після завантаження регістра MAR починається робота пам'яті. Дані з пам'яті поміщаються в MBR або MDR в кінці наступного циклу, а використовуватися ці дані можуть в циклі, який йде після нього. Іншими словами, якщо прочитування з пам'яті через будь-який з портів починається в кінці циклу до, то одержані дані ще не можуть використовуватися в циклі к+1 (тільки в циклі к+2 і пізніше).

Цей процес пояснюється на рис. 7.2. Сигнали управління пам'яттю видаються тільки після завантаження регістрів MAR і PC, яке відбувається на наростаючому фронті синхронізуючого сигналу незадовго до кінця циклу 1. Ми припустимо, що пам'ять поміщає результати на шину пам'яті протягом одного циклу, тому регістри MBR і (або) MDR можуть завантажуватися на наступному наростаючому фронті разом з іншими регістрами.

Іншими словами, ми завантажуємо регістр MAR в кінці циклу тракту даних і запускаємо пам'ять відразу після цього. Отже, ми не можемо чекати, що результати прочитування будуть в регістрі MDR на початку наступного циклу, особливо якщо тривалість імпульсу невелика. Цього часу буде недостатньо. Тому між початком прочитування з пам'яті і використовуванням цього результату повинен поміщатися один цикл. Проте під час цього циклу може виконуватися не тільки передача слова з пам'яті, але і інші операції.

Припущення про те, що робота пам'яті займає один цикл, еквівалентне припущенню, що кількість успішного обігу в кеш-пам'ять складає 100%. Подібне припущення ніколи не може бути істинним, але ми тут не розказуватимемо про цикли пам'яті змінної довжини, оскільки це не входить в задачі даної книги.

Оскільки регістри MBR і MDR завантажуються на наростаючому фронті синхронізуючого сигналу разом з іншими регістрами, вони можуть прочитувати під час циклів, протягом яких здійснюється передача нового слова з пам'яті. Вони повертають старі значення, оскільки пройшло ще недостатньо часу для того, щоб поміняти їх на нові. Тут немає ніякої двозначності: доти поки нові значення не завантажаться в регістри MBR і MDR на наростаючому фронті сигналу, попередні значення знаходяться там і можуть використовуватися. Відзначимо, що прочитування можуть проходити одне за іншим, тобто в двох послідовних циклах (оскільки сам процес прочитування займає тільки один цикл). Крім того, обидва пам'яті можуть діяти в один і той же час. Проте спроба читання і запису одного і того ж байта одночасно приводить до невизначених результатів.

Вихідний сигнал шини З можна записувати відразу в декілька регістрів, проте небажано передавати значення більше одного регістра на шину В. Трохи розширивши схемотехніку, ми можемо скоротити кількість бітів, необхідних для вибору одного з можливих джерел для запуску шини В. Існує тільки 9 вхідних регістрів, які можуть запустити шину В (регістри MBR із знаком і без знаку враховуються окремо). Отже, ми можемо закодувати інформацію для шини У в 4 біти і використати декодер для породження 16 сигналів управління, 7 з яких не потрібні. У розробників комерційних моделей, можливо, було б велике бажання позбавитися від одного з регістрів, щоб обійтися 3 бітами. Проте ми як учені вважаємо за краще мати один зайвий біт, але при цьому одержати більш ясну і просту розробку.

Біти

Регістри шини В

0=MDR 5=LV

1=PC 6=CPP

2=MBR 7=TOS

3=MBRU 8=OPC

4=SP 9-15- нет

Рис.7.4. Формат мікрокоманди для МІС-1

Тепер ми можемо управляти трактом даних за допомогою 9+4+8+2+1 =24 сигналів, отже, нам потрібне 24 біти. Проте ці 24 біти управляють трактом даних тільки протягом одного циклу. Задача управління — визначити, що потрібно робити в наступному циклі. Щоб включити це в розробку контролера, ми створимо формат для опису операцій, які потрібно виконати, використовуючи 24 біти управління і два додаткові поля: поле NEXT_ADDRESS (наступна адреса) і поле JAM. Зміст кожного з цих полів ми обговоримо пізніше. На рис. 7.4 зображений один з можливих форматів. Він роздільний на наступні 6 груп, що містять 36 сигналів:

¦ Addr — містить адресу наступної потенційної мікрокоманди. + JAM — визначає, як вибирається наступна мікрокоманда.

+ ALU — функції АЛЛУ і схеми зсуву.

+ З — вибирає, які регістри записуються з шини С.

¦ Mem — функції пам'яті.

+ У — вибирає джерело для шини В (як він кодується, було показано вище).

Порядок груп у принципі довільний, хоча ми довго і ретельно його підбирали, щоб уникнути перетинів на рис. 7.5. Подібні перетини на діаграмах часто відповідають перетинам дротів на мікросхемах. Вони сильно утрудняють розробку і їх краще зводити до мінімуму.