- •Мови, рівні і віртуальні машини

- •Сучасні багаторівневі машини

- •Поняття архітектури пк

- •1.4. Розвиток комп’ютерної архітектури

- •Розвиток багаторівневих машин

- •Типи сучасних еом

- •Питання до лекції

- •2.1. Принципи розробки сучасних комп'ютерів

- •2.2. Паралелізм на рівні команд

- •2.3. Конвеєри

- •2.4. Суперскалярні архітектури

- •2.5. Паралелізм на рівні процесорів

- •2.6. Векторні комп'ютери

- •Блок управління

- •2.7. Мультипроцессори

- •2.8. Мультикомпьютери

- •Питання до лекції

- •3. Основи комп’ютерної організації : пам’ять

- •3.1. Ієрархічна структура пам'яті

- •3.2. Загальні відомості про пам'ять

- •3.4. Методи звертання до пам'яті

- •3.5. Модулі пам'яті

- •3.6. Ряди і банки пам'яті

- •3.8. Код з виправленням помилок

- •3. 9. Скільки потрібно пам'яті

- •Питання до лекції

- •4. Цифровий рівень побудови ом

- •4.1. Вентилі і булева алгебра

- •4.2. Булева алгебра

- •4.3. Реалізація булевих функцій

- •4.4. Еквівалентність схем

- •Основні цифрові логічні схеми Інтегральні схеми

- •4.5. Комбінаційні схеми

- •3 Входи і 8 виходів

- •4.6. Арифметичні схеми.

- •4.7. Тактові генератори

- •Питання до лекції

- •Цифровий рівень побудови ом.

- •5. Цифровий логічний рівень архітектури: пам’ять, мікропроцесори

- •5.2. Синхронні sr-защіпки

- •5.3. Синхронні d-защіпки

- •5.4. Тригери (flip-flops)

- •5.5. Регістри

- •5.6. Організація пам'яті

- •Тригер (б)

- •Кожний ряд представляє одне з 3-бітних слів. При операції зчитування і запису завжди зчитується або записується ціле слово

- •5.7. Мікросхеми пам'яті

- •5.9. Мікросхеми процесорів

- •Стрілочки указують вхідні і вихідні сигнали. Короткі діагональні лінії вказують на наявність декількох висновків.

- •Питання до лекції

- •6. Шини

- •6.1. Ширина шини

- •6.2. Синхронізація шини

- •6.3. Синхронні шини

- •6.5. Асинхронні шини

- •6.6. Арбітраж шини

- •6.7. Принципи роботи шини

- •Питання до лекції

- •7. Мікроархітектурний рівень

- •7.1. Приклад мікроархітектури

- •7.2. Тракт даних

- •В цьому розділі

- •Табліця 7.1. Деякі комбінації сигналів аллу і відповідні їм функції

- •7.3. Синхронізація тракту даних

- •7.4. Робота пам'яті.

- •7.5. Мікрокоманди

- •7.6. Управління мікрокомандами: Mic-1

- •7.7. Приклад архітектури команд: ijvm

- •7.8. Модель пам'яті ijvm

- •Питання до лекції

- •8. Рівень архітектури команд

- •8.1. Моделі пам'яті

- •8.2. Загальний огляд рівня архітектури команд

- •8.3. Властивості рівня команд

- •8.4. Регістри

- •8.5. Команди

- •8.6. Загальний огляд рівня команд машини Pentium II

- •8.8. Загальний огляд рівня команд системи ultrasparc II

- •8.9. Загальний огляд віртуальної машини Java

- •8.10. Типи даних

- •8.11. Числові типи даних

- •8.12. Нечислові типи даних

- •8.13. Типи даних процесора Pentium II

- •Підтримувані типи відмічені хрестом (х)

- •8.14. Типи даних машини UltraSparc II

- •8.16. Типи даних віртуальної машини Java

- •8.17. Формати команд

- •Питання до лекції

- •9. Адресація

- •9.1. Способи адресації

- •9.2. Безпосередня адресація

- •9.3. Пряма адресація

- •9.4. Регістрова адресація

- •9.5. Непряма регістрова адресація

- •Лістинг 9.1 - Програма на асемблері для обрахунку суми елементів масиву.

- •9.6. Індексна адресація

- •Листинг 9.2. Програма на мові асемблера для обчислення операції або від (Аі і Ві ) для масиву з 1024 елементів.

- •9.7. Відносна індексна адресація

- •9.8. Стекова адресація

- •9.9. Зворотній польський запис

- •9.10. Обчислення формул в зворотнім польськім записі

- •Питання до лекції

6.5. Асинхронні шини

Хоча достатньо зручно використовувати синхронні шини завдяки дискретним тимчасовим інтервалам, тут все ж таки є деякі проблеми. Наприклад, якщо процесор і пам'ять здатні закінчити передачу 3,1 циклу, вони вимушені продовжити її до 4,0 циклів, оскільки неповні цикли заборонені.

Ще гірше то, що якщо одного разу був вибраний певний цикл шини і відповідно до нього були розроблені пам'ять і карти вводу-виводу, то в майбутньому важко робити технологічні удосконалення. Наприклад, припустимо, що через декілька років після випуску системи, зображеної на рис. 6.3, з'явилася нова пам'ять з часом доступу не 40, а 20 не. Це позбавило б нас від періоду очікування і збільшило швидкість роботи машини. Тепер уявимо, що з'явилася пам'ять з часом доступу 10 не. При цьому поліпшення продуктивності вже не буде, оскільки в даній розробці мінімальний час для читання — 2 цикли.

Якщо синхронна шина сполучає ряд пристроїв, одні з яких працюють швидко, а інші поволі, шина підстроюється під найповільніший пристрій, а швидші не можуть використовувати свій повний потенціал.

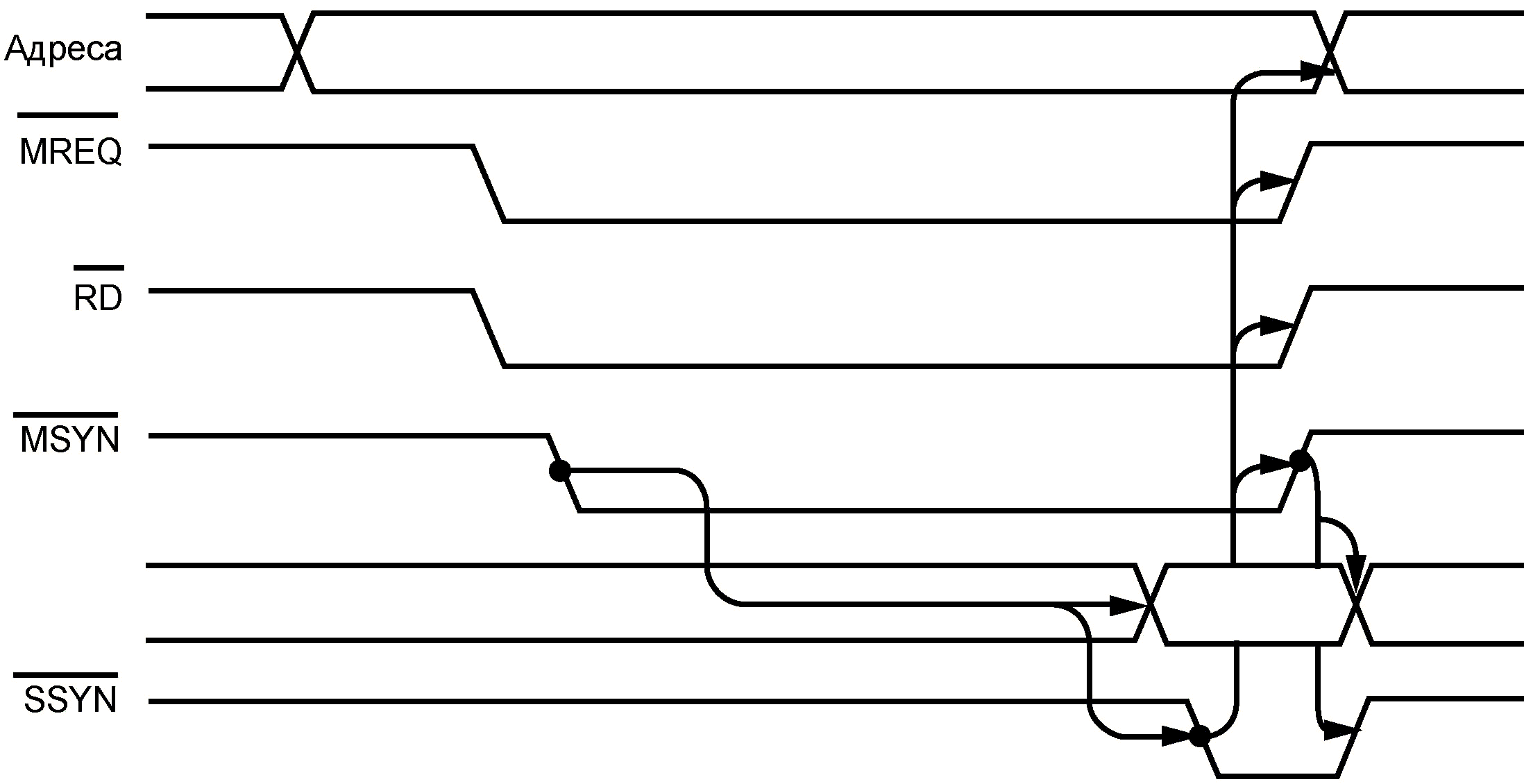

З цієї причини були розроблені асинхронні шини, тобто шини без задаючого генератора, як показано на рис. 6.4. Тут нічого не прив'язується до генератора. Коли задаючий пристрій встановлює адресу, MREQ RD і будь-який інший необхідний сигнал, вона видає спеціальний сигнал, який ми називатимемо MSYN (Master SYNchronization). Коли підлеглий пристрій одержує цей сигнал, воно починає виконувати свою роботу настільки швидко, наскільки це можливо. Коли робота закінчена, пристрій видає сигнал SSYN (Slave SYNchronization).

Сигнал SSYN означає для задаючого пристрою, що дані доступні. Він фіксує їх, а потім відключає адресні лінії разом з MREQ, RD і MSYN. Відміна сигналу MSYN означає для підлеглого пристрою, що цикл закінчений, тому пристрій відміняє сигнал SSYH, і все повертається до первинного стану, коли всі сигнали скасовані.

Рис. 6.4 – Робота асинхронної шини

Стрілки на тимчасових діаграмах асинхронних шин (а іноді і синхронних шин) показують причину і наслідок якої-небудь дії (рис. 6.4). Установка сигналу MSYN приводить до запуску інформаційних ліній, а також до установки сигналу SSYN. Установка сигналу SSYN, у свою чергу, викликає відключення адресних ліній, MREQ, З і MSYN. Нарешті, відключення MSYN викликає відключення SSYN, і на цьому процес прочитування закінчується.

Набір таких взаємообумовлених сигналів називається повним квитуванням. Тут, по суті, спостерігається 4 події:

1. Установка сигналу MSYN.

2. Установка сигналу SSYN у відповідь на сигнал MSYN.

3. Відміна сигналу NtSYN у відповідь на сигнал SSYN.

4. Відміна сигналу SSYN у відповідь на відміну сигналу MSYN.

Слід з'ясувати, що взаємообумовленість сигналів не залежить від синхронізації. Кожна подія викликається попередньою подією, а не імпульсами генератора. Якщо якась пара двох пристроїв (задаючого і підпорядкованого) працює поволі, це ніяк не вплине на наступну пару пристроїв, яка працює набагато швидше.

Переваги асинхронної шини очевидні, але насправді більшість шин є синхронними. Річ у тому, що синхронну систему побудувати простіше, ніж асинхронну. Центральний процесор просто видає сигнали, а пам'ять просто реагує на них. Тут немає ніякого причинно-наслідкового зв'язку, але якщо компоненти вибрані вдало, все працюватиме і без квитування. Крім того, в розробку синхронних шин зроблено дуже багато вкладень.