- •Мови, рівні і віртуальні машини

- •Сучасні багаторівневі машини

- •Поняття архітектури пк

- •1.4. Розвиток комп’ютерної архітектури

- •Розвиток багаторівневих машин

- •Типи сучасних еом

- •Питання до лекції

- •2.1. Принципи розробки сучасних комп'ютерів

- •2.2. Паралелізм на рівні команд

- •2.3. Конвеєри

- •2.4. Суперскалярні архітектури

- •2.5. Паралелізм на рівні процесорів

- •2.6. Векторні комп'ютери

- •Блок управління

- •2.7. Мультипроцессори

- •2.8. Мультикомпьютери

- •Питання до лекції

- •3. Основи комп’ютерної організації : пам’ять

- •3.1. Ієрархічна структура пам'яті

- •3.2. Загальні відомості про пам'ять

- •3.4. Методи звертання до пам'яті

- •3.5. Модулі пам'яті

- •3.6. Ряди і банки пам'яті

- •3.8. Код з виправленням помилок

- •3. 9. Скільки потрібно пам'яті

- •Питання до лекції

- •4. Цифровий рівень побудови ом

- •4.1. Вентилі і булева алгебра

- •4.2. Булева алгебра

- •4.3. Реалізація булевих функцій

- •4.4. Еквівалентність схем

- •Основні цифрові логічні схеми Інтегральні схеми

- •4.5. Комбінаційні схеми

- •3 Входи і 8 виходів

- •4.6. Арифметичні схеми.

- •4.7. Тактові генератори

- •Питання до лекції

- •Цифровий рівень побудови ом.

- •5. Цифровий логічний рівень архітектури: пам’ять, мікропроцесори

- •5.2. Синхронні sr-защіпки

- •5.3. Синхронні d-защіпки

- •5.4. Тригери (flip-flops)

- •5.5. Регістри

- •5.6. Організація пам'яті

- •Тригер (б)

- •Кожний ряд представляє одне з 3-бітних слів. При операції зчитування і запису завжди зчитується або записується ціле слово

- •5.7. Мікросхеми пам'яті

- •5.9. Мікросхеми процесорів

- •Стрілочки указують вхідні і вихідні сигнали. Короткі діагональні лінії вказують на наявність декількох висновків.

- •Питання до лекції

- •6. Шини

- •6.1. Ширина шини

- •6.2. Синхронізація шини

- •6.3. Синхронні шини

- •6.5. Асинхронні шини

- •6.6. Арбітраж шини

- •6.7. Принципи роботи шини

- •Питання до лекції

- •7. Мікроархітектурний рівень

- •7.1. Приклад мікроархітектури

- •7.2. Тракт даних

- •В цьому розділі

- •Табліця 7.1. Деякі комбінації сигналів аллу і відповідні їм функції

- •7.3. Синхронізація тракту даних

- •7.4. Робота пам'яті.

- •7.5. Мікрокоманди

- •7.6. Управління мікрокомандами: Mic-1

- •7.7. Приклад архітектури команд: ijvm

- •7.8. Модель пам'яті ijvm

- •Питання до лекції

- •8. Рівень архітектури команд

- •8.1. Моделі пам'яті

- •8.2. Загальний огляд рівня архітектури команд

- •8.3. Властивості рівня команд

- •8.4. Регістри

- •8.5. Команди

- •8.6. Загальний огляд рівня команд машини Pentium II

- •8.8. Загальний огляд рівня команд системи ultrasparc II

- •8.9. Загальний огляд віртуальної машини Java

- •8.10. Типи даних

- •8.11. Числові типи даних

- •8.12. Нечислові типи даних

- •8.13. Типи даних процесора Pentium II

- •Підтримувані типи відмічені хрестом (х)

- •8.14. Типи даних машини UltraSparc II

- •8.16. Типи даних віртуальної машини Java

- •8.17. Формати команд

- •Питання до лекції

- •9. Адресація

- •9.1. Способи адресації

- •9.2. Безпосередня адресація

- •9.3. Пряма адресація

- •9.4. Регістрова адресація

- •9.5. Непряма регістрова адресація

- •Лістинг 9.1 - Програма на асемблері для обрахунку суми елементів масиву.

- •9.6. Індексна адресація

- •Листинг 9.2. Програма на мові асемблера для обчислення операції або від (Аі і Ві ) для масиву з 1024 елементів.

- •9.7. Відносна індексна адресація

- •9.8. Стекова адресація

- •9.9. Зворотній польський запис

- •9.10. Обчислення формул в зворотнім польськім записі

- •Питання до лекції

6.1. Ширина шини

Ширина шини — найочевидніший параметр при розробці. Чим більше адресних ліній містить шина, тим до більшого об'єму пам'яті може звертатися процесор. Якщо шина містить п адресних ліній, тоді процесор може використовувати її для звернення до 2-х різних елементів пам'яті. Для пам'яті великої місткості необхідно багато адресних ліній. Це звучить досить просто.

Проблема полягає в тому, що для широких шин потрібно більше дротів, ніж для вузьких. Вони займають більше фізичного простору (наприклад, на материнській платі), і для них потрібні роз'єми більшого розміру. Всі ці чинники роблять шину дорогою. Отже, необхідний компроміс між максимальним розміром пам'яті і вартістю системи. Система з шиною, що містить 64 адресних лінії, і пам'яттю в 232 байт коштуватиме дорожче, ніж система з шиною, що містить 32 адресних лінії, і такою ж пам'яттю в 232байт. Подальше розширення не безкоштовне.

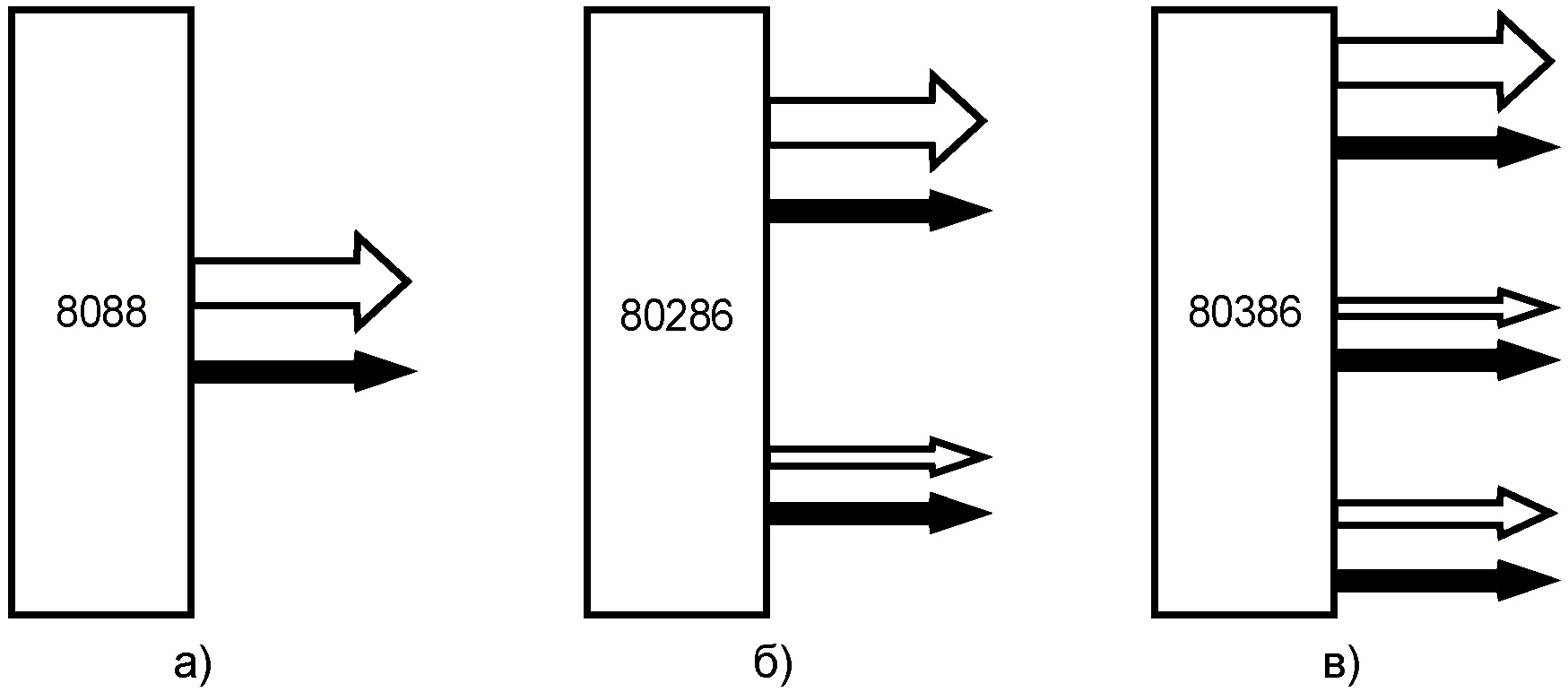

Багато розробників систем недалекоглядні, що приводить до неприємних наслідків. Перша модель IBM PC містила процесор 8088 і 20-бітову адресну шину (рис. 6.2 а). Шина дозволяла звертатися до 1 Мбайт пам'яті.

Рис. 6.2 – Розширення адресної шини з часом

Коли з'явився наступний процесор (80286), Intel вирішив збільшити адресний простір до 16 Мбайт, тому довелося додати ще 4 лінії (не порушуючи початкові 20 з причин сумісності із старішими версіями), як показано на рис. 6.2. б. На жаль, довелося також додати лінії управління для нових адресних ліній. Коли з'явився процесор 80386, було додано ще 8 адресних ліній і, природно, декілька ліній управління, як показано на рис. 6.2 в. В результаті вийшла шина EISA. Проте було б краще, якби із самого початку були 32 лінії.

З часом збільшується не тільки число адресних ліній, але і число інформаційних ліній. Хоча це відбувається по декілька іншій причині. Можна збільшити пропускну спроможність шини двома способами: скоротити час циклу шини (зробити більшу кількість передач в секунду) або збільшити ширину шини даних (тобто збільшити кількість бітів за одну передачу). Можна підвищити швидкість роботи шини, але зробити це досить складно, оскільки сигнали на різних лініях передаються з різною швидкістю (це явище називається перекосом шини). Чим швидше працює шина, тим більше перекіс.

При збільшенні швидкості роботи шини виникає ще одна проблема: в цьому випадку вона не буде сумісною із старішими версіями, Стара плата, розроблена для повільнішої шини, не може працювати з новою. Така ситуація невигідна для власників і виробників старої платі. Тому звичайно для збільшення продуктивності просто додаються нові лінії, як показано на рис. 6.2. Як ви розумієте, в цьому теж є свої недоліки. IBM PC і його послідовники, наприклад, почали з 8 інформаційних ліній, потім перейшли до 16, а потім до 32, і все це в одній і тій же шині.

Щоб обійти цю проблему, розробники іноді віддають перевагу мультиплексній шині. У цій шині немає розділення на адресні і інформаційні лінії. У ній може бути, наприклад, 32 лінії і для адрес, і для даних. Спочатку ці лінії використовуються для адрес. Потім вони використовуються для даних. Щоб записати інформацію в пам'ять, потрібно спочатку передавати в пам'ять адреса, а потім дані. У випадку з окремими лініями адреси і дані можуть передаватися разом. Об'єднання ліній скорочує ширину і вартість шини, але система працює при цьому повільніше. Тому розробникам доводиться зважувати все за і проти, перш ніж зробити вибір.