- •Мови, рівні і віртуальні машини

- •Сучасні багаторівневі машини

- •Поняття архітектури пк

- •1.4. Розвиток комп’ютерної архітектури

- •Розвиток багаторівневих машин

- •Типи сучасних еом

- •Питання до лекції

- •2.1. Принципи розробки сучасних комп'ютерів

- •2.2. Паралелізм на рівні команд

- •2.3. Конвеєри

- •2.4. Суперскалярні архітектури

- •2.5. Паралелізм на рівні процесорів

- •2.6. Векторні комп'ютери

- •Блок управління

- •2.7. Мультипроцессори

- •2.8. Мультикомпьютери

- •Питання до лекції

- •3. Основи комп’ютерної організації : пам’ять

- •3.1. Ієрархічна структура пам'яті

- •3.2. Загальні відомості про пам'ять

- •3.4. Методи звертання до пам'яті

- •3.5. Модулі пам'яті

- •3.6. Ряди і банки пам'яті

- •3.8. Код з виправленням помилок

- •3. 9. Скільки потрібно пам'яті

- •Питання до лекції

- •4. Цифровий рівень побудови ом

- •4.1. Вентилі і булева алгебра

- •4.2. Булева алгебра

- •4.3. Реалізація булевих функцій

- •4.4. Еквівалентність схем

- •Основні цифрові логічні схеми Інтегральні схеми

- •4.5. Комбінаційні схеми

- •3 Входи і 8 виходів

- •4.6. Арифметичні схеми.

- •4.7. Тактові генератори

- •Питання до лекції

- •Цифровий рівень побудови ом.

- •5. Цифровий логічний рівень архітектури: пам’ять, мікропроцесори

- •5.2. Синхронні sr-защіпки

- •5.3. Синхронні d-защіпки

- •5.4. Тригери (flip-flops)

- •5.5. Регістри

- •5.6. Організація пам'яті

- •Тригер (б)

- •Кожний ряд представляє одне з 3-бітних слів. При операції зчитування і запису завжди зчитується або записується ціле слово

- •5.7. Мікросхеми пам'яті

- •5.9. Мікросхеми процесорів

- •Стрілочки указують вхідні і вихідні сигнали. Короткі діагональні лінії вказують на наявність декількох висновків.

- •Питання до лекції

- •6. Шини

- •6.1. Ширина шини

- •6.2. Синхронізація шини

- •6.3. Синхронні шини

- •6.5. Асинхронні шини

- •6.6. Арбітраж шини

- •6.7. Принципи роботи шини

- •Питання до лекції

- •7. Мікроархітектурний рівень

- •7.1. Приклад мікроархітектури

- •7.2. Тракт даних

- •В цьому розділі

- •Табліця 7.1. Деякі комбінації сигналів аллу і відповідні їм функції

- •7.3. Синхронізація тракту даних

- •7.4. Робота пам'яті.

- •7.5. Мікрокоманди

- •7.6. Управління мікрокомандами: Mic-1

- •7.7. Приклад архітектури команд: ijvm

- •7.8. Модель пам'яті ijvm

- •Питання до лекції

- •8. Рівень архітектури команд

- •8.1. Моделі пам'яті

- •8.2. Загальний огляд рівня архітектури команд

- •8.3. Властивості рівня команд

- •8.4. Регістри

- •8.5. Команди

- •8.6. Загальний огляд рівня команд машини Pentium II

- •8.8. Загальний огляд рівня команд системи ultrasparc II

- •8.9. Загальний огляд віртуальної машини Java

- •8.10. Типи даних

- •8.11. Числові типи даних

- •8.12. Нечислові типи даних

- •8.13. Типи даних процесора Pentium II

- •Підтримувані типи відмічені хрестом (х)

- •8.14. Типи даних машини UltraSparc II

- •8.16. Типи даних віртуальної машини Java

- •8.17. Формати команд

- •Питання до лекції

- •9. Адресація

- •9.1. Способи адресації

- •9.2. Безпосередня адресація

- •9.3. Пряма адресація

- •9.4. Регістрова адресація

- •9.5. Непряма регістрова адресація

- •Лістинг 9.1 - Програма на асемблері для обрахунку суми елементів масиву.

- •9.6. Індексна адресація

- •Листинг 9.2. Програма на мові асемблера для обчислення операції або від (Аі і Ві ) для масиву з 1024 елементів.

- •9.7. Відносна індексна адресація

- •9.8. Стекова адресація

- •9.9. Зворотній польський запис

- •9.10. Обчислення формул в зворотнім польськім записі

- •Питання до лекції

Питання до лекції

Защіпки

Синхронні SR-защіпки

Схема синхронної SR-защіпки

Синхронні D-защіпки

Схема синхронної D-защіпки

Тригери (flip-flops)

Генератор імпульсу та його часова діаграма для чотирьох точок на схемі

Схема D-тригера

Регістри

схема з двома D-тригерами із сигналами попередньої установки й очищення

Організація пам'яті

Мікросхеми пам'яті

ОЗП

ПЗП

Мікросхеми процесорів

6. Шини

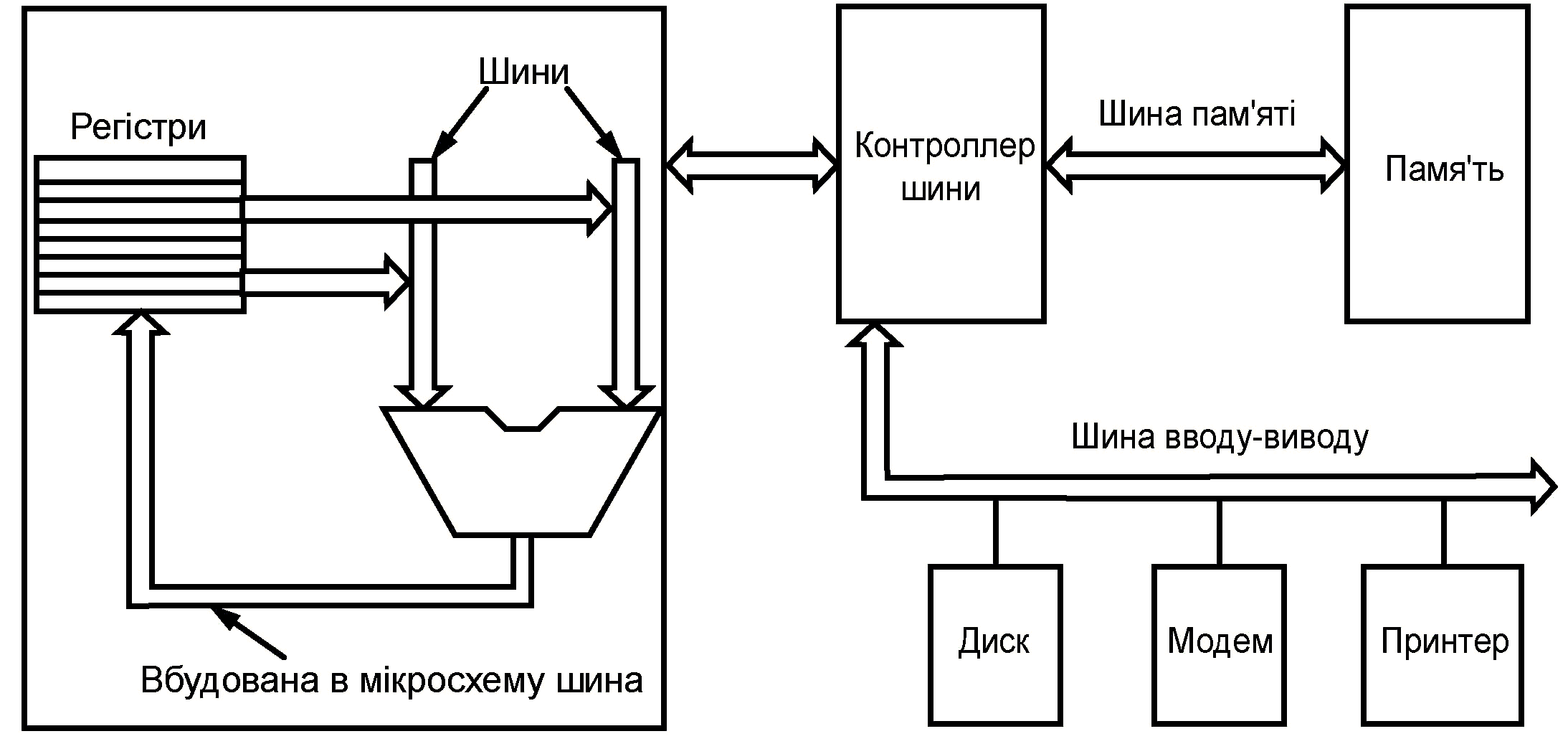

Шина - це група провідників, що сполучають різні пристрої, Шини можна розділити на групи відповідно до виконуваних функцій. Вони можуть бути внутрішніми по відношенню до процесора і служити для передачі даних в АЛУ і з АЛУ, а можуть бути зовнішніми по відношенню до процесора і пов'язувати процесор з пам'яттю або пристроями вводу-виводу. Кожен тип шини володіє певними властивостями, і до кожного з них пред'являються певні вимоги. У цьому і наступних розділах ми зосередимося на шинах, які пов'язують центральний процесор з пам'яттю і пристроями вводу-виводу. У наступному розділі ми детально розглянемо внутрішні шини процесора.

Мікросхема процесора

Рис. 6.1 – Комп'ютерна система з декількома шинами

Перші персональні комп'ютери мали одну зовнішню шину, яка називалася системною шиною. Вона складалася з декількох мідних дротів (від 50 до 100), які вбудовувалися в материнську плату. На материнській платі знаходилися роз'єми на однакових відстанях один від одного для мікросхем пам'яті і пристроїв вводу-виводу, Сучасні персональні комп'ютери звичайно містять спеціальну шину між центральним процесором і пам'яттю і принаймні ще одну шину для пристроїв вводу-виводу. На рис. 6.1 зображена система з однією шиною пам'яті і однією шиною вводу-виводу.

У літературі шини звичайно зображаються у вигляді жирних стрілок, як показано на цьому малюнку. Різниця між жирною і нежирною стрілкою невелика, Коли всі біти одного типа, наприклад адресні або інформаційні, малюється звичайна стрілка. Коли включаються адресні лінії, лінії даних і управління, використовується жирна стрілка

Хоча розробники процесорів можуть використовувати будь-який тип шини для мікросхеми, повинні бути введені чіткі правила про те, як працює шина, і пристрої, пов'язані з шиною, повинен підкорятися тим правилам, щоб плати до системної шини. Ці правила називаються протоколом шини. Крім того, повинні існувати певні технічні вимоги, щоб плати від третіх виробників підходили до каркаса плати і мали роз'єми, відповідні материнській платі механічно і з погляду потужностей, синхронізації і т.д.

Існує ряд широко використовуваних в комп'ютерному світі шин. Приведемо декілька прикладів: Omnibus (PDP-8), Unibus (PDP-11), IBM PC (PC/XT), ISA (PC/AT), EISA (80386), MicroChannel (PC/2), PCI, SCSI (різні персональні комп'ютери і робочі станції), Nubus (Macintosh), Universal Serial Bus (сучасні персональні комп'ютери), FireWire (побутова техніка), VME (устаткування в кабінетах фізики) і Сатас (фізика високих енергій). Можливо, все стало б набагато простіше, якщо б всі шини, окрім однієї, зникли з поверхні Землі (або окрім двох). На жаль, стандартизація в цій області здається маловірогідною, і вже вкладено дуже багато засобів у всі ці несумісні системи.

Давайте почнемо з того, як працюють шини. Деякі пристрої, зв’язані з шиною, є активними і можуть ініціювати передачу інформації по шині, тоді як інші є пасивними і чекають запитів. Активний пристрій називається задаючим пристроєм, пасивне — підчиненим пристроєм. Коли центральний процесор вимагає від контроллера диска зчитати або записати блок інформації, центральний процесор діє як задаючий пристрій, а контроллер диска — як підлеглий пристрій. Контроллер диска може діяти як задаючий пристрій, коли він наказує пам'яті прийняти слова, які зчиталися з диска. Декілька типових комбінацій задаючого і підлеглого пристроїв указані в табл. 6.1. Пам'ять ні за яких обставин не може бути задаючим пристроєм.

Таблиця 6.1 – Приклади задаючих і підлеглих пристроїв

Задаючий пристрій |

Підлеглий пристрій |

Приклад |

Центральний процесор |

Пам'ять |

Виклик команд і даних |

Центральний процесор |

Пристрій вводу-виводу |

Ініціалізація передачі даних |

Центральний процесор |

Співпроцесор |

Передача команди від процесора до співпроцесора |

Пристрій вводу-виводу |

Пам'ять |

ПДП (прямий доступ до пам'яті) |

Співпроцесор |

Центральний процесор |

Виклик співпроцесором операндів з центрального процесора |

Двійкові сигнали, які видають пристрої комп'ютера, часто недостатньо інтенсивні, щоб активізувати шину, особливо якщо вона достатньо довга і якщо до неї приєднано багато пристроїв. З цієї причини більшість задаючих пристроїв шини звичайно пов'язана з нею через мікросхему, яка називається драйвером шини, що по суті є двійковим підсилювачем. Схожим чином більшість підлеглих пристроїв пов'язана з шиною приймачем шини. Для пристроїв, які можуть бути і задаючим, і підлеглим пристроєм, використовується приймач-передавач шини. Ці мікросхеми взаємодії з шиною часто є пристроями з трьома станами, що дає їм можливість від'єднуватися, коли вони не потрібні. Іноді вони підключаються через відкритий колектор, що дає схожий ефект. Коли одне або декілька пристроїв на відкритому колекторі вимагають доступу до шини в один і той же час, результатом є булева операція АБО над всіма цими сигналами. Така угода називається монтажним АБО. У більшості шин одні лінії є пристроями з трьома станами, а інші, яким потрібна властивість монтажного АБО, — відкритим колектором.

Як і процесор, шина має адресні лінії, інформаційні лінії і лінії управління. Проте між виведеннями процесора і сигналами шини може і немає взаємно однозначної відповідності. Наприклад, деякі процесори містять три висновки, які видають сигнал читання з пам'яті або запису в пам'ять, або читання пристрою вводу-виводу, або запису на пристрій вводу-виводу, або який-небудь іншої операції. Звичайна шина може містити одну лінію для читання з пам'яті, другу лінію для запису в пам'ять, третю - для читання пристрою вводу-виводу, четвертую - для запису на пристрій вводу-виводу і т.д. Мікросхема-декодер повинна тоді пов'язувати даний процесор з такою шиною, щоб перетворювати 3-бітовий кодований сигнал в окремі сигнали, які можуть управляти лініями шини.

Розробка шин і принципи дії шин — це достатньо складні питання, і із цього приводу написаний ряд книг [128,135,136]. Принциповими питаннями в розробці є ширина шини, синхронізація шини, арбітраж шини і функціонування шини. Всі ці параметри істотно впливають на швидкість і пропускну спроможність шини. У наступних чотирьох розділах ми розглянемо кожний з них .