- •Мови, рівні і віртуальні машини

- •Сучасні багаторівневі машини

- •Поняття архітектури пк

- •1.4. Розвиток комп’ютерної архітектури

- •Розвиток багаторівневих машин

- •Типи сучасних еом

- •Питання до лекції

- •2.1. Принципи розробки сучасних комп'ютерів

- •2.2. Паралелізм на рівні команд

- •2.3. Конвеєри

- •2.4. Суперскалярні архітектури

- •2.5. Паралелізм на рівні процесорів

- •2.6. Векторні комп'ютери

- •Блок управління

- •2.7. Мультипроцессори

- •2.8. Мультикомпьютери

- •Питання до лекції

- •3. Основи комп’ютерної організації : пам’ять

- •3.1. Ієрархічна структура пам'яті

- •3.2. Загальні відомості про пам'ять

- •3.4. Методи звертання до пам'яті

- •3.5. Модулі пам'яті

- •3.6. Ряди і банки пам'яті

- •3.8. Код з виправленням помилок

- •3. 9. Скільки потрібно пам'яті

- •Питання до лекції

- •4. Цифровий рівень побудови ом

- •4.1. Вентилі і булева алгебра

- •4.2. Булева алгебра

- •4.3. Реалізація булевих функцій

- •4.4. Еквівалентність схем

- •Основні цифрові логічні схеми Інтегральні схеми

- •4.5. Комбінаційні схеми

- •3 Входи і 8 виходів

- •4.6. Арифметичні схеми.

- •4.7. Тактові генератори

- •Питання до лекції

- •Цифровий рівень побудови ом.

- •5. Цифровий логічний рівень архітектури: пам’ять, мікропроцесори

- •5.2. Синхронні sr-защіпки

- •5.3. Синхронні d-защіпки

- •5.4. Тригери (flip-flops)

- •5.5. Регістри

- •5.6. Організація пам'яті

- •Тригер (б)

- •Кожний ряд представляє одне з 3-бітних слів. При операції зчитування і запису завжди зчитується або записується ціле слово

- •5.7. Мікросхеми пам'яті

- •5.9. Мікросхеми процесорів

- •Стрілочки указують вхідні і вихідні сигнали. Короткі діагональні лінії вказують на наявність декількох висновків.

- •Питання до лекції

- •6. Шини

- •6.1. Ширина шини

- •6.2. Синхронізація шини

- •6.3. Синхронні шини

- •6.5. Асинхронні шини

- •6.6. Арбітраж шини

- •6.7. Принципи роботи шини

- •Питання до лекції

- •7. Мікроархітектурний рівень

- •7.1. Приклад мікроархітектури

- •7.2. Тракт даних

- •В цьому розділі

- •Табліця 7.1. Деякі комбінації сигналів аллу і відповідні їм функції

- •7.3. Синхронізація тракту даних

- •7.4. Робота пам'яті.

- •7.5. Мікрокоманди

- •7.6. Управління мікрокомандами: Mic-1

- •7.7. Приклад архітектури команд: ijvm

- •7.8. Модель пам'яті ijvm

- •Питання до лекції

- •8. Рівень архітектури команд

- •8.1. Моделі пам'яті

- •8.2. Загальний огляд рівня архітектури команд

- •8.3. Властивості рівня команд

- •8.4. Регістри

- •8.5. Команди

- •8.6. Загальний огляд рівня команд машини Pentium II

- •8.8. Загальний огляд рівня команд системи ultrasparc II

- •8.9. Загальний огляд віртуальної машини Java

- •8.10. Типи даних

- •8.11. Числові типи даних

- •8.12. Нечислові типи даних

- •8.13. Типи даних процесора Pentium II

- •Підтримувані типи відмічені хрестом (х)

- •8.14. Типи даних машини UltraSparc II

- •8.16. Типи даних віртуальної машини Java

- •8.17. Формати команд

- •Питання до лекції

- •9. Адресація

- •9.1. Способи адресації

- •9.2. Безпосередня адресація

- •9.3. Пряма адресація

- •9.4. Регістрова адресація

- •9.5. Непряма регістрова адресація

- •Лістинг 9.1 - Програма на асемблері для обрахунку суми елементів масиву.

- •9.6. Індексна адресація

- •Листинг 9.2. Програма на мові асемблера для обчислення операції або від (Аі і Ві ) для масиву з 1024 елементів.

- •9.7. Відносна індексна адресація

- •9.8. Стекова адресація

- •9.9. Зворотній польський запис

- •9.10. Обчислення формул в зворотнім польськім записі

- •Питання до лекції

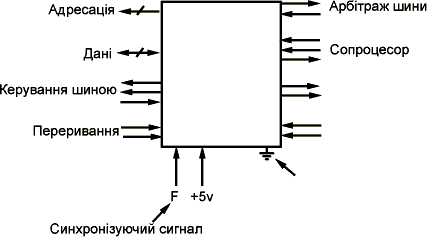

5.9. Мікросхеми процесорів

Усі сучасні процесори містяться на одній мікросхемі. Це робить цілком визначеним їхню взаємодію з іншими частинами системи. Кожна мікросхема процесора містить набір виходів, через які відбувається обмін інформацією з зовнішнім світом. Одні виходи передають сигнали від центрального процесора, інші приймають сигнали від інших компонентів, треті роблять і те й інше. Вивчивши функції усіх виводів, можна довідатися, як процесор взаємодіє з пам'яттю і пристроями вводу-виводу на цифровому логічному рівні.

Виводи мікросхеми центрального процесора можна підрозділити на три типи: адресні, інформаційні і керуючі. Ці виводи пов'язані з відповідними виводами на мікросхемах пам'яті і мікросхемах пристроїв вводу-виводу через набір паралельних проводів (так звану шину). Щоб викликати команду, центральний процесор спочатку посилає в пам'ять адресу цієї команди по адресних виводах. Потім він запускає одну або кілька ліній керування, щоб повідомити пам'яті, що йому потрібно, наприклад, прочитати слово. Пам'ять видає відповідь, розміщуючи необхідне слово на інформаційні виводи процесора і посилаючи сигнал про те, що це зроблено. Коли центральний процесор одержує даний сигнал, він приймає слово і виконує викликану команду.

Команда може вимагати читання або записи слів, що містять дані. У цьому випадку весь процес повторюється для кожного додаткового слова. Отже, центральний процесор обмінюється інформацією з пам'яттю і пристроями вводу-виводу, подаючи сигнали на виводи і приймаючи сигнали на входи. Іншого способу обміну інформацією не існує.

Кількість адресних виводів і кількість інформаційних виводів – два ключових параметри, що визначають продуктивність процесора. Мікросхема, що містить m адресних виводів, може звертатися до 2т комірок пам'яті. Звичайно m дорівнює 16, 20, 32 або 64. Мікросхема, що містить п інформаційних виводів, може зчитувати або записувати n-бітне слово за одну операцію. Звичайно п дорівнює 8, 16, 32, 36 або 64. Центральному процесорові з 8 інформаційними виводами потрібно 4 операції, щоб зчитати 32-бітне слово, тоді як процесор, що має 32 інформаційних виводів, може зробити ту ж роботу в одну операцію. Отже, мікросхема з 32 інформаційними виводами працює набагато швидше, але і коштує набагато дорожче.

Крім адресних і інформаційних виводів кожен процесор містить виводи керування. Виводи керування регулюють і синхронізують потік даних до процесора і від нього, а також виконують інші різноманітні функції. Усі процесори містять виводи для живлення (+3,3 В або +5 В), “землі” і синхронізуючого сигналу (меандру).

Виводи керування можна розділити на кілька основних категорій:

Керування шиною.

Переривання.

Арбітраж шини:

Стан.

Різне.

Схема типового центрального процесора, в якому використовуються ці типи сигналів, зображена на рис. 5.11.

Рис. 5.11 - Цоколівка типового центрального процесора.

Стрілочки указують вхідні і вихідні сигнали. Короткі діагональні лінії вказують на наявність декількох висновків.

Цоколівка – значення сигналів на різних виводах.

Виводи керування шиною у своїй більшості - це виходи з центрального процесора в шину (і отже, входи в мікросхеми пам'яті і мікросхеми пристроїв вводу-виводу). Вони повідомляють, що процесор хоче зчитати інформацію з пам'яті, або записати інформацію в пам'ять, або зробити що-небудь ще.

Виводи переривання – це входи з пристроїв вводу-виводу в процесор. У більшості систем процесор може дати сигнал пристрою вводу-виводу почати операцію, а потім приступити до якої-небудь іншої дії, поки пристрій вводу-виводу виконує свою роботу. Коли пристрій вводу-виводу закінчує свою роботу, контролер вводу-виводу посилає сигнал на один з виводів переривання, щоб перервати роботу процесора і змусити його обслуговувати пристрій вводу-виводу (наприклад, перевіряти помилки вводу-виводу). Деякі процесори містять вихідний вивід, щоб підтверджувати одержання сигналу переривання.

Виводи дозволу конфліктів у шині потрібні для того, щоб регулювати потік інформації в шині, тобто не допускати таких ситуацій, коли два пристрої намагаються скористатися шиною одночасно. З метою дозволу конфліктів центральний процесор вважається пристроєм.

Деякі центральні процесори можуть працювати з різними співпроцесорами (наприклад, із графічними процесорами, процесорами з плаваючою комою і т.ін.). Щоб забезпечити обмін інформації між процесором і співпроцесором, потрібні спеціальні виводи для передачі сигналів.

Крім цих виводів у деяких процесорах є різні додаткові виводи. Одні з них видають або приймають інформацію про стан, інші потрібні для перезавантаження комп'ютера, а треті – для забезпечення сумісності зі старими мікросхемами пристроїв вводу-виводу.