- •Мови, рівні і віртуальні машини

- •Сучасні багаторівневі машини

- •Поняття архітектури пк

- •1.4. Розвиток комп’ютерної архітектури

- •Розвиток багаторівневих машин

- •Типи сучасних еом

- •Питання до лекції

- •2.1. Принципи розробки сучасних комп'ютерів

- •2.2. Паралелізм на рівні команд

- •2.3. Конвеєри

- •2.4. Суперскалярні архітектури

- •2.5. Паралелізм на рівні процесорів

- •2.6. Векторні комп'ютери

- •Блок управління

- •2.7. Мультипроцессори

- •2.8. Мультикомпьютери

- •Питання до лекції

- •3. Основи комп’ютерної організації : пам’ять

- •3.1. Ієрархічна структура пам'яті

- •3.2. Загальні відомості про пам'ять

- •3.4. Методи звертання до пам'яті

- •3.5. Модулі пам'яті

- •3.6. Ряди і банки пам'яті

- •3.8. Код з виправленням помилок

- •3. 9. Скільки потрібно пам'яті

- •Питання до лекції

- •4. Цифровий рівень побудови ом

- •4.1. Вентилі і булева алгебра

- •4.2. Булева алгебра

- •4.3. Реалізація булевих функцій

- •4.4. Еквівалентність схем

- •Основні цифрові логічні схеми Інтегральні схеми

- •4.5. Комбінаційні схеми

- •3 Входи і 8 виходів

- •4.6. Арифметичні схеми.

- •4.7. Тактові генератори

- •Питання до лекції

- •Цифровий рівень побудови ом.

- •5. Цифровий логічний рівень архітектури: пам’ять, мікропроцесори

- •5.2. Синхронні sr-защіпки

- •5.3. Синхронні d-защіпки

- •5.4. Тригери (flip-flops)

- •5.5. Регістри

- •5.6. Організація пам'яті

- •Тригер (б)

- •Кожний ряд представляє одне з 3-бітних слів. При операції зчитування і запису завжди зчитується або записується ціле слово

- •5.7. Мікросхеми пам'яті

- •5.9. Мікросхеми процесорів

- •Стрілочки указують вхідні і вихідні сигнали. Короткі діагональні лінії вказують на наявність декількох висновків.

- •Питання до лекції

- •6. Шини

- •6.1. Ширина шини

- •6.2. Синхронізація шини

- •6.3. Синхронні шини

- •6.5. Асинхронні шини

- •6.6. Арбітраж шини

- •6.7. Принципи роботи шини

- •Питання до лекції

- •7. Мікроархітектурний рівень

- •7.1. Приклад мікроархітектури

- •7.2. Тракт даних

- •В цьому розділі

- •Табліця 7.1. Деякі комбінації сигналів аллу і відповідні їм функції

- •7.3. Синхронізація тракту даних

- •7.4. Робота пам'яті.

- •7.5. Мікрокоманди

- •7.6. Управління мікрокомандами: Mic-1

- •7.7. Приклад архітектури команд: ijvm

- •7.8. Модель пам'яті ijvm

- •Питання до лекції

- •8. Рівень архітектури команд

- •8.1. Моделі пам'яті

- •8.2. Загальний огляд рівня архітектури команд

- •8.3. Властивості рівня команд

- •8.4. Регістри

- •8.5. Команди

- •8.6. Загальний огляд рівня команд машини Pentium II

- •8.8. Загальний огляд рівня команд системи ultrasparc II

- •8.9. Загальний огляд віртуальної машини Java

- •8.10. Типи даних

- •8.11. Числові типи даних

- •8.12. Нечислові типи даних

- •8.13. Типи даних процесора Pentium II

- •Підтримувані типи відмічені хрестом (х)

- •8.14. Типи даних машини UltraSparc II

- •8.16. Типи даних віртуальної машини Java

- •8.17. Формати команд

- •Питання до лекції

- •9. Адресація

- •9.1. Способи адресації

- •9.2. Безпосередня адресація

- •9.3. Пряма адресація

- •9.4. Регістрова адресація

- •9.5. Непряма регістрова адресація

- •Лістинг 9.1 - Програма на асемблері для обрахунку суми елементів масиву.

- •9.6. Індексна адресація

- •Листинг 9.2. Програма на мові асемблера для обчислення операції або від (Аі і Ві ) для масиву з 1024 елементів.

- •9.7. Відносна індексна адресація

- •9.8. Стекова адресація

- •9.9. Зворотній польський запис

- •9.10. Обчислення формул в зворотнім польськім записі

- •Питання до лекції

Кожний ряд представляє одне з 3-бітних слів. При операції зчитування і запису завжди зчитується або записується ціле слово

в дію всі сигнали СК для обраного слова, завантажуючи вхідні дані в тригери для цього слова. Запис здійснюється тільки в тому випадку, якщо CS дорівнює 1, a RD дорівнює 0, при цьому записується тільки слово, обране адресами А0 і А1 інші слова не змінюються.

Процес зчитування подібний процесу запису. Декодування адреси відбувається аналогічно, як і при запису. Але в даному випадку лінія приймає значення 0, тому усі вентилі запису блокуються і жоден із тригерів не змінюється. Замість цього лінія вибору слів запускає вентилі І, що пов'язані з бітами Q обраного слова. Таким чином, обране слово передає свої дані в чотирьохвхідні вентилі АБО, розташовані в нижній частині схеми, а інші три слова видають 0. Отже, вихід вентилів АБО ідентичний значенню, збереженому в даному слові. Інші три слова ніяк не впливають на вихідні дані.

Розглянемо схему, в якій три вентилі АБО з'єднані із трьома лініями виводу даних. Але це викликає деякі проблеми. Вище було розглянуто лінії введення даних і лінії виводу даних як різні лінії. На практиці ж використовуються ті самі лінії. Отже, якщо зв'язати вентилі АБО з лініями виводу даних, мікросхема буде намагатися виводити дані (тобто задавати кожній лінії визначену величину) навіть у процесі запису, заважаючи нормальному введенню даних. З цієї причини бажано якимось чином з'єднувати вентилі АБО з лініями виводу даних при зчитуванні і цілком роз'єднувати їх при запису. Усе, що для цього потрібно, – електронний перемикач, що встановлює і руйнує зв'язок за кілька наносекунд.

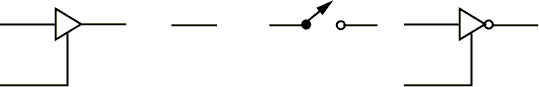

Такі перемикачі приведені на рис. 5.9. На рис. 5.9 а показане символічне зображення так званого буферного елемента без інверсії. Він містить вхід для даних, вихід для даних і вхід керування. Коли вхід керування дорівнює 1, буферний елемент працює як провідник (див. рис. 5.9 б). Коли вхід керування дорівнює 0, буферний елемент працює як розімкнутий ланцюг (див. рис. 5.9 в). З'єднання може бути відновлене за декілька наносекунд, якщо зробити сигнал керування рівним 1.

На рис. 5.9 г показаний буферний елемент з інверсією, що діє як звичайний інвертор, коли сигнал керування дорівнює 1, і відокремлює вихід від іншої частини схеми, коли сигнал керування дорівнює 0. Обоє буферних елемента являють собою пристрої з трьома станами, оскільки вони можуть видавати 0,1 або взагалі не видавати сигналу (у випадку з розімкнутого ланцюга). Буферні елементи, крім того, підсилюють сигнали, тому вони можуть справлятися з великою кількістю сигналів одночасно. Іноді вони використовуються в схемах саме з цієї причини, навіть якщо їхні властивості перемикача не потрібні.

Коли CS, RD і ОЕ дорівнюють 1, то сигнал дозволу видачі вихідних даних також дорівнює 1, у результаті чого запускаються буферні елементи і слово видається на вихідні лінії. Коли один із сигналів CS, RD і ОЕ дорівнює 0, виходи від'єднуються від іншої частини схеми.

а) б) в) г)

Рис. 5.9 - Буферний елемент без інверсії (а); дія буферного елемента без інверсії, коли сигнал керування дорівнює 1 (б); дія буферного елемента без інверсії, коли сигнал керування дорівнює 0 (в); буферний елемент з інверсією (г)

На

одних виводах

висока

напруга

викликає яку-небудь

дію,

на інших

– низька

напруга.

Щоб уникнути плутанини, термін “встановити

сигнал” вживається,

коли

викликається якась дія, замість того

щоб говорити, що напруга підвищується

або

знижується. Таким чином, для одних

виводів

установка

сигналу значить установку

на 1, а для інших – установку

на 0. Назви виводів,

що встановлюються на 0, містять

зверху риски. Сигнал CS установлюється

на 1, а сигнал

![]() – на 0. Протилежний термін – “скинути”.

– на 0. Протилежний термін – “скинути”.