- •Мови, рівні і віртуальні машини

- •Сучасні багаторівневі машини

- •Поняття архітектури пк

- •1.4. Розвиток комп’ютерної архітектури

- •Розвиток багаторівневих машин

- •Типи сучасних еом

- •Питання до лекції

- •2.1. Принципи розробки сучасних комп'ютерів

- •2.2. Паралелізм на рівні команд

- •2.3. Конвеєри

- •2.4. Суперскалярні архітектури

- •2.5. Паралелізм на рівні процесорів

- •2.6. Векторні комп'ютери

- •Блок управління

- •2.7. Мультипроцессори

- •2.8. Мультикомпьютери

- •Питання до лекції

- •3. Основи комп’ютерної організації : пам’ять

- •3.1. Ієрархічна структура пам'яті

- •3.2. Загальні відомості про пам'ять

- •3.4. Методи звертання до пам'яті

- •3.5. Модулі пам'яті

- •3.6. Ряди і банки пам'яті

- •3.8. Код з виправленням помилок

- •3. 9. Скільки потрібно пам'яті

- •Питання до лекції

- •4. Цифровий рівень побудови ом

- •4.1. Вентилі і булева алгебра

- •4.2. Булева алгебра

- •4.3. Реалізація булевих функцій

- •4.4. Еквівалентність схем

- •Основні цифрові логічні схеми Інтегральні схеми

- •4.5. Комбінаційні схеми

- •3 Входи і 8 виходів

- •4.6. Арифметичні схеми.

- •4.7. Тактові генератори

- •Питання до лекції

- •Цифровий рівень побудови ом.

- •5. Цифровий логічний рівень архітектури: пам’ять, мікропроцесори

- •5.2. Синхронні sr-защіпки

- •5.3. Синхронні d-защіпки

- •5.4. Тригери (flip-flops)

- •5.5. Регістри

- •5.6. Організація пам'яті

- •Тригер (б)

- •Кожний ряд представляє одне з 3-бітних слів. При операції зчитування і запису завжди зчитується або записується ціле слово

- •5.7. Мікросхеми пам'яті

- •5.9. Мікросхеми процесорів

- •Стрілочки указують вхідні і вихідні сигнали. Короткі діагональні лінії вказують на наявність декількох висновків.

- •Питання до лекції

- •6. Шини

- •6.1. Ширина шини

- •6.2. Синхронізація шини

- •6.3. Синхронні шини

- •6.5. Асинхронні шини

- •6.6. Арбітраж шини

- •6.7. Принципи роботи шини

- •Питання до лекції

- •7. Мікроархітектурний рівень

- •7.1. Приклад мікроархітектури

- •7.2. Тракт даних

- •В цьому розділі

- •Табліця 7.1. Деякі комбінації сигналів аллу і відповідні їм функції

- •7.3. Синхронізація тракту даних

- •7.4. Робота пам'яті.

- •7.5. Мікрокоманди

- •7.6. Управління мікрокомандами: Mic-1

- •7.7. Приклад архітектури команд: ijvm

- •7.8. Модель пам'яті ijvm

- •Питання до лекції

- •8. Рівень архітектури команд

- •8.1. Моделі пам'яті

- •8.2. Загальний огляд рівня архітектури команд

- •8.3. Властивості рівня команд

- •8.4. Регістри

- •8.5. Команди

- •8.6. Загальний огляд рівня команд машини Pentium II

- •8.8. Загальний огляд рівня команд системи ultrasparc II

- •8.9. Загальний огляд віртуальної машини Java

- •8.10. Типи даних

- •8.11. Числові типи даних

- •8.12. Нечислові типи даних

- •8.13. Типи даних процесора Pentium II

- •Підтримувані типи відмічені хрестом (х)

- •8.14. Типи даних машини UltraSparc II

- •8.16. Типи даних віртуальної машини Java

- •8.17. Формати команд

- •Питання до лекції

- •9. Адресація

- •9.1. Способи адресації

- •9.2. Безпосередня адресація

- •9.3. Пряма адресація

- •9.4. Регістрова адресація

- •9.5. Непряма регістрова адресація

- •Лістинг 9.1 - Програма на асемблері для обрахунку суми елементів масиву.

- •9.6. Індексна адресація

- •Листинг 9.2. Програма на мові асемблера для обчислення операції або від (Аі і Ві ) для масиву з 1024 елементів.

- •9.7. Відносна індексна адресація

- •9.8. Стекова адресація

- •9.9. Зворотній польський запис

- •9.10. Обчислення формул в зворотнім польськім записі

- •Питання до лекції

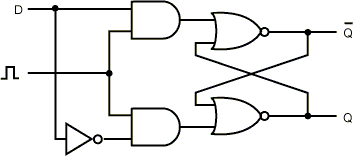

5.3. Синхронні d-защіпки

Щоб позбутися невизначеності SR-защіпки (невизначеність виникає у випадку, якщо S=R=1), потрібно запобігти появі подібної невизначеності. На рис. 5.3 зображена схема защіпки тільки з одним входом D. Так як вхідний сигнал у нижній вентиль І завжди є інверсним кодом вхідного сигналу у верхній вентиль І, ситуація, коли обидва входи рівні 1, ніколи не виникає. Коли D=l і синхронізуючий вхід дорівнює 1, защіпка переходить у стан Q=l. Коли D=0 і синхронізуючий вхід дорівнює 1, защіпка переходить у стан Q=0. Іншими словами, коли синхронізуючий вхід дорівнює 1, поточне значення D вилучається і зберігається в защіпці. Така схема називається синхронною D-защіпкою, і являє собою пам'ять об’ємом 1 біт. Значення, яке було збережено, завжди доступне на виході Q. Щоб завантажити в пам'ять поточне значення D, потрібно задати позитивний імпульс по лінії синхронізуючого сигналу.

Рис. 5.3 - Синхронна D – защіпка

Така схема вимагає наявності 11 транзисторів. Більш складні схеми можуть зберігати 1 біт, маючи всього 6 транзисторів.

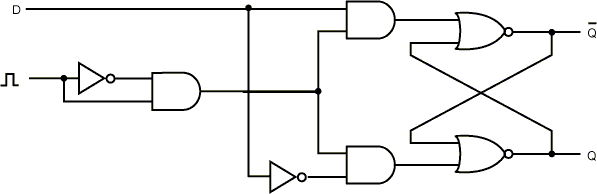

5.4. Тригери (flip-flops)

Багато схем вилучають значення на визначеній лінії у певний момент часу і запам'ятовують його. У такій схемі, що називається тригером, перехід стану відбувається не тоді, коли синхронізуючий сигнал дорівнює 1, а під час переходу синхронізуючого сигналу з 0 на 1 (наростаючий фронт) або з 1 на 0 (задній фронт). Отже, довжина синхронізуючого імпульсу не має значення, оскільки переходи відбуваються швидко.

Підкреслимо ще раз розходження між тригером і защіпкою. Тригер запускається фронтом сигналу, а защіпка запускається рівнем сигналу.

Існує кілька підходів до розробки тригерів. Наприклад, якби існував спосіб генерування дуже короткого імпульсу на наростаючому фронті синхронізуючого сигналу, цей імпульс можна було б подавати у D-защіпку. Такий спосіб існує. Відповідна схема показана на рис. 5.4 а.

а) б)

Рис. 5.4 - Генератор імпульсу (а); часова діаграма для чотирьох точок на схемі (б)

Може здатися, що вихід вентиля І завжди буде нульовим, оскільки функція І від будь-якого сигналу з його інверсією дає 0, але насправді ситуація більш тонка. При проходженні сигналу через інвертор відбувається невелика, але все-таки не нульова затримка. Дана схема працює саме завдяки цій затримці. Припустимо, що вимірюється напруга в чотирьох точках а, b, с і d. Вхідний сигнал у точці а являє собою довгий синхронізуючий імпульс (див. нижній графік на рис. 5.4 б. Сигнал у точці b показаний над ним. Відзначимо, що цей сигнал інвертований і подається з деякою затримкою. Час затримки залежить від типу інвертора і, як правило, складає кілька наносекунд.

Сигнал у точці с також подається із затримкою, але ця затримка зумовлена тільки часом проходження сигналу (зі швидкістю світла). Якщо фізична відстань між а і с, наприклад, 20 мікрон, тоді затримка на поширення сигналу складає 0,0001 нс, що, як правило, є незначною величиною у порівнянні із часом, що необхідний на проходження сигналу через інвертор. Таким чином, сигнал у точці с практично ідентичний сигналу в точці а.

Коли вхідні сигнали b і с піддаються операції І, у результаті виходить короткий імпульс, довжина якого (Δ) дорівнює вентильній затримці інвертора (як правило 5 нс і менше). Вихідний сигнал вентиля І – це даний імпульс, зміщений внаслідок затримку вентиля І (див. верхній графік на рис. 5.4 б. Це часове зміщення означає тільки те, що D-защіпка активізується із визначеною затримкою після наростаючого фронту синхронізуючого імпульсу. Він ніяк не впливає на довжину імпульсу. У пам'яті з часом циклу в 50 нс імпульс у 5 нс (який повідомляє, коли потрібно вибирати лінію D) досить короткий, і в цьому випадку повна схема може бути такою, яка зображена на рис. 5.5.

Рис. 5.5 - D-тригер

Стандартні зображення защіпок і тригерів показані на рис. 5.6. На рис. 5.6, а зображена защіпка, стан якої завантажується тоді, коли синхронізуючий сигнал СК (від слова clock) дорівнює 1, на противагу защіпці, зображеної на рис. 5.6 б, у якої синхронізуючий сигнал звичайно дорівнює 1, але переходить на 0, щоб завантажити стан з D. На рис. 5.6 в і г зображені тригери. Те, що це тригери, а не защіпки, показано за допомогою кутиків при синхронізуючому вході. Тригер на рис. 5.6 в змінює стан на наростаючому фронті синхронізуючого імпульсу (перехід від 1 до 0), тоді як тригер на рис. 5.6 г змінює стан на задньому фронті (перехід від 0 до 1). Більшість защіпок і тригерів також мають вихід , а в деяких є два додаткових входи: Set (установка) або Preset (попередня установка) і Reset (скидання) або Clear (очищення). Перший вхід (Set або Preset) установлює Q=1, а другий (Reset або Clear) – Q=0.