- •Мови, рівні і віртуальні машини

- •Сучасні багаторівневі машини

- •Поняття архітектури пк

- •1.4. Розвиток комп’ютерної архітектури

- •Розвиток багаторівневих машин

- •Типи сучасних еом

- •Питання до лекції

- •2.1. Принципи розробки сучасних комп'ютерів

- •2.2. Паралелізм на рівні команд

- •2.3. Конвеєри

- •2.4. Суперскалярні архітектури

- •2.5. Паралелізм на рівні процесорів

- •2.6. Векторні комп'ютери

- •Блок управління

- •2.7. Мультипроцессори

- •2.8. Мультикомпьютери

- •Питання до лекції

- •3. Основи комп’ютерної організації : пам’ять

- •3.1. Ієрархічна структура пам'яті

- •3.2. Загальні відомості про пам'ять

- •3.4. Методи звертання до пам'яті

- •3.5. Модулі пам'яті

- •3.6. Ряди і банки пам'яті

- •3.8. Код з виправленням помилок

- •3. 9. Скільки потрібно пам'яті

- •Питання до лекції

- •4. Цифровий рівень побудови ом

- •4.1. Вентилі і булева алгебра

- •4.2. Булева алгебра

- •4.3. Реалізація булевих функцій

- •4.4. Еквівалентність схем

- •Основні цифрові логічні схеми Інтегральні схеми

- •4.5. Комбінаційні схеми

- •3 Входи і 8 виходів

- •4.6. Арифметичні схеми.

- •4.7. Тактові генератори

- •Питання до лекції

- •Цифровий рівень побудови ом.

- •5. Цифровий логічний рівень архітектури: пам’ять, мікропроцесори

- •5.2. Синхронні sr-защіпки

- •5.3. Синхронні d-защіпки

- •5.4. Тригери (flip-flops)

- •5.5. Регістри

- •5.6. Організація пам'яті

- •Тригер (б)

- •Кожний ряд представляє одне з 3-бітних слів. При операції зчитування і запису завжди зчитується або записується ціле слово

- •5.7. Мікросхеми пам'яті

- •5.9. Мікросхеми процесорів

- •Стрілочки указують вхідні і вихідні сигнали. Короткі діагональні лінії вказують на наявність декількох висновків.

- •Питання до лекції

- •6. Шини

- •6.1. Ширина шини

- •6.2. Синхронізація шини

- •6.3. Синхронні шини

- •6.5. Асинхронні шини

- •6.6. Арбітраж шини

- •6.7. Принципи роботи шини

- •Питання до лекції

- •7. Мікроархітектурний рівень

- •7.1. Приклад мікроархітектури

- •7.2. Тракт даних

- •В цьому розділі

- •Табліця 7.1. Деякі комбінації сигналів аллу і відповідні їм функції

- •7.3. Синхронізація тракту даних

- •7.4. Робота пам'яті.

- •7.5. Мікрокоманди

- •7.6. Управління мікрокомандами: Mic-1

- •7.7. Приклад архітектури команд: ijvm

- •7.8. Модель пам'яті ijvm

- •Питання до лекції

- •8. Рівень архітектури команд

- •8.1. Моделі пам'яті

- •8.2. Загальний огляд рівня архітектури команд

- •8.3. Властивості рівня команд

- •8.4. Регістри

- •8.5. Команди

- •8.6. Загальний огляд рівня команд машини Pentium II

- •8.8. Загальний огляд рівня команд системи ultrasparc II

- •8.9. Загальний огляд віртуальної машини Java

- •8.10. Типи даних

- •8.11. Числові типи даних

- •8.12. Нечислові типи даних

- •8.13. Типи даних процесора Pentium II

- •Підтримувані типи відмічені хрестом (х)

- •8.14. Типи даних машини UltraSparc II

- •8.16. Типи даних віртуальної машини Java

- •8.17. Формати команд

- •Питання до лекції

- •9. Адресація

- •9.1. Способи адресації

- •9.2. Безпосередня адресація

- •9.3. Пряма адресація

- •9.4. Регістрова адресація

- •9.5. Непряма регістрова адресація

- •Лістинг 9.1 - Програма на асемблері для обрахунку суми елементів масиву.

- •9.6. Індексна адресація

- •Листинг 9.2. Програма на мові асемблера для обчислення операції або від (Аі і Ві ) для масиву з 1024 елементів.

- •9.7. Відносна індексна адресація

- •9.8. Стекова адресація

- •9.9. Зворотній польський запис

- •9.10. Обчислення формул в зворотнім польськім записі

- •Питання до лекції

5. Цифровий логічний рівень архітектури: пам’ять, мікропроцесори

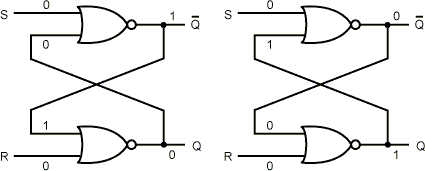

5.1. Защіпки

Щоб створити один біт пам'яті, необхідна схема, яка деяким чином “запам'ятовує” попередні вхідні значення. Таку схему можна сконструювати з двох вентилів НЕ-АБО, як показано на рис. 5,1, а. Аналогічні схеми можна побудувати з вентилів НЕ-І.

А |

В |

НЕ-АБО |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

а) б) в)

Рис. 5.1 - Защіпка НЕ-АБО в стані 0 (а); защіпка НЕ-АБО в стані 1 (б); таблиця істинності для функції НЕ-АБО (в)

Схема,

зображена на рис. 5.1 а,

називається

SR-защіпкою.

У

неї є два

входи: S (setting – установка)

і R (resetting – скидання). В ній є також два

комплементарних (додаткових) виходи: Q

і

![]() .

На відміну від комбінаційної схеми,

вихідні сигнали защіпки

не визначаються

поточними вхідними сигналами.

.

На відміну від комбінаційної схеми,

вихідні сигнали защіпки

не визначаються

поточними вхідними сигналами.

Розглянемо

приклад. Нехай, S=0

і R=0 (вони дорівнюють 0 більший час).

Припустимо також, що Q=0. Так як Q повертається

у верхній вентиль НЕ-АБО й обидва входи

цього вентиля дорівнюють 0, то його вихід

![]() дорівнює 1. Одиниця повертається в нижній

вентиль, у

якого в підсумку один

вхід дорівнює 0, а інший

– 1, а на виході виходить

Q=0 (рис. 5.1, а).

дорівнює 1. Одиниця повертається в нижній

вентиль, у

якого в підсумку один

вхід дорівнює 0, а інший

– 1, а на виході виходить

Q=0 (рис. 5.1, а).

Уявимо, що Q=l, a R і S усе ще дорівнюють 0. Верхній вентиль має входи 0 і 1 і вихід (тобто 0), що повертається в нижній вентиль. Така ситуація зображена на рис. 5.1 б. Стан, коли обидва виходи дорівнюють 0, неможливий, оскільки в цьому випадку обидва вентилі мали б на вході два нулі, що привело б до одиниці на виході, а не до нуля. Так само неможливо мати на обох виходах 1, оскільки це привело б до вхідних сигналів 0 і 1, що викликає на виході 0, а не 1. Висновок простий: при R=S=0 защіпка має два стабільних стани, які будемо називати 0 і 1 у залежності від Q.

Розглянемо дію вхідних сигналів на стан защіпки. Припустимо, що S приймає значення 1, у той час як Q=0. Тоді вхідні сигнали верхнього вентиля будуть 1 і 0, що приведе до вихідного сигналу =0. Ця зміна робить обидва входи в нижній вентиль рівними 0 і, отже, вихідний сигнал рівним 1. Таким чином, установка S на значення 1 переключає стан з 0 на 1. Установка R на значення 1, коли защіпка знаходиться в стані 0, не викликається змін, оскільки вихід нижнього вентиля НЕ-АБО дорівнює 0 і для входів 10, і для входів 11.

Використовуючи подібну аргументацію, доводиться, що установка S на значення 1 при стані защіпки 1 (тобто при Q=1) не викликає змін, але установка R на значення 1 приводить до зміни стану защіпки. Таким чином, якщо S приймає значення 1, то Q буде дорівнювати 1 незалежно від попереднього стану защіпки. Подібним чином перехід R на значення 1 викликає Q=0. Схема «запам'ятовує», який сигнал був останнім: S або R. Використовуючи цю властивість, можна конструювати комп'ютерну пам'ять.

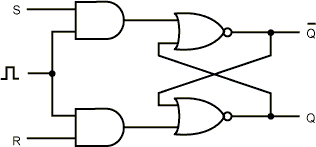

5.2. Синхронні sr-защіпки

Зручно зробити так, щоб защіпка змінювала свій стан тільки у визначені моменти. Щоб реалізувати це, шляхом модифікації основної схеми можна одержати синхронну SR-защіпку (рис. 5.2).

Ця схема має додатковий синхронізуючий вхід, який, як правило, дорівнює 0. Якщо цей вхід дорівнює 0, то обидва виходи вентилів І дорівнюють 0 незалежно від S і R, і защіпка не змінює стан. Коли значення синхронізуючого входу дорівнює 1, дія вентилів І зникає і стан защіпки стає залежним від S і R. Для позначення того факту, що синхронізуючий вхід дорівнює 1 (тобто стан схеми залежить від значень S і R), часто використовується термін стробувати.

Рис. 5.2 - Синхронна SR-защіпка

Якщо і R, і S повертаються до 0, схема стає недетермінованою. Єдиний можливий стан при S=R=1 – це Q= =0, але як тільки обидва входи повертаються до 0, защіпка повинна перейти в один із двох стабільних станів. Якщо один із входів приймає значення 0 раніше за інший, той що залишився в стані 1 “перемагає”, внаслідок того, що коли один із входів дорівнює 1, він керує станом защіпки. Якщо обидва входи переходять до 0 одночасно (що малоймовірно), защіпка переходить в один зі своїх станів випадково.