- •Мови, рівні і віртуальні машини

- •Сучасні багаторівневі машини

- •Поняття архітектури пк

- •1.4. Розвиток комп’ютерної архітектури

- •Розвиток багаторівневих машин

- •Типи сучасних еом

- •Питання до лекції

- •2.1. Принципи розробки сучасних комп'ютерів

- •2.2. Паралелізм на рівні команд

- •2.3. Конвеєри

- •2.4. Суперскалярні архітектури

- •2.5. Паралелізм на рівні процесорів

- •2.6. Векторні комп'ютери

- •Блок управління

- •2.7. Мультипроцессори

- •2.8. Мультикомпьютери

- •Питання до лекції

- •3. Основи комп’ютерної організації : пам’ять

- •3.1. Ієрархічна структура пам'яті

- •3.2. Загальні відомості про пам'ять

- •3.4. Методи звертання до пам'яті

- •3.5. Модулі пам'яті

- •3.6. Ряди і банки пам'яті

- •3.8. Код з виправленням помилок

- •3. 9. Скільки потрібно пам'яті

- •Питання до лекції

- •4. Цифровий рівень побудови ом

- •4.1. Вентилі і булева алгебра

- •4.2. Булева алгебра

- •4.3. Реалізація булевих функцій

- •4.4. Еквівалентність схем

- •Основні цифрові логічні схеми Інтегральні схеми

- •4.5. Комбінаційні схеми

- •3 Входи і 8 виходів

- •4.6. Арифметичні схеми.

- •4.7. Тактові генератори

- •Питання до лекції

- •Цифровий рівень побудови ом.

- •5. Цифровий логічний рівень архітектури: пам’ять, мікропроцесори

- •5.2. Синхронні sr-защіпки

- •5.3. Синхронні d-защіпки

- •5.4. Тригери (flip-flops)

- •5.5. Регістри

- •5.6. Організація пам'яті

- •Тригер (б)

- •Кожний ряд представляє одне з 3-бітних слів. При операції зчитування і запису завжди зчитується або записується ціле слово

- •5.7. Мікросхеми пам'яті

- •5.9. Мікросхеми процесорів

- •Стрілочки указують вхідні і вихідні сигнали. Короткі діагональні лінії вказують на наявність декількох висновків.

- •Питання до лекції

- •6. Шини

- •6.1. Ширина шини

- •6.2. Синхронізація шини

- •6.3. Синхронні шини

- •6.5. Асинхронні шини

- •6.6. Арбітраж шини

- •6.7. Принципи роботи шини

- •Питання до лекції

- •7. Мікроархітектурний рівень

- •7.1. Приклад мікроархітектури

- •7.2. Тракт даних

- •В цьому розділі

- •Табліця 7.1. Деякі комбінації сигналів аллу і відповідні їм функції

- •7.3. Синхронізація тракту даних

- •7.4. Робота пам'яті.

- •7.5. Мікрокоманди

- •7.6. Управління мікрокомандами: Mic-1

- •7.7. Приклад архітектури команд: ijvm

- •7.8. Модель пам'яті ijvm

- •Питання до лекції

- •8. Рівень архітектури команд

- •8.1. Моделі пам'яті

- •8.2. Загальний огляд рівня архітектури команд

- •8.3. Властивості рівня команд

- •8.4. Регістри

- •8.5. Команди

- •8.6. Загальний огляд рівня команд машини Pentium II

- •8.8. Загальний огляд рівня команд системи ultrasparc II

- •8.9. Загальний огляд віртуальної машини Java

- •8.10. Типи даних

- •8.11. Числові типи даних

- •8.12. Нечислові типи даних

- •8.13. Типи даних процесора Pentium II

- •Підтримувані типи відмічені хрестом (х)

- •8.14. Типи даних машини UltraSparc II

- •8.16. Типи даних віртуальної машини Java

- •8.17. Формати команд

- •Питання до лекції

- •9. Адресація

- •9.1. Способи адресації

- •9.2. Безпосередня адресація

- •9.3. Пряма адресація

- •9.4. Регістрова адресація

- •9.5. Непряма регістрова адресація

- •Лістинг 9.1 - Програма на асемблері для обрахунку суми елементів масиву.

- •9.6. Індексна адресація

- •Листинг 9.2. Програма на мові асемблера для обчислення операції або від (Аі і Ві ) для масиву з 1024 елементів.

- •9.7. Відносна індексна адресація

- •9.8. Стекова адресація

- •9.9. Зворотній польський запис

- •9.10. Обчислення формул в зворотнім польськім записі

- •Питання до лекції

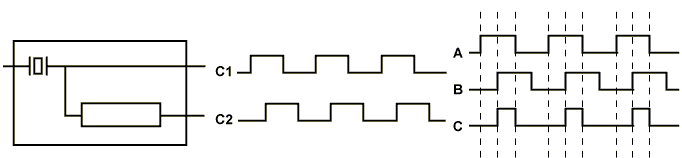

4.7. Тактові генератори

У багатьох цифрових схемах все залежить від порядку, в якому виконуються дії. Іноді одна дія повинна передувати іншій, іноді дві дії повинні відбуватися одночасно. Для контролю часових відносин у цифрові схеми вбудовуються тактові генератори, щоб забезпечити синхронізацію. Тактовий генератор – це схема, що викликає серію імпульсів. Всі імпульси однакові по тривалості. Інтервали між послідовними імпульсами також однакові. Часовий інтервал між початком одного імпульсу і початком наступних називається часом такту. Частота імпульсів звичайно від 1 до 500 Мгц, що відповідає часу такту від 1000 нс до 2 нс. Частота тактового генератора звичайно контролюється кварцовим генератором, щоб досягти високої точності.

У комп'ютері за час одного такту може відбутися багато подій. Якщо вони повинні здійснюватися у визначеному порядку, то такт варто розділити на підтакти. Щоб досягти кращого дозволу, ніж в основного тактового генератора, потрібно зробити відгалуження від задаючої лінії тактового генератора і вставити схему з визначеним часом затримки. У такий спосіб породжується вторинний сигнал тактового генератора, що зміщений по фазі щодо первинного (рис. 4.20 а). Часова діаграма (рис. 4.20 б) забезпечує чотири початки відліку часу для дискретних подій:

Наростаючий фронт С1.

Задній фронт С1.

Наростаючий фронт С2.

Задній фронт С2.

Зв'язавши різні події з різними фронтами, можна досягти необхідної послідовності виконання дій. Якщо в межах одного такту потрібно більш чотирьох початків відліку, можна зробити ще кілька відгалужень від задаючої лінії з різним часом затримки.

а) б) в)

Рис. 4.20 - Тактовий генератор (а); часова діаграма для тактового генератора (б); породження асинхронних тактових імпульсів (в)

У

деяких схемах важливі часові

інтервали, а не дискретні моменти часу.

Наприклад, деяка

подія

може відбуватися

в будь-який час, коли

рівень імпульсу С1

високий, а не на наростаючому фронті.

Інша

подія

може

відбуватися

тільки в тому випадку, коли

рівень імпульсу С2

високий. Якщо

необхідно більш двох інтервалів, потрібно

забезпечити більше

ліній передачі

синхронізуючих імпульсів або

зробити так, щоб стани

з

високим рівнем імпульсу в

двох тактових генераторів частково

перетиналися в часі.

В останньому випадку можна виділити 4

окремих інтервали:![]() І

І

![]() ,

С1 І С2, С1 І

,

І

.

,

С1 І С2, С1 І

,

І

.

Тактові генератори можуть бути синхронними. У цьому випадку час стану з високим рівнем імпульсу дорівнює часу стану з низьким рівнем імпульсу (рис. 4.20, б). Щоб одержати асинхронну серію імпульсів, потрібно змістити сигнал задаючого генератора, використовуючи ланку затримки. Потім потрібно з'єднати отриманий сигнал з початковим сигналом за допомогою логічної функції І (рис. 4.20 в, сигнал С).

Питання до лекції

Цифровий рівень побудови ом.

Що таке вентиль та які вентилі ви знаєте?

Інвертори

Булева алгебра

Схема функції більшості від трьох змінних

Реалізація булевих функцій

Еквівалентність схем

Основні цифрові логічні схеми

Інтегральні схеми

Мікросхема МІС, що містить 4 вентилі

Комбінаційні схеми

Мультиплексори.

Декодери.

Компаратори

Програмувальні логічні матриці

Арифметичні схеми

Схема зсуву

Суматори

Арифметико-логічні пристрої

Тактові генератори