- •Мови, рівні і віртуальні машини

- •Сучасні багаторівневі машини

- •Поняття архітектури пк

- •1.4. Розвиток комп’ютерної архітектури

- •Розвиток багаторівневих машин

- •Типи сучасних еом

- •Питання до лекції

- •2.1. Принципи розробки сучасних комп'ютерів

- •2.2. Паралелізм на рівні команд

- •2.3. Конвеєри

- •2.4. Суперскалярні архітектури

- •2.5. Паралелізм на рівні процесорів

- •2.6. Векторні комп'ютери

- •Блок управління

- •2.7. Мультипроцессори

- •2.8. Мультикомпьютери

- •Питання до лекції

- •3. Основи комп’ютерної організації : пам’ять

- •3.1. Ієрархічна структура пам'яті

- •3.2. Загальні відомості про пам'ять

- •3.4. Методи звертання до пам'яті

- •3.5. Модулі пам'яті

- •3.6. Ряди і банки пам'яті

- •3.8. Код з виправленням помилок

- •3. 9. Скільки потрібно пам'яті

- •Питання до лекції

- •4. Цифровий рівень побудови ом

- •4.1. Вентилі і булева алгебра

- •4.2. Булева алгебра

- •4.3. Реалізація булевих функцій

- •4.4. Еквівалентність схем

- •Основні цифрові логічні схеми Інтегральні схеми

- •4.5. Комбінаційні схеми

- •3 Входи і 8 виходів

- •4.6. Арифметичні схеми.

- •4.7. Тактові генератори

- •Питання до лекції

- •Цифровий рівень побудови ом.

- •5. Цифровий логічний рівень архітектури: пам’ять, мікропроцесори

- •5.2. Синхронні sr-защіпки

- •5.3. Синхронні d-защіпки

- •5.4. Тригери (flip-flops)

- •5.5. Регістри

- •5.6. Організація пам'яті

- •Тригер (б)

- •Кожний ряд представляє одне з 3-бітних слів. При операції зчитування і запису завжди зчитується або записується ціле слово

- •5.7. Мікросхеми пам'яті

- •5.9. Мікросхеми процесорів

- •Стрілочки указують вхідні і вихідні сигнали. Короткі діагональні лінії вказують на наявність декількох висновків.

- •Питання до лекції

- •6. Шини

- •6.1. Ширина шини

- •6.2. Синхронізація шини

- •6.3. Синхронні шини

- •6.5. Асинхронні шини

- •6.6. Арбітраж шини

- •6.7. Принципи роботи шини

- •Питання до лекції

- •7. Мікроархітектурний рівень

- •7.1. Приклад мікроархітектури

- •7.2. Тракт даних

- •В цьому розділі

- •Табліця 7.1. Деякі комбінації сигналів аллу і відповідні їм функції

- •7.3. Синхронізація тракту даних

- •7.4. Робота пам'яті.

- •7.5. Мікрокоманди

- •7.6. Управління мікрокомандами: Mic-1

- •7.7. Приклад архітектури команд: ijvm

- •7.8. Модель пам'яті ijvm

- •Питання до лекції

- •8. Рівень архітектури команд

- •8.1. Моделі пам'яті

- •8.2. Загальний огляд рівня архітектури команд

- •8.3. Властивості рівня команд

- •8.4. Регістри

- •8.5. Команди

- •8.6. Загальний огляд рівня команд машини Pentium II

- •8.8. Загальний огляд рівня команд системи ultrasparc II

- •8.9. Загальний огляд віртуальної машини Java

- •8.10. Типи даних

- •8.11. Числові типи даних

- •8.12. Нечислові типи даних

- •8.13. Типи даних процесора Pentium II

- •Підтримувані типи відмічені хрестом (х)

- •8.14. Типи даних машини UltraSparc II

- •8.16. Типи даних віртуальної машини Java

- •8.17. Формати команд

- •Питання до лекції

- •9. Адресація

- •9.1. Способи адресації

- •9.2. Безпосередня адресація

- •9.3. Пряма адресація

- •9.4. Регістрова адресація

- •9.5. Непряма регістрова адресація

- •Лістинг 9.1 - Програма на асемблері для обрахунку суми елементів масиву.

- •9.6. Індексна адресація

- •Листинг 9.2. Програма на мові асемблера для обчислення операції або від (Аі і Ві ) для масиву з 1024 елементів.

- •9.7. Відносна індексна адресація

- •9.8. Стекова адресація

- •9.9. Зворотній польський запис

- •9.10. Обчислення формул в зворотнім польськім записі

- •Питання до лекції

3 Входи і 8 виходів

вони не рівні. Схема ґрунтується на вентилі ВИКЛЮЧНЕ АБО, що видає 0, якщо сигнали на вході рівні, і 1, якщо сигнали на вході не рівні. Якщо всі чотири вхідних слова рівні, усі чотири вентилі ВИКЛЮЧНЕ АБО повинні видавати 0. Ці чотири сигнали потім надходять у вентиль АБО. Якщо в результаті виходить 0, отже, слова, що надійшли на вхід, рівні; у противному випадку вони не рівні. У нашому прикладі використовувався вентиль АБО як кінцева стадія, щоб поміняти значення отриманого результату: 1 означає рівність, а 0 – нерівність.

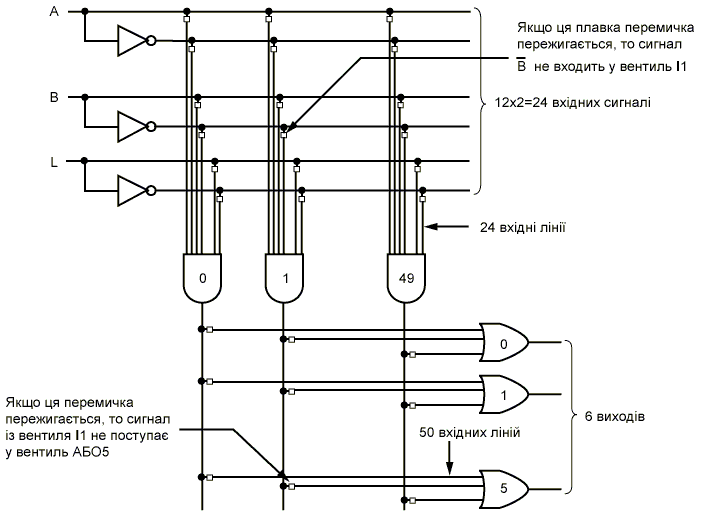

Програмувальні логічні матриці. Будь-яку функцію (таблицю істинності) можна представити у вигляді суми добутків і, отже, втілити у схеми, використовуючи вентилі І і АБО. Для обчислення сум добутків служить так звана програмувальна логічна матриця (рис. 4.14). Ця мікросхема містить входи для 12 змінних. Додаткові сигнали (інверсії) генеруються всередині самої мікросхеми. У підсумку усього виходить 24 вхідних сигналів. Який саме вхідний сигнал надходить у визначений вентиль І, визначається за матрицею 24x50 біт. Кожна з вхідних ліній до 50 вентилів І містить плавку перемичку. При випуску з заводу всі 1200 перемичок залишаються недоторканими. Щоб запрограмувати матрицю, покупець випалює обрані перемички, прикладаючи до схеми високу напругу.

Мал 4.13 - Простий чотирьохрозрядний компаратор

Вихідна частина схеми складається із шести вентилів АБО, кожний з яких містить до 50 входів, що відповідає наявності 50 виходів у вентилів І. Які з потенційно можливих зв'язків дійсно існують, залежить від того, як була запрограмована матриця 50x6. Мікросхема має 12 вхідних виводів, 6 вихідних виводів, живлення і «землю» (тобто всього 20 виводів).

Наведемо приклад використання програмувальної логічної матриці. Розглянемо схему, зображену на рис. 4.3 б. Вона містить три входи, чотири вентилі І, один вентиль АБО і три інвертори. Якщо запрограмувати матрицю певним чином, вона зможе обчислювати ту ж функцію, використовуючи три з 12 входів, чотири з 50 вентилів І і один з 6 вентилів АБО. (Чотири вентилі І повинні обчислювати BC, A C, AB і ABC; вентиль АБО приймає ці 4 добутки в якості вхідних даних.) Можна зробити так, щоб та ж програмувальна логічна матриця обчислювала одночасно суму чотирьох функцій однакової складності. Для простих функцій обмежуючим фактором є кількість вхідних змінних, для більш складних – вентилі І і АБО.

Матриці, програмувальні в умовах експлуатації, усе ще використовуються. Однак перевага віддається матрицям, що виготовляються на замовлення. Вони розробляються замовником і випускаються виробником відповідно до запитів замовника. Такі програмувальні логічні матриці набагато дешевші.

Рис. 4.14 - Програмувальна логічна матриця з 12 входами і 6 виходами. (Маленькі квадратики – плавкі перемички, що випалюються для завдання функції, яку потрібно обчислити. Плавкі перемички упорядковуються в двох матрицях. Верхня матриця – для вентилів І, а нижня матриця – для вентилів АБО)

Існує три різних способи втілення таблиці істинності, приведеної на рис. 4.3 а. Якщо в якості компонентів використовувати МІС, потрібно 4 мікросхеми. З іншого боку, можна обійтися одним мультиплексором, побудованим на СІС, як показано на рис. 4.11 б. Нарешті, можна використовувати лише четверту частину програмувальної логічної матриці. Очевидно, якщо необхідно обчислювати багато функцій, використання логічної матриці, що програмується більш ефективно, чим застосування двох інших методів. Для простих схем найкраще використовувати більш дешеві МІС і СІС.